Code No: **R17A0401**

### MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

### (Autonomous Institution – UGC, Govt. of India)

**II B.Tech I Semester Supplementary Examinations, April 2023**

**Electronic Devices and Circuits**

#### (EEE, ECE, CSE & IT)

### Time: 3 hours

2

#### Max. Marks: 70

R17

Note: This question paper Consists of 5 Sections. Answer FIVE Questions, Choosing ONE Question from each SECTION and each Question carries 14 marks.

# SECTION-I

- 1 A The reverse saturation current of a germanium diode is  $100\mu$ A at room [7M] temperature of  $27^{0}$  C. Calculate the current in forward biased condition, if forward bias voltage is 0.2V at room temperature. If temperature is increased by  $20^{0}$  C, calculate the reverse saturation current and the forward current for same forward voltage at new temperature

- **B** Explain the operation of Zener diode and explain how it act as voltage [7M] regulator in detail.

OR

- A(i) Compare Zener and Avalanche break downs[7M]

- (ii) Determine the value of forward current in the case of p-n junction silicon diode with  $I_0 = 10 \ \mu A$ ,  $V_f = 0.8V$ , T= 300 K.

- *B* Explain in detail about the forward and reverse biased conditions of p-n [7M] junction diode and also explain about the estimation of static and dynamic resistances.

# **SECTION-II**

- 3 A Derive the expression for the following parameters [7M] (i)I<sub>DC</sub> (ii) E<sub>DC</sub> (iii) I<sub>rms</sub> (iv) efficiency (v) ripple factor of a Full-wave-rectifier.

- **B** A 230 V, 50Hz voltage is applied to the primary of a 3:1 step down [7M] transformer used in a Half wave rectifier having a load of 10K $\Omega$ . If the diode resistance and the secondary coil resistance are 75  $\Omega$  and 10  $\Omega$ , determine maximum, average and RMS values of current, DC voltage across the load, efficiency, ripple factor.

### OR

- 4 A Derive the expression for the following parameters [6M]

(i)I<sub>DC</sub> (ii) E<sub>DC</sub> (iii) I<sub>rms</sub> (iv) efficiency (v) ripple factor of a Half Wave rectifier.

B A centre tapped full wave rectifier circuit the RMS half secondary voltage is

- **3** A centre tapped full wave rectifier circuit the RMS half secondary voltage is 9V assuming ideal diodes and load resistance  $R_L = 1K\Omega$ . Calculate

| y assuming root and roug resistance R <sub>L</sub> - Tree. Calculate |                  |      |  |  |

|----------------------------------------------------------------------|------------------|------|--|--|

| i)                                                                   | Peak Curent      | [2M] |  |  |

| ii)                                                                  | DC load Voltage  | [2M] |  |  |

| iii)                                                                 | I <sub>rms</sub> | [2M] |  |  |

| iv)                                                                  | ripple factor    | [2M] |  |  |

|                                                                      |                  |      |  |  |

## **SECTION-III**

| 5 | A                | For a certain transistor $I_C$ = 5.255mA, $I_B$ =100 $\mu A$ and $I_{CBO}$ = 5 $\mu A$                                         | [7M]          |

|---|------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|

|   |                  | (i) calculate $\alpha$ , $\beta$ and I <sub>E</sub> .                                                                          |               |

|   |                  | (ii) Detrmine the new level of $I_B$ required to make $I_C = 15 \text{ mA}$                                                    |               |

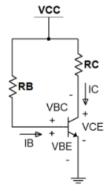

|   | B                | Explain in detail about the operation of Transistor in CB configuration with                                                   | [ <b>7M</b> ] |

|   |                  | suitable diagrams.                                                                                                             |               |

|   |                  | OR                                                                                                                             |               |

| 6 | A                | For a single-stage Transistor Amplifier, $R_S = 2 \text{ k}\Omega$ and $R_L = 5 \text{ k}\Omega$ . The <i>h</i> -              | [7M]          |

|   |                  | parameter values are $h_{\rm fb} = 0.98$ , $h_{\rm ib} = 21\Omega$ , $h_{\rm rb} = 2.9 \times 10^{-4}$ and $h_{\rm ob} = 0.49$ |               |

|   |                  | $\mu$ A/V. Find A <sub>I</sub> , A <sub>V</sub> , R <sub>i</sub> and R <sub>o</sub> for CB transistor configuration            |               |

|   | B                | Differentiate CB, CE, CC configurations on indicating all parameters                                                           | [ <b>7</b> M] |

|   |                  | necessary and with suitable basic diagrams of configurations.                                                                  |               |

|   |                  | SECTION-IV                                                                                                                     |               |

| 7 | $\boldsymbol{A}$ | Define biasing? Draw the Self bias circuit and obtain the expression for the                                                   | [7M]          |

- 7 A Define biasing? Draw the Self bias circuit and obtain the expression for the [7M] stability factor?

- B

For circuit shown is subjected to temperature change ; and the value of  $\beta = 100$  at  $25^{0}$  C and  $\beta = 125$  at  $75^{0}$  C determine the percentage change in the Q-point values over the temperature range .

## OR

| 8  | $\boldsymbol{A}$ | What is the need for biasing and explain the DC and AC load line analysis     | [ <b>7</b> M] |

|----|------------------|-------------------------------------------------------------------------------|---------------|

|    |                  | for Q- point identification                                                   |               |

|    | B                | Design a collector to base bias circuit using silicon transistor to achieve a | [7M]          |

|    |                  | stability factor of 20, with the following specifications:                    |               |

|    |                  | $V_{CC} = 16V, V_{BE} = 0.7V, V_{CEQ} = 8V, Icq=4ma \& \beta=50$              |               |

|    |                  | SECTION-V                                                                     |               |

| 9  | $\boldsymbol{A}$ | Explain the construction and operation of JFET with its characteristics and   | [ <b>7</b> M] |

|    |                  | explain the different regions in VI characteristics?                          |               |

|    | B                | Analyze the operation of FET with fixed bias and derive the values of Input   | [ <b>7</b> M] |

|    |                  | impedance, output impedance, voltage gain.                                    |               |

|    |                  |                                                                               |               |

|    |                  | OR                                                                            |               |

| 10 | $\boldsymbol{A}$ | Explain the construction & operation of a n-channel MOSFET in                 | [ <b>7</b> M] |

|    |                  | enhancement and depletion modes with the help of static drain characteristics |               |

|    |                  | and transfer characteristics?                                                 |               |

|    | B                | Compare BJT and FET and list our their advantages and disadvantages.          | [7M]          |

[7M]