**MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY**

Autonomous Institution – UGC, Govt. of India

# **Department of COMPUTATIONAL INTELLIGENCE**

# CSE (AI&ML)

## **B.TECH (R-22 Regulation)**

(II YEAR - I SEM)

# 2024-25

# COMPUTER ORGANIZATION AND ARCHITECTURE

(R22A1261)

# **LECTURE NOTES**

#### MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12(B) of UGC ACT 1956

(Affiliated to JNTUH, Hyderabad, Approved by AICTE-Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified) Maisammaguda, Dhulapally (Post Via. Hakimpet), Secunderabad–500100, Telangana State, India

# Department of COMPUTATIONAL INTELLIGENCE CSE (ARTIFICIAL INTELLIGENCE & MACHINE LEARNING)

# COMPUTER ORGANIZATION AND ARCHITECTURE (R22A1261)

# **LECTURE NOTES**

### SK. Subhani

Assistant Professor

#### Department of Computational Intelligence CSE (Artificial Intelligence and Machine Learning), Artificial Intelligence and Machine Learning

#### Vision

To be a premier centre for academic excellence and research through innovative interdisciplinary collaborations and making significant contributions to the community, organizations, and society as a whole.

#### Mission

- To impart cutting-edge Artificial Intelligence technology in accordance with industry norms.

- To instill in students a desire to conduct research in order to tackle challenging technical problems for industry.

- To develop effective graduates who are responsible for their professional growth, leadership qualities and are committed to lifelong learning.

#### **QUALITY POLICY**

- To provide sophisticated technical infrastructure and to inspire students to reach their full potential.

- To provide students with a solid academic and research environment for a comprehensive learning experience.

- To provide research development, consulting, testing, and customized training to satisfy specific industrial demands, thereby encouraging self-employment and entrepreneurship among students.

For more information: www.mrcet.ac.in

#### MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY DEPARTMENT OF COMPUTATIONAL INTELLIGENCE

II Year B.Tech. CSE(AIML)- I Sem

L/T/P/C 3/-/-/3

#### (R22A1261) COMPUTER ORGANIZATION AND ARCHITECTURE

#### **OBJECTIVES:**

The students will be able to:

- 1. To understand the working of a Computer System and its basic principles.

- 2. To learn the architecture and design of 8086 processor.

- 3. To know the concepts of Memory and corresponding technologies.

- 4. To understand the functional aspects of various peripheral devices.

- 5. To acquire knowledge about parallel processors.

#### UNIT - I:

**Functional blocks of a computer**: CPU, memory, input-output subsystems, control unit. Computer Organization and Architecture - Von Neumann

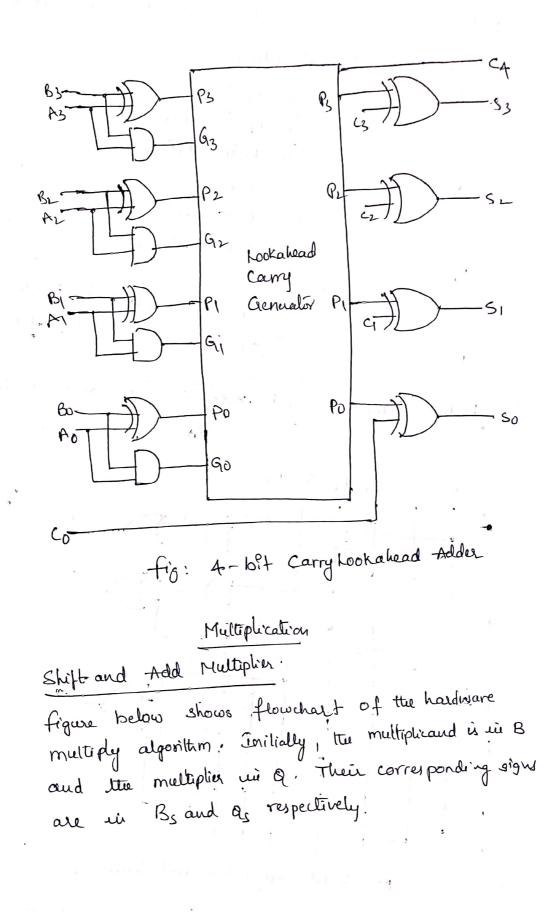

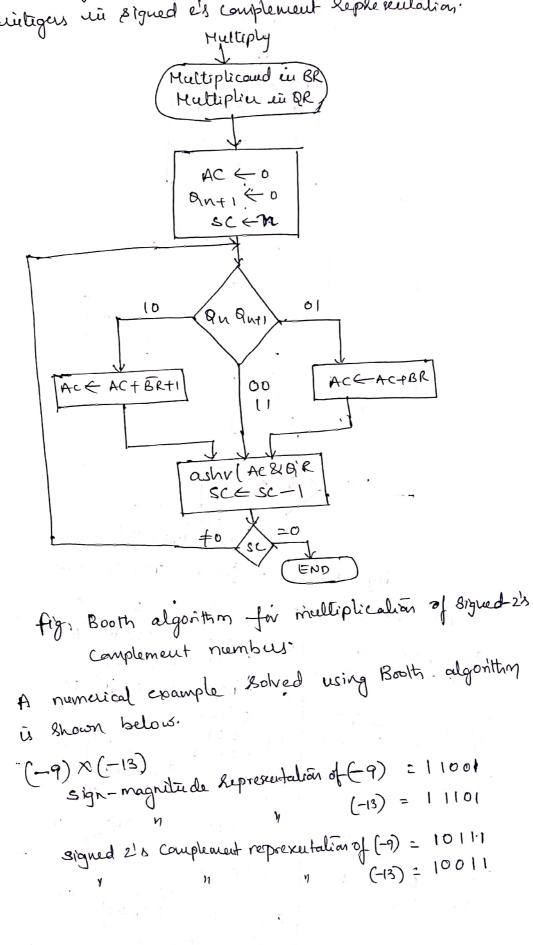

**Data representation**: signed number representation, fixed and floating-point Representations, Character representation. Computer arithmetic – integer addition and Subtraction, Ripple carry adder, carry look-ahead adder, etc. Multiplication – shift-and add, Booth multiplier.

#### UNIT – II:

**Introduction** to x86 architecture.

**Instruction set architecture** of a CPU: Registers, instruction execution cycle, RTL Interpretation of instructions, addressing modes, instruction set.

CPU Control unit design: Micro-programmed design approach.

#### UNIT – III:

**Memory system design**: Semiconductor memory technologies, memory organization. **Memory organization:** Memory interleaving, concept of hierarchical memory organization, Cache memory, cache size vs. block size, mapping functions, Replacement algorithms, write policies.

#### UNIT – IV:

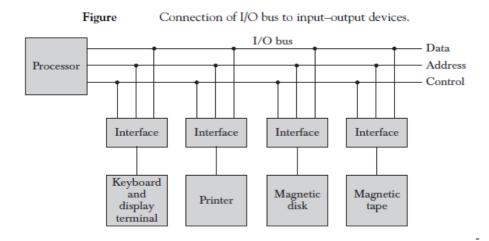

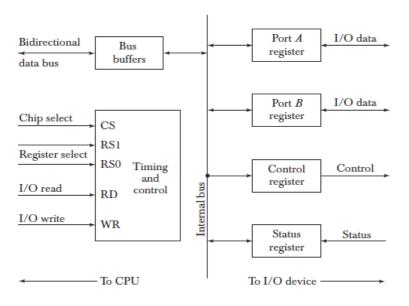

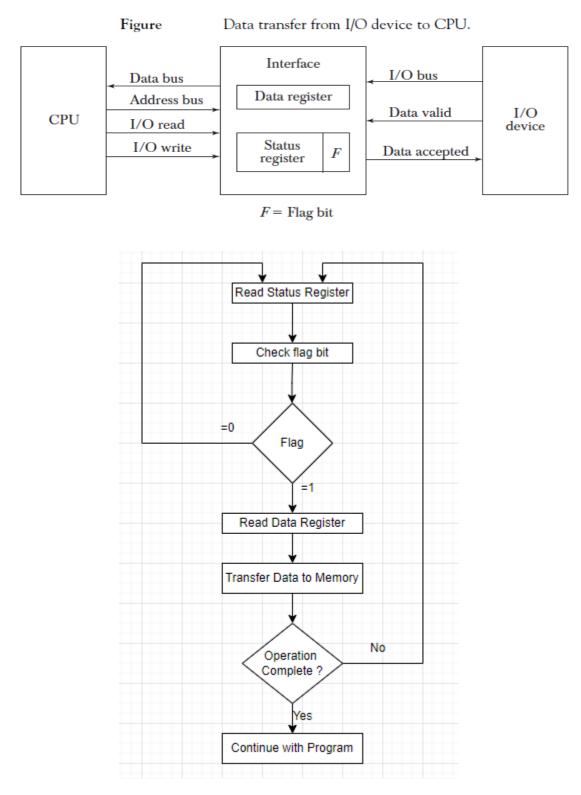

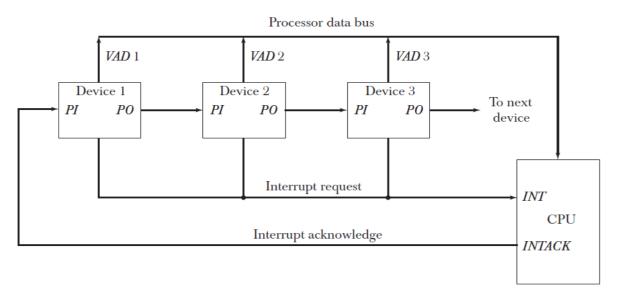

**Peripheral devices and their characteristics**: Input-output subsystems, I/O device interface, I/O transfers – program controlled, interrupt driven and DMA, privileged and non-privileged instructions, software interrupts and exceptions. Programs and processes – role of interrupts in process state transitions.

#### UNIT – V:

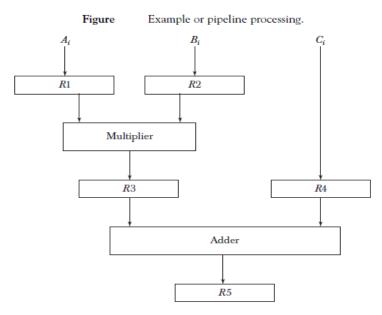

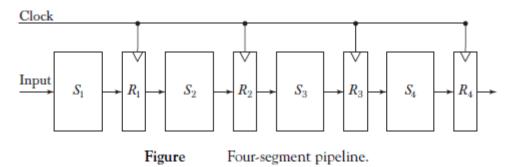

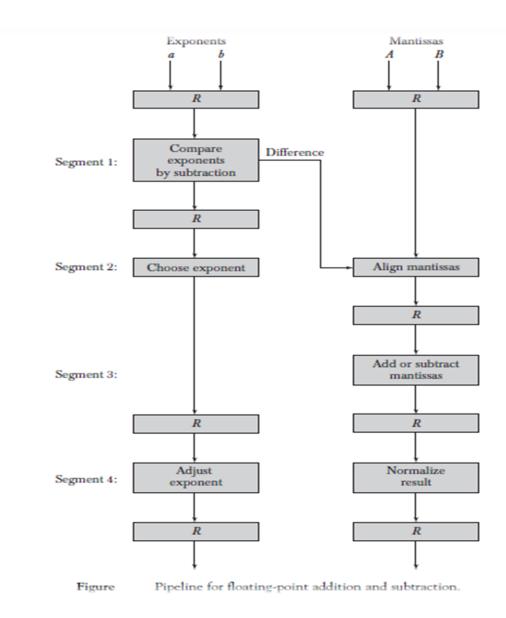

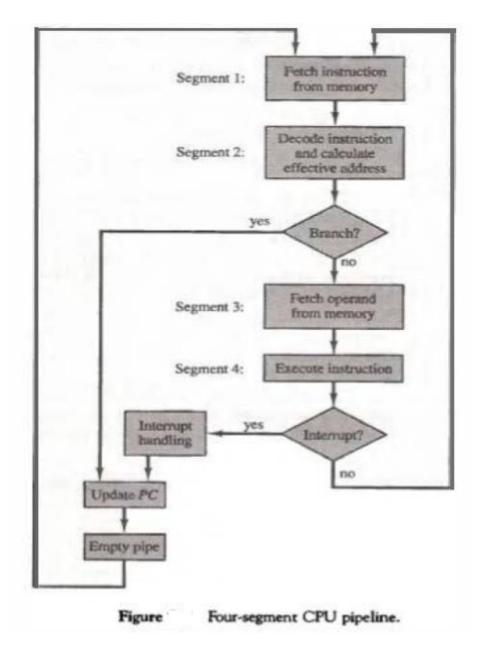

**Pipelining:** Basic concepts of pipelining, throughput and speedup, pipeline hazards. **Parallel Processors:** Introduction to parallel processors, Concurrent access to memory and cache coherency.

#### **TEXT BOOKS:**

- 1."Computer System Architecture", 3rd Edition by M.Morris Mano, Pearson.

- 2. "Computer Organization and Design: The Hardware/Software Interface", 5th Edition by David A. Patterson and John L. Hennessy, Elsevier.

3."Computer Organization and Embedded Systems", 6th Edition by Carl Hamacher, McGraw Hill Higher Education.

#### **REFERENCE BOOKS:**

#### **Course Outcomes:**

#### At the end of the course, Students will be able to:

1. Illustrate the functional block diagram of a single bus architecture of a computer.

- 2. Analyze the various instruction sets and addressing modes.

- 3. Design a memory module and analyze its operation by interfacing with the CPU for a specific architecture.

- 4. Compare and contrast the peripherals and the related I/O transfers

- 5. Assess the performance, and apply design techniques to enhance performance using pipelining & parallelism.

COA UNET-I (part-1)

Overview of Hiero computer structure and operations-Functional parts of the Herro Computer -The block diagram for a simple microcomputer. The major pasts are the central processing unit or CPU, memory and riput and output circuity or Ilo. Connecting these parts are three sets of parallel lines called buses. The three buses are the address bus, the data bus,

and the control bus.

Memory: - Hu menory section consists of a mixture of RAM and ROM: It may also have magnetic disk magnetic hard disks, or optical disks. Henny has two purposes. The first purpose is to store the. brang codes for the sequence of instructions you want the computer to carry out. The second purpose of the memory is to store the brany coded deta with which the computer is going to be worked. Input/output:- The input/output or 310 Section allows the computer to take data from the outside world or rend date to the outside world. Peripherals such as keyboards, Video display terminales, printers and modeurs are Cancelid to the 210 section. This allows The

user and computer to communicate with eacholing the best example for the imput devices is A/D output devices is A/D Output devices is DIA Converter and the best example for placements I/O porto 2- The actual physical devices and to rielenface the computer burns to epleaned Sydeen are often called ports. The post is simply a group of D-flipflops. OB: Data DB Bus CB: Control Bus 11P Central procensity cinit(CPV) CB Memory AB: Addrug (RAM and ROM) devices CB J/o Bus ports Gp devin fø: Block diagram of the Hicrocomputer A.B Central Processing Unit :- The Central processing unitare controls the operation of the computer. a microcomputer lui cpu is a microprocensir. In the CPU fetches benany coded Pretouctions from menny decodes the instructions into a series of simple actions and carries out there actions a sequence of ships. cui

The CPU also contains an address counter or histruction pointer register contech holds the address of address from next execulately histruction or date ileur to be felched from menny, general purpose registers, which are used for temporary storage of benavy dete and circevilaring which generalis the coultof bus Signals. Address Bus:- The address Bus consists of 16,20, dy or 32 parallel signal lines. On of these lines the CPU sends out the address of memory localism Ital is to be willen to a read from. The no. of menny localions that the CPU can address is deturined by the number of address lines. If the CPU has N address lines of can address 2N' memory localions. M'CPU with 16 addresslives cau addres 216 memory locations is, 65536 memory localión. A CPU with 20 address lines can address 220 i., 1,048,576 localions.

2

Data Bus :- The Data bus contrists of \$, 16 or 32 parallel signal lines. As midicalis by the double ended arrows on the data bus, the data bus lines are bedinchisted. This means that can read data from a part on these lines or it can send data ui from memory or from a port on these times, or it can send date, out to memory or from a post on these lines.

Many devices in a system will have their outputs connected to the detabus but only are device outputs connected to the detabus but only are device will have their offers connected to the date Krips its outputs enabled.

Control Bus !-

The carlood bus consists of 4 to 10 parallel signal lines. The CPU sends out Signals on the cartial bus to enable the olps of addressed memory devices or post devices. Typical control bus signals are Hemory Read, Hemory Write, Ilo Read and Slo Write.

To read a byte of data from a memory location the CPV kends out the memory addres of the destruct byte on the address bus and than sends out a Hemory Read signal on the could bus. the memory read signal arables the addressed memory derive to cutput a data word outo the databus

# Computer Organization and Architecture

Computer organization is concerned with the Structure and behaviour of a computer système as seen by the three. Organization deals with physical components (cércuit design, adders, signals & pripherals) Computer Architecture helps us to understand the functionalities of a system. A programmer courview alchitecture wither of entructions, addressing modes.

Von-Neumann Architecture :-

Von-Neumann Architecture follous Stored program organization. All modern computers are bared on a stored program concept withoduced by John Von Neumann. Th twis stored program cancept', programs and date are stored eix a separate storage unit called memories and are torated the same. This novel idea meant that a computer built with this addicted be much easier to reprogram.

# Data Representation:-

# Neamber Systems.

1. Decemal Number System 2. Binary Number System 3. Octal Number System 4. Hexa decemal Number System 5. Binary coded decimal Number System.

The bare (on radio of the benary no system is It consists of only two different digits of and i. Octar Kumber system 0001 1001 1010 1011 1100 1101 13 1110 14 undertousité main Maine 15 Fin Octal Number system:-The base (or) radix of octal no system is s'. It consists of 8 different digite '0' to 7'. 70 100 20 0 10 21 pt still 22 12 3 13 14 4 15 5 16 77 107 - -... 777 6 17 7 Herpa Decimal Number system the base (or) radio of hepadecinal no system is ils'. It consists of ils' different digits. O' to f' It is as shown below.

A 100 Ao 90 20 10 0 110100 21 11 22 12 2 23 13 3 24 14 4 25 15 5 26 16 G 27 17 7 28 18 8 29 19 9 2A IA A 2B IB B 20 IC C -- · FFF 20 ---. 9F AF ..... FF lof (D) D 20 IE E 24 IF Binary coded Decemal Number System:-In this no système decimal digits are coded este binary format. 9 0 8 7 (10) 1001 0000 1000 0101 (BLD) Every decimal digit has to be written to bit brang equivalent. Carvasians. Desimal to benany: -1001011 275 75(10) 237 -- [ 18-1 9-0 4-2 2-0 1-0 repeated devision with 2 and record the perform

4.5

remainders in the reverse order.

75.23 (10) 0.23×2: 0.46 .00111 0.46x2 2 0.92 0.9222 = 1.94 FS = 1001001 24 0.84x2 = 1.68 75.23 21001011,00111,21 0.68×2 = 1.36 > To carvert the fractional post into benary multiply the fractional port by 18 posted by 2' leave the integri part and meltiply the new feachional part by 2' and so on centil flactional part becomes zero or perform meltiplication by atleast '5' times, and recard the left over eiteger parts in forward order TO convert rieteger part Decimal to octal preform repeated division with respective radix and Decimal to Hepadecimal 8 or 16. And to Convert fearliand purt multiply if by 8 or 16 leose the integer part and continue the multiplication with maco fractional part. Exactly Same as Decimal to binary. Binary to Decimal :-2222 22 222 222 24  $\left[2^{3}\times1+2^{2}\times0+2^{1}\times1+2^{0}\times0\right]$ ,  $2^{-1}\times1+2^{-2}\times1+2^{-3}\times0$ [8+0+2+0].[0.5+0.250+0.0625] 10,8125,10, Octal to Decemal:-81 80 87 2 3 . 5 (8)  $[8 \times 2 + 1 \times 3] \cdot [5 \times 0.125] = 19 \cdot 625$ (10)

6 Herea Decimal to Decimal:-0  $16^{1} 16^{0} 16^{-1}$ A B · 4 (16) 16×A+1×B]. [0:0625×4] 171+2.5 = 173.510 Octal to Binary 437,26(8) Allocate 3' binary digits for each and every octal digit. Then we get benavy equivalent 100 011 111 . 010 \$10 Brhany to Octal '-10110110.10101 starting from binary point towards left side geoup 3' positions and assign octal equavalent stærting from binary point towards Right side geoup '3' positions and assign octal equivalent  $\begin{array}{c} 010 | 1 0 | 10 \\ 2 \\ 2 \\ 6 \\ 6 \\ 5 \\ 8 \\ 8 \\ \end{array}$ 266.52(8) Hexadecimal to Binary B2A, C16, Allocate 'i' binary digits for each and every a digit. Then we get binary equivalent 1011 0010 1010. 1100

Brang to Heradecemel :-0> 1011010110, 101101 Starting from Brany point towards leftside group \$ 7 positions and assign here decined equivalent. and starting from broany point lowends Right sigle group '4' positions and assign heradeemed equivalent. 0010/10 01/0110. 1011/0 1002 296.34,16, signed Integer Representation !-tre intgos care be represented es arly one format ie, Ston-magnitude form. -ve integers can be represented in adding 3 formats. 1. sign-magnitude form They are d. signed - 1's complement form 3. Signed 2's complement form. Represent 178 in sign-mag format: 0 00 magnitude sign Represent -7810, in Three different formalis 0 0 Sign-mag termet 0 0 Signed 1's comp 0 signed es lour

floating point Representation.

IEEE floating point notalion consiste of i, single precession floating point representation (32) i double "

(60) is extended "

(80)

0

Represent the given no -53.5,10, mi signelsign Single precession and double precession format

- 53.5(10) 0.5×221.0 2 27-1 2133-0 2113-1 116-1 216-1 Binary equippalent is  $-110111 \cdot 1 = (-1.10111) \times 2^{5}$ maulisse biard (23 bib) expansent Sign (1 bit) (8 bits) In single precision format as shown above I-bit is allocated for sign, 8 bits for biand exponent (bias value is 127 bib(2K-1-1) for Sigt single precision and 23 bils for the fractional put. The leading bit a i's not Stored (as it is always i for a normalized number) aud is referred as hidden bit

If we represent the same nember -53.5 Lie double precision format.

| 1              |                          | 1011/1 + 496 zeros | 1        |

|----------------|--------------------------|--------------------|----------|

| 1              | 10000000000              | maintursa          |          |

| Sign<br>Clibit | epponent<br>+) (11 bits) | CI' hidden t       | +<br>sit |

The bras value in double precision is 1023 1023 +5 = 1028.

1023

3/1028

So, bland exponent is 10000000100

2/514-0 2 257-0 -> In double precision format i bit is for sign i libils are 2/128-1 2764-0 for brand exponent and 32-0 2 '52' bits are allocated for wantissa 16-0 18-0 and i'hidden bit & prevent wi 24-0 2-0 maulista. 1-0

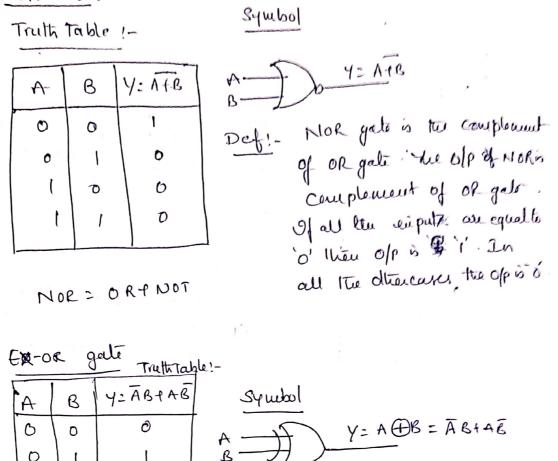

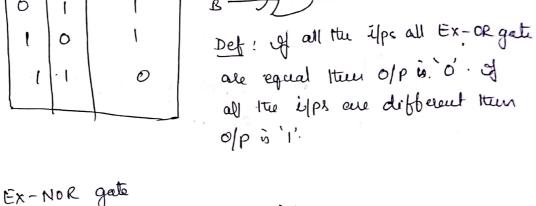

NOR Gale :-

ER-NOR = ER-OR PNOT. · 80 00 - 1.

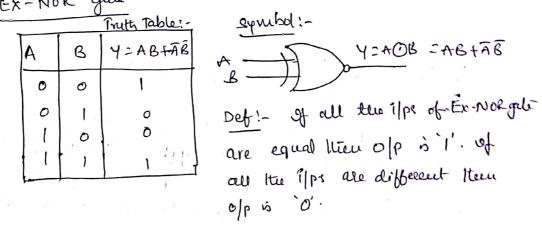

Combinational Circuits:-

2

Digital logic circuite are basically categorized into two lypes.

1. combinational circuits

a. Sequential circuits

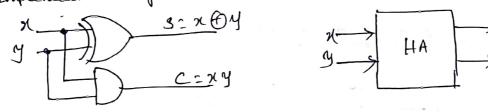

A combinational circuit is a connected arrangement of logic gates with a set of eights and outputs. At any given time, the brnary values of the outputs are a feenchion of the benavy combination of inputs. Half-Adder : Half-adder is a combenational circuit which adds two benary digets namely aregend and addend and produces the result as carry and sum. Boolean Expressions. Truthtable of HA  $C = \chi Y$ S.NO X S: 5. y+ 2. y 0 0 0 0. 0 1 0 1 1 0 0 1 = x(+)y

Black deageau of Half Addu Implementation of Half Adder

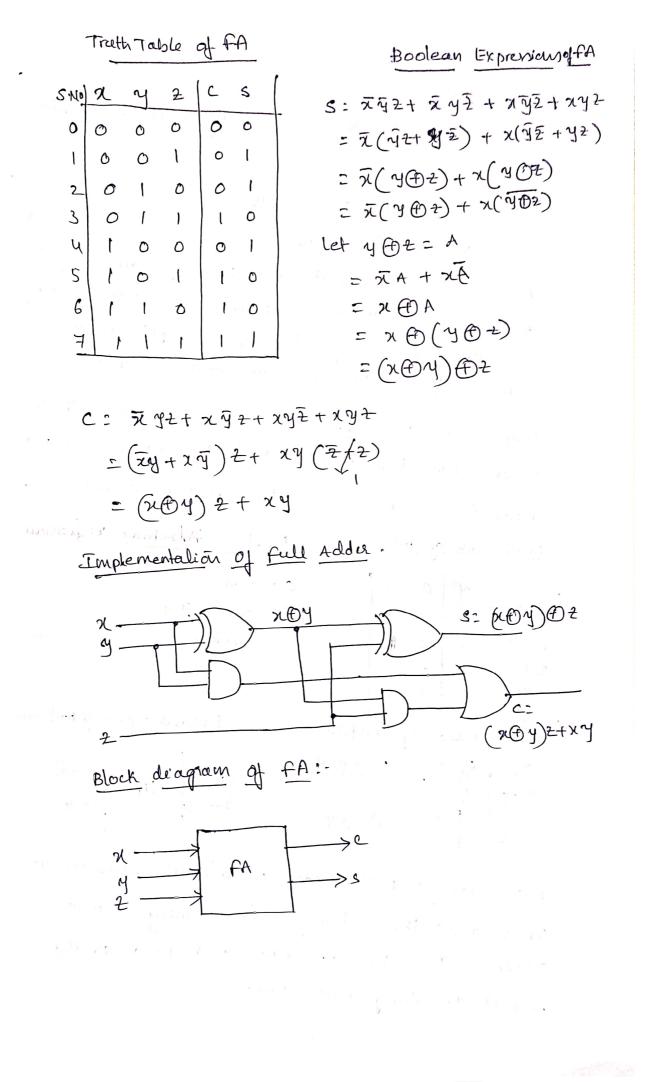

full-Adder : fall-Adder is a combination circuit which adds three binary digits namely augend, addened and previous cavry and produces the Result as carry and sum.

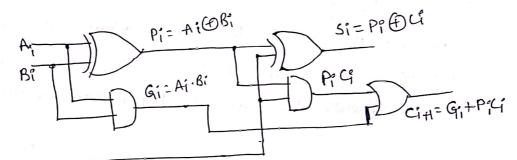

(3) Ripple carry Adder (or) Binary Parallel Addu A ripple carry adder is a digital circuit that produces the arithmetic sum of two brang numbers. It is a cascaded connection of fulladders. A 4-bit ripple carry adder is caricaded connection of 4 fell addese.

In ripple carry adder, in each section the Sum output is generaled only after the previous Carry is produced. These, the seem of the most Significant bit is available only after the carry signal has rippled through the adder from the least significant stage to the most significant stage. As a result, the final sum and carry bits Will be available after a considuable delay. Fig. below shows the 4-bet Ripple carry Adder

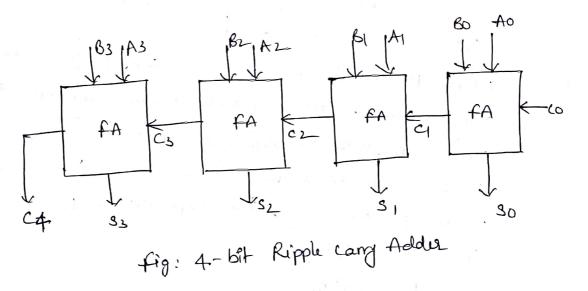

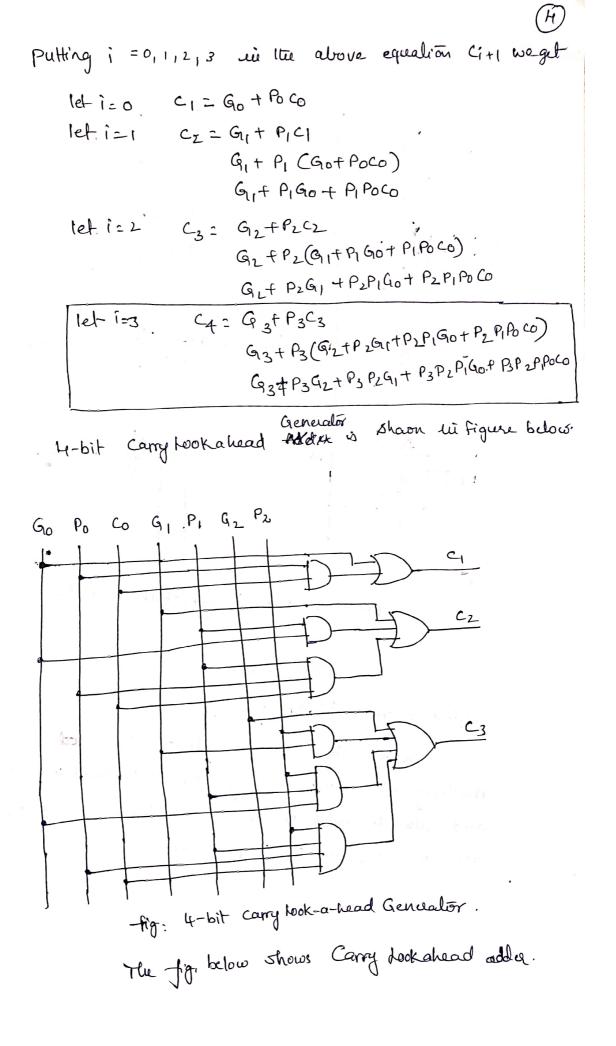

Carry Lookahead Adder:-The carry Lookahead Adder (CLA) Solves the carry delay problem by calculating the carry signals in advance, based on the input signals. It is based on the fact that carry signal will be generaled in two cases:

i) When both bits A; and B; are 'i',

a) when one of the two bits is i' and carry-in it 'i.

The above two conditions are designated in the below truth table.

Citien and Gi are called the camp propagate and cohere Pi and Gi are called the camp propagate and carry generate. The carry generate and carry propagate signals are used to calculate all the carries we advance. So, there is no need to wait for the carry to ripple through all the previous stages. The expressions for Pi, Gi, Si and Cite are as follows.

Scanned with OKEN Scanner

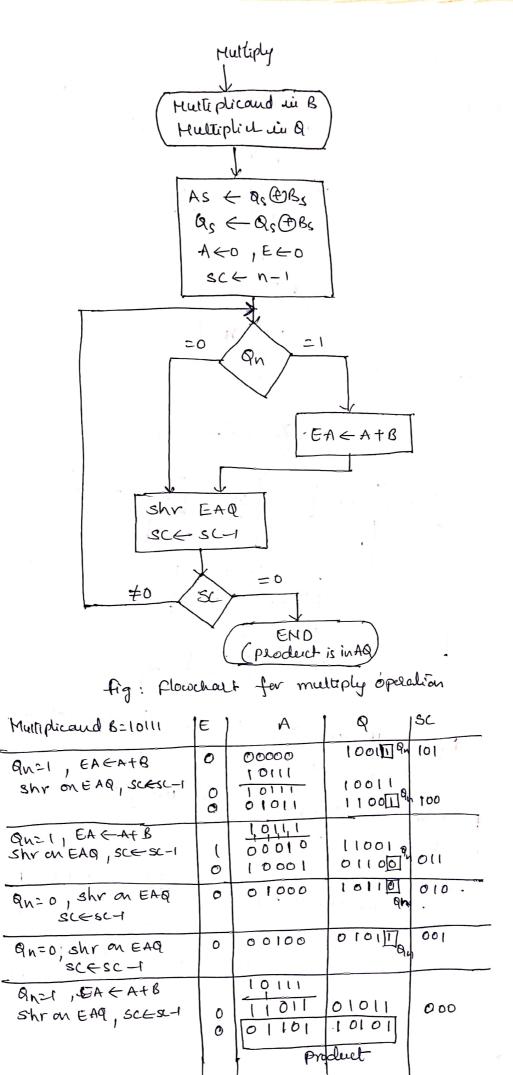

Multiplication Algorithm:-Booth Booth algorithm gives a procedure for multiplying binary rietigers in signed es complement Repherentation.

| Example of Multiplication with Booth Algorithm |                                      |                    |       |                  |      |  |  |

|------------------------------------------------|--------------------------------------|--------------------|-------|------------------|------|--|--|

| Qn Qn+1                                        | BR= 10111                            | AC                 | QR    | anti             | JC   |  |  |

|                                                | BR +1 = 01001                        | <b>60</b> 000      | 1001  | 0                | 101  |  |  |

|                                                | AC & ACTBRFI                         | 01001              |       |                  |      |  |  |

|                                                | ashron Acear<br>SCESC-1              | 01001              |       | n I              | 100  |  |  |

|                                                | ashr on Ac &QR                       | 00010              | 01100 | ۰ <sub>۱</sub> ۱ | 011  |  |  |

|                                                | sc€sc-                               | 10111              |       |                  |      |  |  |

| 01                                             | ACE ACTBR<br>ashron Aesar<br>SCESC-1 | 11001              |       | ٥                | 01 D |  |  |

|                                                | ashr on Acega                        | 11110              | 0101  | 0                | 00 I |  |  |

|                                                | SCESC-1<br>ACEACFBRTI                | 01001              | 01011 |                  |      |  |  |

|                                                | SCESC-I                              | VOOD II<br>Discard | 10101 |                  |      |  |  |

|                                                |                                      | J                  | 1     | 1.               | -    |  |  |

Addetion and Subtraction:-There are three ways of representing negative fixed. point benary numbers. .1. signed - magnitude 2 - signed - 1's complement

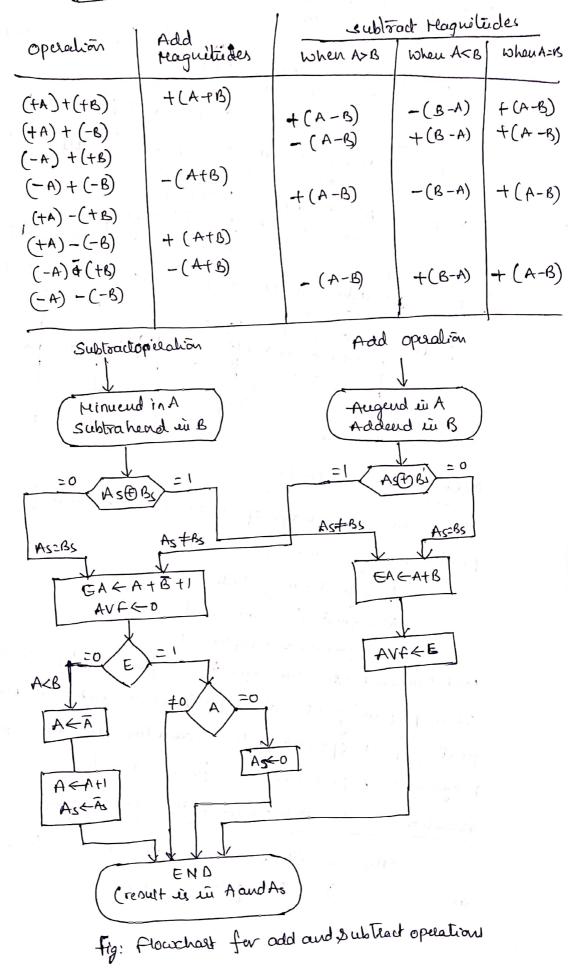

3 - signed -2's complement rost computer use the signed is complement representation Cohen performing eviltimetic operations with integers. for ploating point operations, most computers use the signedmagnitude representation for the mantisca. Addition and subtraction with signed-Magnitude Data: the algorithms for addition and subtraction are derived from the following table.

Addition and subtraction of Signed - Magnitude Data

🔘 🖉 Scanned with OKEN Scanner

UNTT-II Past-1

Syllabus:-

Introduction to X86 Architectur. Instruction set architecture of a CPU: Reguistion, Instruction execution cycle, RTL Interpretation of instructions, addressing Hoder, Instruction Let. CPU control Unit Design: Microplogrammed control wit. design approach.

I) Introduction to X86 Architecture:-

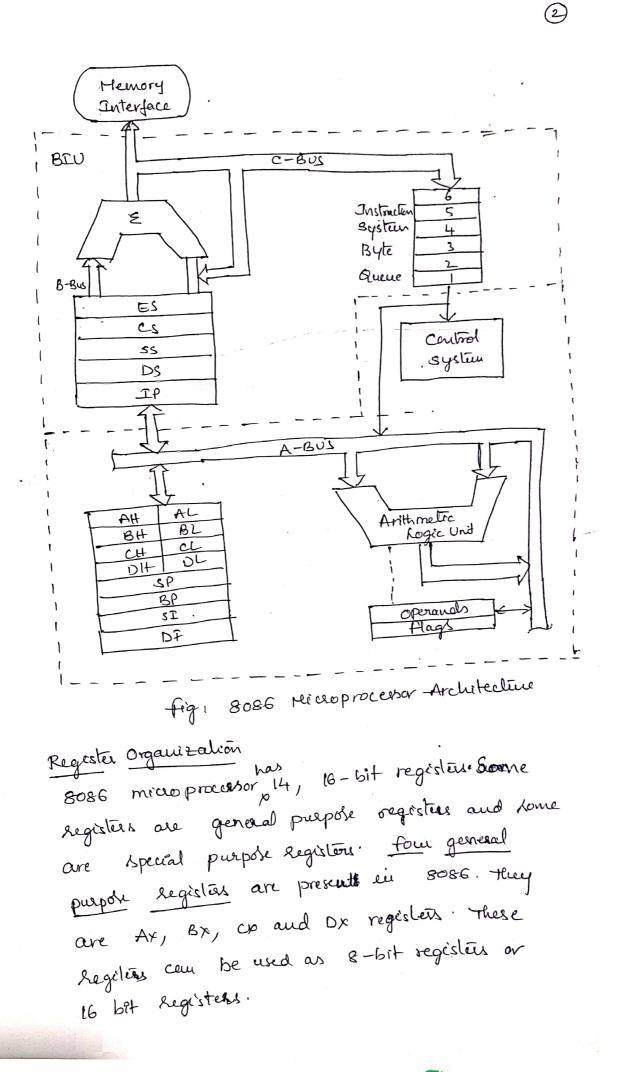

The figure below shows the 8086 mino processor architecture. The 8086 CPU is divided into two independent functional parts.

1. BUS Interface Unit (BIU)

2. Execution Unit (EU)

D'viding the work between these two and's speeds up processing

Bus vaterface unit (BIU): The BIU sends out addresses, fetches instructions from memory, reads data from ports and memory, writes data to poste and memory. In simple words, the BIU handles all transfers of data and addresses on the buses for the execution unit: Execution Unit (EU)!-

the EU of the 8086 tells the BIU where to

$\bigcirc$

fetzh eustmilian or data from, decodus intrations and execute instructions. The EU control contains Control system which derects all the distanced Operations. A decoder en la EU Bondales interdiens felched from memory with a begin of actions, which the EU carries out. The EU has 16-bit anothemetic dogic unit (ALU) which can perform all arithmetre, logic and

shift operation also. The main functions of EU are: 1. Decoding of instruction 2. Execution of instructions

8086 has pipelining Architecture:fetching the meret instruction while the

current instruction execution is called Pipelining. While the EU is decoding an inistrution or exacting au mistruction, which does not require us of the bures, the BID fetches up to cix existención bytes, and places them on 6-byte instruction projetilique which works on the principle FIFO. When the EU is redy to take next uistruction it just grabs the istructions from uistruction prefétet queue.

| Are AH AL Accumulators                                                                                                                      |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Are Att AL Accumulations<br>Bx BH BL Bare Register Coffeet augistic wort. DS)                                                               |  |  |  |  |  |  |  |

| CX CH CL counter register                                                                                                                   |  |  |  |  |  |  |  |

| DY DH DL Data Registra EDX                                                                                                                  |  |  |  |  |  |  |  |

| Land love legisters are general purply                                                                                                      |  |  |  |  |  |  |  |

| Even though the above though some special people.                                                                                           |  |  |  |  |  |  |  |

| Even though the above is having some special people.<br>registers. Every register is having some special people.                            |  |  |  |  |  |  |  |

| segment Rogisleir                                                                                                                           |  |  |  |  |  |  |  |

| CS Code pegment Register<br>DS Data segment Register<br>ES Extra segment Register<br>SS Stack segment Register<br>CS Stack segment Register |  |  |  |  |  |  |  |

| Att the Begnewet Register are used to store starting<br>address of Respective Sequent. Cuppe order 16-1515                                  |  |  |  |  |  |  |  |

| address of hespecture                                                                                                                       |  |  |  |  |  |  |  |

| of 20, bit address) ·                                                                                                                       |  |  |  |  |  |  |  |

| Pointer and Indup Registers! -                                                                                                              |  |  |  |  |  |  |  |

| IP Instruction Pointer Reg.                                                                                                                 |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

| <u>SP</u> Stack pointing Reg.<br><u>BP</u> Base pointing Reg.<br><u>SI</u> Source Indep Reg.                                                |  |  |  |  |  |  |  |

| Deltroutor                                                                                                                                  |  |  |  |  |  |  |  |

| atta acta as an offset register wisit                                                                                                       |  |  |  |  |  |  |  |

| IP:- This register acts as our offset register w.r.t<br>to CS. offset means distance from the base of                                       |  |  |  |  |  |  |  |

| it. reament                                                                                                                                 |  |  |  |  |  |  |  |

| SP&BP! - There two regulars acts as offset legislere                                                                                        |  |  |  |  |  |  |  |

| Wirit to SS.                                                                                                                                |  |  |  |  |  |  |  |

| SI &DI! - These two Registers acts as offlet legs.                                                                                          |  |  |  |  |  |  |  |

| w.r.t to Eptra segment.                                                                                                                     |  |  |  |  |  |  |  |

|                                                                                                                                             |  |  |  |  |  |  |  |

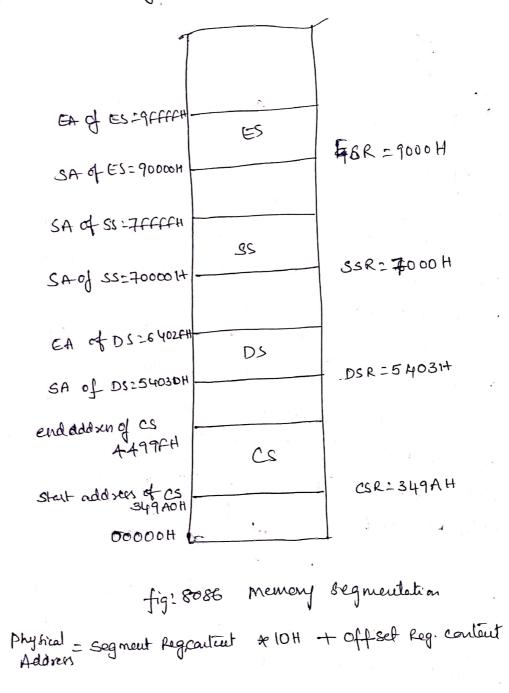

-flag Register:-14 13 12 10 UAFUPFUCF U OF DF IF IF SF 26 U= undefined Carry flag set by carry Trapflag out of MSB for single Parity flag stepping set it result has Intempt flag even parity. -for enabling Auxillary carry-flag interrupt for BLD. Direction flag 2 croflag - set if result=0 for string operations sign flag - HSB of result averflow flag. Memory Segmentation The memory in 8086 based system is organized as regnessed memory. The CPU 8086 is able to access IMB of physical memory. The memory devided with no of dogical segment and each S sequent is having the capacity of 64KB. Regments can be overlapped are upon the other. The 8086 microprocessor is having 20-bit address buy and 16-bit Data bus. with 20-bit address bus the CPU Can address 220 memory ladious means [MB(1,048,576) locations. To write an assembly longuage program we require de different segments. Jev 8086 They are codesegment, Data segment, stack Segnent and extrasegment.

To address any memory location from any of la segments we need 20-bit address, But the segment registéris can store only oupper 16-bits of address. So; to calculate the 20-bit physical address of any memory location we take the help of segment register and respective offset Register. The physical address calculation is done by physical address generator.

UN17-11 (PA-RT-2)

4

I Instruction set alchitecture of a CPU;

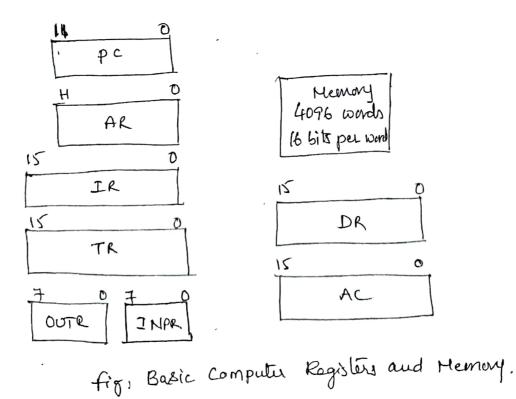

| Registers: - In a basic computer the following<br>dist of registers are available.     |                                                                                                                                                         |                                                                                                                                                                                                                |  |  |  |  |  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Register Symbol &<br>Number of<br>bite                                                 | Registre<br>Name                                                                                                                                        | femilian                                                                                                                                                                                                       |  |  |  |  |  |

| DR (16)<br>AR (12)<br>AC (16)<br>IR (16)<br>PC (12)<br>TR (16)<br>INPR (8)<br>OUTR (8) | Data Register<br>Address Register<br>Accumulator<br>Instruction Register<br>Program Cocenter<br>Temporary Register<br>Input Register<br>Output Register | Holds Memory operand<br>Holds -Addren for Memory<br>Procensor Register<br>Holds Instruction coole<br>Holds address of instruction<br>Holds temporary pata<br>Holds Liepert Character<br>Holds output character |  |  |  |  |  |

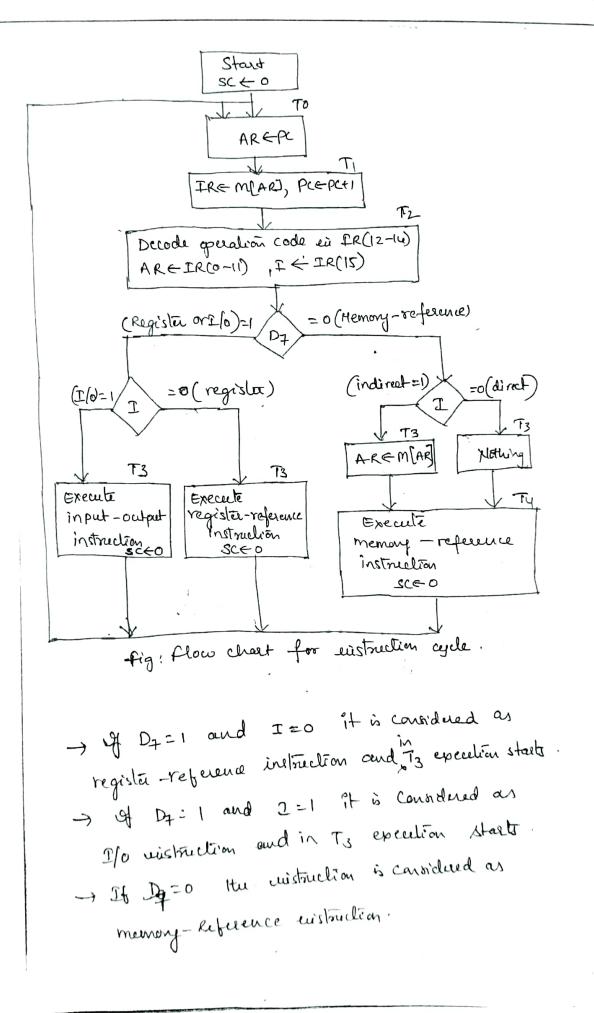

Instruction <u>Courcle</u>:-A program residing with the memory unit of a campula <u>Coursisling</u> & equivation of <u>wintfructions</u>. The program is executed in the <u>Computer by going</u> through a cycle for each instruction. Each instruction cycle to entition is <u>subdivided</u> into a sequence of subsector or phases.

In the book basic computer each instruction Cycle consists of the following phases.

1. fetch an existruction from memory

a. Decode the existención

3. Read the effective address from memory if the instruction has an indirect address. 4. Execute the instruction.

upon the completion of step 4, the control goes back to step 1 to fetch, decode and execute nept instruction.

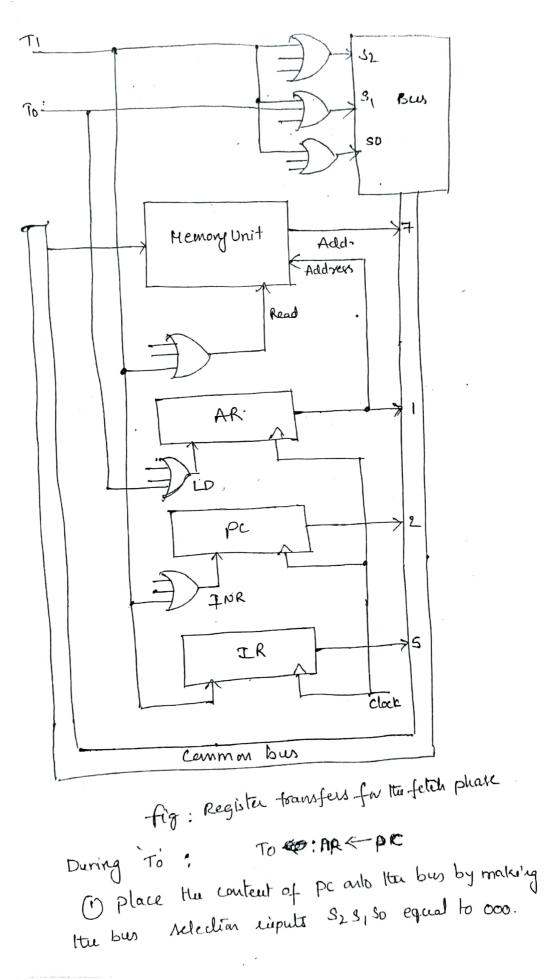

$\begin{array}{l} \underline{fetth} \ \underline{oud} \ \underline{becode}:-\\ To : AR \in PC\\ T_1 : JR \in M[AR], \ PC \in PC+1\\ T_2 : Do, \ldots, D_4 \leftarrow Decode \ JR(12-14), \\ AR \in JR(0-11), \ J \in JR(17)\\ \end{array}$  The above three lines shows the RTL (RegisterTransfer language) for fetch and Decode cycles.

In time period To, the address of PC is loaded with AR. (Initially PC contrains starting address of program)

K.

In T<sub>1</sub> the period M[AR] intronsforred to I:R:(Instruction Register) and PC is wirreneutred by '1'. In To and T<sub>1</sub> three periods fetch cycle will be completed.

In  $T_2$  time period Decode cycle will be completed  $T_2$ : Do, ...,  $D_{\mp} \in Decode IR(12-14)$ ,  $AR_{\pm} \in IR(0-11)$ ,  $F_{\pm} \cdot I \in IR(15)$

the diagram for the fetch phase is shown below.

⇒ Since anly AR is connected to the address hippets of memory it is necessary to transfer the address from pc to AR during the clock associated with timing signal TO.

=> The instruction read from memory is their placed with instruction Register IR with the clock transistion arsoviated with Honing signal T1' At the same time PC is incremented by it to prepare it for the address of the next histruction wi the program.

Scanned with OKEN Scanne

E Scanned with OKEN Scan

d. Transfer the centert of the bus to AR by enabling the ND ereput of AR. During TI TI: DREM (AR), PCE PC+1 1. Enable the Read Riepet of memory 2. Place the content of memory on to the bus by making S2 S1 S0 = 111 3. Thansfer the content of the bus to IR by cerabling the LD event of IR. A . Increment PC by enabling the INR input of PC. Instruction cycle The fig below shows the Pristneetion copile. > In the mistruction cycle the first two time periods To and Ti are for fetch cycle. -> The T' time period is for decoding. Decoding means the computer understands the meaning of eustruction. Q If decides whether the tu uistruction is memory-reference instruction, register - reference instruction offor) /o instruction. In T'z' it self address part of IR is bransferred to AR and IR(15) is transferred to I. After decoding if Dy = 1 it must be either Register-reference or Iloinstructur

Scannod will aver

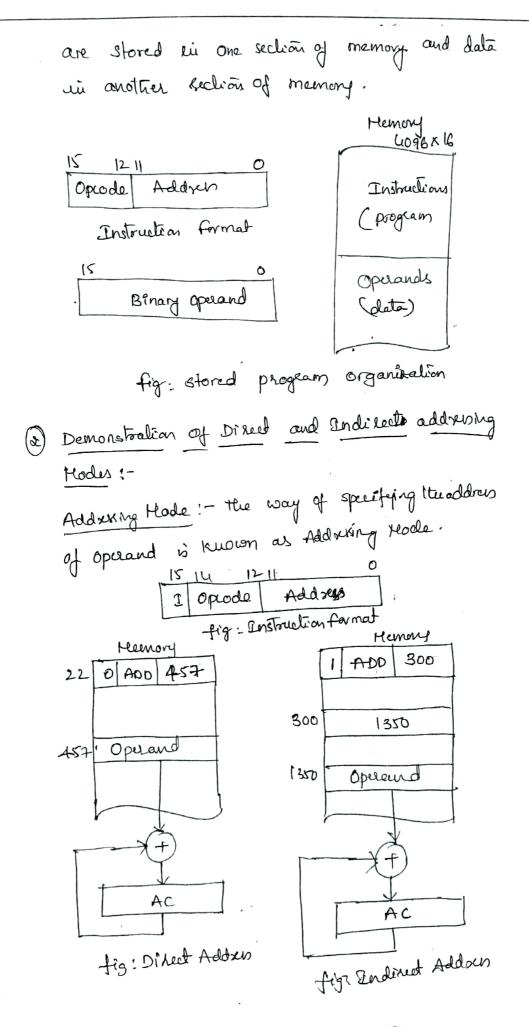

-) If Dy to and I to it is considered as Direct addressing mocks memory reference instribion. Then in To time period nothing will happen. -> If Dy=0 and I=1 it is considered as Indirect addressing mode memory represence uistruction. Then in Ty time period. M[AR] is transferred to AR. TI: AR - M[AR] -) In Ty time peuid teemory-higerence reistruction execution cycle starts. -> In T3 time period the following operations are performed The three instructions types are subdivided. uito four sepurate paths. The operations performed lie four paths are shown below. Dy IT3 : AR < M[AR] Dy I I'T3 : NIOLAING Dy Il r3 : Execute a registre reference wistmichion D7 IT3 : Execute a input output instruction Some pre-requester to studay Instruction cycle:-1) Stored Program Organization,-In This Von-neumanny architective, Stored program organization is used where instruction

| 2 | 3 Com                                                                                              | pater Ir     | atoritime    |                                                       |  |  |

|---|----------------------------------------------------------------------------------------------------|--------------|--------------|-------------------------------------------------------|--|--|

|   |                                                                                                    |              |              |                                                       |  |  |

|   | 15 14 12 11 0<br>I Opcode Addows (Opcode = 000 through<br>(a) Memory - reference Instruction (110) |              |              |                                                       |  |  |

|   | (0                                                                                                 | ) Memor      | 1 - refere   | me Justruction                                        |  |  |

|   | 15 1                                                                                               |              |              |                                                       |  |  |

|   |                                                                                                    |              |              | operation (opeode = 111, I=0)                         |  |  |

|   | C                                                                                                  | By Regist    | ir-refu      | ence Oustrudian                                       |  |  |

|   | 15                                                                                                 | 14 12-11     |              | operation (operation, I=1)                            |  |  |

|   |                                                                                                    |              |              |                                                       |  |  |

|   | $(\mathcal{C}$                                                                                     | Input        | t cutput     | + Que Fruchion.                                       |  |  |

|   |                                                                                                    |              | imal code    | Description .                                         |  |  |

|   | _symbol                                                                                            | I -0         |              | AND manage word to AC-                                |  |  |

|   | AND                                                                                                | OXXX<br>XXXO | 8xxx<br>9xxx | AND memory word to AC<br>ADD on y "                   |  |  |

|   | ADD                                                                                                | 2 x x x      |              | LOAD " AC'IN"                                         |  |  |

|   | LDA<br>STA                                                                                         | 3XXX         | BAXA         | STORE content of memory                               |  |  |

|   | BUN                                                                                                | y xxx        | CARX         | amount curconditionally                               |  |  |

|   | BSA                                                                                                | 5772         | DXXX         | Branch and save returnadates                          |  |  |

|   | ISE                                                                                                | 6***         | Ex xx        | Increment and skip of zero                            |  |  |

|   | CLA                                                                                                | 7800         |              | Clear AC                                              |  |  |

|   | CLE                                                                                                | 7400         |              | Clear E                                               |  |  |

|   | CMA                                                                                                | 7200         |              | Complement AC                                         |  |  |

|   | CME                                                                                                | 7100         |              | Complement E<br>Circulate right AC and E              |  |  |

|   | CIR                                                                                                | 7-080        |              | Circulate left AC and E                               |  |  |

|   | CEL<br>ENC                                                                                         | 7040         |              | Circulate (F)                                         |  |  |

|   |                                                                                                    | 7020         |              | Increment AC<br>skip rept elistruction if AC positive |  |  |

|   | SPA<br>SNA                                                                                         | 7010         |              | skip next b 1 Acinegation                             |  |  |

|   | SZA                                                                                                | 7008         |              |                                                       |  |  |

|   | 520                                                                                                | 7004         |              |                                                       |  |  |

|   | HLT                                                                                                | 7-002        |              | h h h h E LO                                          |  |  |

|   | FTCI                                                                                               | 7001         |              | Halt Compulier                                        |  |  |

|   | INP                                                                                                |              | £800         | Enput character to Ac                                 |  |  |

|   | DUT                                                                                                |              | £400         | Output character from Ac                              |  |  |

|   | SKI                                                                                                |              |              | skip on euput flag                                    |  |  |

|   | SKO                                                                                                |              | £100         | skip on output flag.                                  |  |  |

|   | ION                                                                                                |              | F-080        | Interrupt on                                          |  |  |

|   | IOF                                                                                                |              | F040         | Interrept off                                         |  |  |

|   |                                                                                                    | , Rasia      | Chungal      | T (mpt.u.)                                            |  |  |

Fig: Basic Canapulie Instructions

A Thirt

3

| N T T  | Interpretation of Instructions:-<br>- Roberouce Instructions<br>3 =r ( common to all register ref<br>) = B;( bit luIR(0-11) that spe | erence instructions)<br>affies the operation) |

|--------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Symbol | RTL                                                                                                                                  | Description                                   |

|        | Y! SCEO                                                                                                                              | Clearsc                                       |

| CLA    | YB <sub>11</sub> : A ← 0                                                                                                             | clear AC                                      |

| CLE    | rBID: Eto                                                                                                                            | Clear E                                       |

| CMA    | rBg: AceAc                                                                                                                           | Complement A.C                                |

| CME    | rBg : E€Ê                                                                                                                            | Complement E<br>cèrcelae right                |

| CLR    | YBZ; ACESHYAC, AC(IS) EE,                                                                                                            | circular right                                |

| CIL    | $rB6: AC \in shIAC,$<br>$AC(0) \in E, E \in AC(1S)$                                                                                  | Cercular Leff                                 |

| INC    | NB5! ACEACHI                                                                                                                         | Increment Ac                                  |

| SPA    | 2 BA . TH (-AC(15)-0) (HELL                                                                                                          | skip if positive                              |

| SNA    | rB3: if (Ac(15)=1) then                                                                                                              | skip it regalize                              |

|        | PCZPC+1                                                                                                                              | skip if negalize                              |

| SZA    | YB2: if (AC=0) them<br>preperty                                                                                                      | skip if AC zero                               |

| 520    | rB1 ! if (E=0) then PCEPC+1                                                                                                          | skip if E Zero.                               |

| H-CT   | Mg: # 5€-0 (s is a<br>start slop flip flop                                                                                           | Halt computer.                                |

| ·      |                                                                                                                                      |                                               |

The above table Represents RTL Priterprélation of régister leference instructions: <u>Hemory-Référence Instructions:</u> RTL interpretation of all Hemory-Reference instructions is shown belows. <u>AND to AC:</u> DoTY: DR E-M[AR] DoT5: ACEACADR, SC <del>CO</del> ADD to AC :-

ISZ: Increment and skip 1) sero

$$D_{6}T_{4}$$

:  $DR \leftarrow M[AR]$

$D_{6}T_{5}$ :  $DR \leftarrow DR + 1$

$D_{6}T_{6}$ :  $M[AR] \leftarrow DR$ ,  $ib(DR=0)$  liven

$(PC \leftarrow PC + 1)$ ,  $BC \leftarrow 0$

$D_{\mp}IT_{3}=p$  (common to us superior the  $IT_{3}=p$  (common to us superior that specifies the  $IT_{3}=Bi$  [bit will IR[6-11] that specifies the instruction)

| e test | RTL                                          | Description           |

|--------|----------------------------------------------|-----------------------|

| Symbol | P:SCEO                                       | clear sk              |

| INP    | PB11: AC(0-7) € 2NPR,                        | Input character.      |

|        | ·FGI ←0                                      |                       |

| OUT    | PBID: OUTRE AC(0-7),                         | Output characlui -    |

|        | faoeo                                        |                       |

| SKI    | PBq: IF(far =1) lhon<br>PCEPC+1              | skip if Proput flag   |

| SKO    | $PB_{g}$ if $(FGO = 1)$ lum $pC \neq PC + 1$ | slip on output flag   |

| ION    | PB7: LENEI                                   | Interrupt cuable on   |

| LOF    | PBO: IENCO                                   | Interrupt enable off. |

Canned with OKEN Scann

10

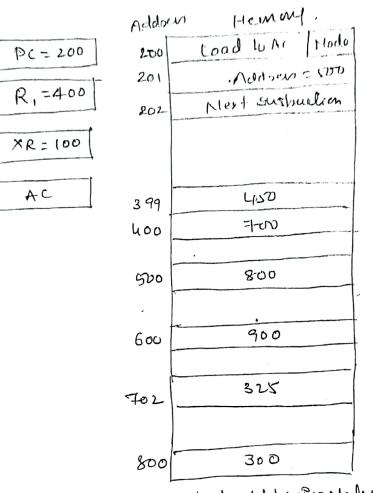

Addressing Modes :-

The way of specifying the address of the operand is known as addressing mode. I. Emplied Mode: - In this mode the operands are specified emplicitly in the definition of the enstruction. For example, the existruction "complement Accumulator" is an implied mode enstruction because the operand in the accumulator legislet is emplied with the definition of the enstruction

d. <u>Immediate Hode</u> 1 - In this mode operand is specified is the existence in itself. That means an immediate mode instruction has an operand field. Than an address field.

3 - Register Mode! - In this mode the operands are his Registers that leside witheir the CPU.

H. Register endiked Mode: - In this mode the eristruction specifies a register in the CPU whole contents give the address of the operand we memory.

5. Auto micrement or Acto decrement mode:-This is Similar to the legisler mode work Except that the register in incremented or deccremented after (or before) its value is

10

used to acces merry.

6. Direct Addson Mode! - In this mode the effective address is equal to the address part of the existance

4. Indirect Address Mode!- In this mode the address of the mistruction gives the address where the effective address 5 stored is memory (i., address of address of operand.

8. <u>Relative address Mode</u>: - In this mode the Conteast of the program counter is added to the address past of the mistrution wi order to obtain the effective address.

9. Indeped Addressing Mole: - In this mode Its content of an mideo registre is added to the address part of the metruction to obtain the effective address

10 Bare regester addressing reade! - In this addressing mode the content of the bare register is added to the address part of the mistruction to obtain the effective addresso.

A Mumerical example is shown

below.

fis: Numerical example for Addrining Moder.

| Addrening Hode                       | Effective Add xm | content<br>of f.c |

|--------------------------------------|------------------|-------------------|

| Direct address                       | 600              | 800               |

| Fundiale operand                     | 201<br>800       | 300<br>300        |

| Indirect address<br>Relative address | 702              | 325               |

| Endeped address                      | 600              | 900               |

| Register                             |                  | Ato O             |

| Register under rect                  | 400              | 700               |

| Acito excrement                      | 399              | 450               |

| fig! Tabulo                          | r list of Namu   | rial Example.     |

$(\mathbf{I})$

Instruction Set:-

Most computer mistructione can be clarrified mito three categories:

- 1. Data transfer instructions

- 2. Data Hanipulation Instructions

- 3. program control existructions.

| · Data | Transfer | Instructions:- |   |

|--------|----------|----------------|---|

|        | Name     | Mnemonic       | - |

|        | Load     | LD             |   |

| Load     | LD . |

|----------|------|

| store    | ST   |

| Hove     | Hov  |

| Exchange | XCH  |

| 0        | IN   |

| Input    |      |

| Output   | OUT  |

|          | PUSH |

| Push     |      |

| POP      | Pop  |

|          |      |

à Data Manipulation Quetructions There are litree types of Data manipulation

instructions,

1. Arithmetic Instructions a degrical and Bit manipulation instructions 3. Shiff Pritructions

| Aritzmeti | c Justruch  | row             |          |

|-----------|-------------|-----------------|----------|

|           | 1 Hneenonic | 1 Name          | Mnemonic |

| Name      | 2 10        | Hultiply        | MUL      |

| Increment |             | Divide          | DIU      |

| Decrement | DEC         | Add with Carry  | ADDC     |

| pdd       | ADD         | Cultura et with | COBR     |

| sub ract  | SUB         | Negati          | NEG      |

|           |             | Niegau          | · · ·    |

| 1         |             |                 |          |

| Lugi | cal and f                                                                                                                   | Ril Hanipulal                                                               | an Oustneet ans :- |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------|

| Logi | Lame<br>Clear<br>Cauplemond<br>AND<br>OR<br>Exclusive-OR<br>Clear Carry<br>Set Carry<br>Cauplementicary<br>Enable Enterrupt | MINE MIONIC<br>CCR<br>COM<br>AND<br>OR<br>XOR<br>CLRC<br>SETC<br>COMC<br>EI |                    |

|      | Drsable Interrupt                                                                                                           |                                                                             |                    |

Shift Instructions:-

|                            | Hnemonic |

|----------------------------|----------|

| Name                       | SHR      |

| Logical shift Right        | SH4      |

| Logical shift left         | SHRA     |

| Arithmetic shift kight     | SHLA     |

| Anthonelic shift left      | ROR      |

| Rotate Right               | ROL      |

| Dotati Utt                 | RORL     |

| Polate night Through carry |          |

| Rotali left Through carry  | ROLC     |

|                            |          |

| Diagram | Control Unstruct | Four     |

|---------|------------------|----------|

| Program | Manie            | Memonic/ |

|         | Branch           | BR       |

|         | Jump             | JMP      |

|         | skip             | SKP      |

|         | Call             | CALL     |

|         | Relien           | RET      |

|         | Compare (by sus) | CMP      |

|         | Test ( by AND)   | TST L    |

|         |                  |          |

(12)

| Canditional B | ranch Instructions    |                |

|---------------|-----------------------|----------------|

| Mnemonic      | Branch Coudi lion     | test-condition |

| Millionac     |                       | 221            |

| BZ            | Branch if Zero        | 720            |

| BNE           | Branch if not zero    | -              |

|               | Branch it carry.      | CI             |

| BC            |                       | C=0            |

| BNIC          | Branch if no carry    |                |

| BP            | Branch it plus        | 5-0            |

|               |                       | 5=1            |

| BM            | Branch if minus.      |                |

| BV            | Branch it overflow    | VEI            |

| BNV           | Branch if no overflew | V=0            |

|               | Branch of the Oregiew |                |

,

.

.

.

• \*

#### Unit-II (Part-2)

#### CPU Control unit design: Micro-programmed design approach.

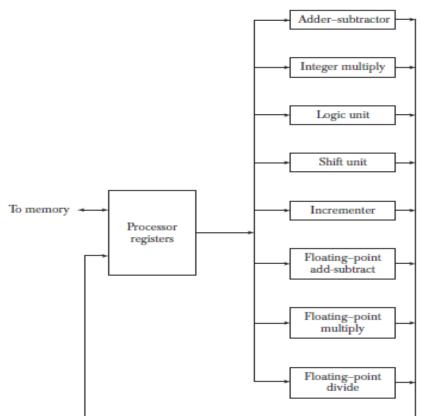

The major functional parts in a digital computer are Central Processing Unit (CPU), Memory, and Input–output. The main functional units of CPU are control unit, arithmetic and logic unit, and registers. The function of the control unit in a digital computer is to initiate sequences of microoperations.

There are two types of control units. One is Hardwired and the other one is called Microprogrammed Control Unit. When the control signals are generated by hardware using conventional logic design techniques, the control unit is said to be **hardwired Control Unit**. In **Microprogrammed Control Unit** the control unit initiates a series of sequential steps of microoperations. Micro operation is group of control variables (signals),

The control variables at any given time can be represented by a string of 1's and 0's called a **control word (Micro instruction)**. As such, control words can be programmed to perform various operations on the components of the system. A control unit whose binary control variables are stored in memory is called a *microprogrammed control unit*. Each word in control memory is called as *microinstruction*. The microinstruction specifies **one or more microoperations** for the system. A sequence of microinstructions constitutes a *microprogram*.

Since alterations of the microprogram are not needed once the control unit is in operation, the control memory can be a read-only memory (ROM). ROM words are made permanent during the hardware production of the unit.

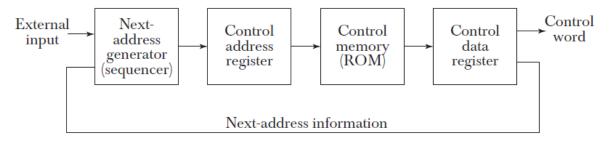

A memory that is part of a control unit is referred to as a *control memory*. The general configuration of a microprogrammed control unit is demonstrated in the block diagram shown below. The control memory is assumed to be a ROM, within which all control information is permanently stored. The control memory address register specifies the address of the microinstruction, and the control data register holds the microinstruction read from memory.

Figure Microprogrammed control organization.

The microinstruction specifies one or more microoperations for the data processor. Once these operations are executed, the control must determine the next address. The location of the next microinstruction may be the one next in sequence, or it may be located somewhere else in the control memory. For this reason, it is necessary to use some bits of the present microinstruction to control the generation of the address of the next microinstruction. The next address may also be a function of external input conditions.

While the microoperations are being executed, the next address is computed in the next address generator circuit and then transferred into the control address register to read the next microinstruction. Thus, a microinstruction contains bits for initiating microoperations in the data processor part and bits that determine the address sequence for the control memory.

### **Address Sequencing**

The address sequencing (Next address generation) capabilities required in a control memory are:

- 1. Incrementing of the control address register.

- 2. Unconditional branch or conditional branch, depending on status bit conditions.

- 3. A mapping process from the bits of the instruction to an address for control memory.

- 4. A facility for subroutine call and return.

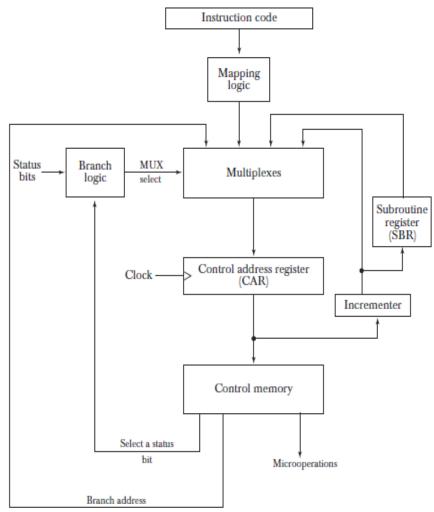

Figure below shows a block diagram of a control memory and the associated hardware needed for selecting the next microinstruction address.

Figure Selection of address for control memory.

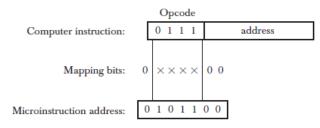

**Mapping Process:** Mapping process that converts the 4-bit operation code to a 7-bit address for control memory is shown in Fig below. This mapping consists of placing a 0 in the most significant bit of the address, transferring the four operation code bits, and clearing the two least significant bits of the control address register. This provides for each computer instruction a microprogram routine with a capacity of four microinstructions.

Figure Mapping from instruction code to microinstruction address.

#### **Computer Instruction Format**

The computer instruction format is depicted in Fig. below. These instructions are used to explain the Micro programmed Control Unit. It consists of three fields: a 1-bit field for indirect addressing symbolized by *I*, a 4-bit operation code (opcode), and an 11-bit address field. Figure below also shows lists four of the 16 possible memory-reference instructions. The instructions are ADD, BRANCH, STORE and EXCHANGE.

| ure C    | Computer instructions.                                                                                |  |

|----------|-------------------------------------------------------------------------------------------------------|--|

| 11 10    | 0                                                                                                     |  |

| de       | Address                                                                                               |  |

| (a) Inst | ruction format                                                                                        |  |

| Opcode   | Description                                                                                           |  |

| 0000     | $AC \rightarrow AC + M[EA]$                                                                           |  |

| 0001     | If $(AC < 0)$ then $(PC \leftarrow EA)$                                                               |  |

| 0010     | $M[EA] \leftarrow AC$                                                                                 |  |

| E 0011   | $AC \leftarrow M[EA], M[EA] \leftarrow AC$                                                            |  |

|          | 11         10           de         (a) Inst           Opcode         0000           0001         0010 |  |

EA is the effective address

(b) Four computer instructions

#### **Microinstruction Format**

The microinstruction format for the control memory is shown in Fig. below. The 20 bits of the microinstruction are divided into four functional parts. The three fields Fl, F2, and F3 specify microoperations for the computer. The CD field selects status bit conditions. The **BR** field specifies the type or branch to be used. The **AD** field contains a branch address. The address field is seven bits wide, since the control memory has  $128 = 2^{2}$  words.

| 3                                                                | 3  | 3  | 2  | 2  | 7  |  |  |

|------------------------------------------------------------------|----|----|----|----|----|--|--|

| F1                                                               | F2 | F3 | CD | BR | AD |  |  |

| F1, F2, F3: Microoperation fields<br>CD: Condition for branching |    |    |    |    |    |  |  |

| BR: Branch field                                                 |    |    |    |    |    |  |  |

| AD: Address field                                                |    |    |    |    |    |  |  |

| Figure Microinstruction code format (20 bits).                   |    |    |    |    |    |  |  |

The CD, BR fields are shown below.

|    | CD | Condition                                                                             |                                                              | Symbol | Comments             |  |  |  |  |

|----|----|---------------------------------------------------------------------------------------|--------------------------------------------------------------|--------|----------------------|--|--|--|--|

|    | 00 | Always                                                                                | = 1                                                          | U      | Unconditional branch |  |  |  |  |

|    | 01 | DR(15)                                                                                |                                                              | Ι      | Indirect address bit |  |  |  |  |

|    | 10 | AC(15)                                                                                |                                                              | S      | Sign bit of AC       |  |  |  |  |

| _  | 11 | AC = 0                                                                                |                                                              | Z      | Zero value in AC     |  |  |  |  |

| BR |    | Symbol Function                                                                       |                                                              |        |                      |  |  |  |  |

| 00 |    | JMP $CAR \leftarrow AD$ if condition = 1<br>$CAR \leftarrow CAR + 1$ if condition = 0 |                                                              |        |                      |  |  |  |  |

| 01 |    | CALL $CAR \leftarrow AD, SBR \leftarrow CAR + 1$ if condition = 1                     |                                                              |        |                      |  |  |  |  |

| 10 |    | DET                                                                                   | $CAR \leftarrow CAR + 1 \text{ if condition} = 0$            |        |                      |  |  |  |  |

| 10 |    | RET $CAR \leftarrow SBR$ (Return from subroutine)                                     |                                                              |        |                      |  |  |  |  |

| 11 |    | MAP                                                                                   | MAP $CAR(2-5) \leftarrow DR(11-14), CAR(0,1,6) \leftarrow 0$ |        |                      |  |  |  |  |

| The microopera | ation fields F1 | . F2. F3 are                  | shown in | figure below.  |

|----------------|-----------------|-------------------------------|----------|----------------|

| The meroopen   | auton neras i i | , <b>1 2</b> , <b>1</b> 0 ure |          | inguie beloit. |

| TABLE | Sym | r Microinstruction Fields      |        |

|-------|-----|--------------------------------|--------|

|       | F1  | Microoperation                 | Symbol |

|       | 000 | None                           | NOP    |

|       | 001 | $AC \leftarrow AC + DR$        | ADD    |

|       | 010 | $AC \leftarrow 0$              | CLRAC  |

|       | 011 | $AC \leftarrow AC + 1$         | INCAC  |

|       | 100 | $AC \leftarrow DR$             | DRTAC  |

|       | 101 | $AR \leftarrow DR(0-10)$       | DRTAR  |

|       | 110 | $AR \leftarrow PC$             | PCTAR  |

|       | 111 | $M[AR] \leftarrow DR$          | WRITE  |

|       | F2  | Microoperation                 | Symbol |

|       | 000 | None                           | NOP    |

|       | 001 | $AC \leftarrow AC - DR$        | SUB    |

|       | 010 | $AC \leftarrow AC \lor DR$     | OR     |

|       | 011 | $AC \leftarrow AC \land DR$    | AND    |

|       | 100 | $DR \leftarrow M[AR]$          | READ   |

|       | 101 | $DR \leftarrow AC$             | ACTDR  |

|       | 110 | $DR \leftarrow DR + 1$         | INCDR  |

|       | 111 | $DR(0-10) \leftarrow PC$       | PCTDR  |

|       | F3  | Microoperation                 | Symbol |

|       | 000 | None                           | NOP    |

|       | 001 | $AC \leftarrow AC \oplus DR$   | XOR    |

|       | 010 | $AC \leftarrow AC$             | COM    |

|       | 011 | $AC \leftarrow \text{shl } AC$ | SHL    |

|       | 100 | $AC \leftarrow \text{shr } AC$ | SHR    |

|       | 101 | $PC \leftarrow PC + 1$         | INCPC  |

|       | 110 | $PC \leftarrow AR$             | ARTPC  |

|       | 111 | Reserved                       |        |

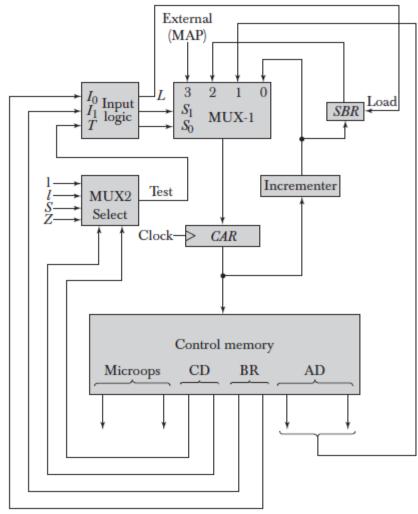

The **microprogram sequencer** for a control memory is as shown in figure below. The control memory is included in the diagram to show the interaction between the sequencer and the memory attached to it. There are two multiplexers in the circuit. The first multiplexer selects an address from one of four sources and routes it into a control address register *CAR*.

The second multiplexer tests the value of a selected status bit and the result of the test is applied to an input logic circuit. The output from *CAR* provides the address for the control memory. The content of *CAR* is incremented and applied to one of the multiplexer inputs and to the subroutine register *SBR*. The other three inputs to multiplexer number 1 come from the address field of the present microinstruction, from the output of *SBR*, and from an external source that maps the instruction.

The CD (condition) field of the microinstruction selects one of the status bits in the second multiplexer. If the bit selected is equal to 1, the T (test) variable is equal to 1; otherwise, it is equal to 0. The T value together with the two bits from the BR (branch) field go to an input logic circuit. The input logic in a particular sequencer will determine the type of operations that are available in the unit.

Typical sequencer operations are: increment, branch or jump, call and return from subroutine, load an external address and other address sequencing operations. With three inputs, the sequencer can provide up to eight address sequencing operation.

The input logic circuit has three inputs, *I*0, *I*1, and *T*, and three outputs, *S*0, *S*1, and *L*. Variables *S*0 and *S*1 select one of the source addresses for *CAR*. Variable *L* enables the load input in *SBR*. The binary values of the two selection variables determine the path in the multiplexer.

Figure Microprogram sequencer for a control memory.

**Memory system design**: Semiconductor memory technologies, memory organization. **Memory organization:** Memory interleaving, concept of hierarchical memory organization, Cache memory, cache size vs. block size, mapping functions, Replacement algorithms, write policies.

# Semiconductor Memory Technologies:

Semiconductor random-access memories (RAMs) are available in a wide range of speeds. Their cycle times range from 100 ns to less than 10 ns. Semiconductor memory is used in any electronics assembly that uses computer processing technology. The use of semiconductor memory has grown, and the size of these memory cards has increased as the need for larger and larger amounts of storage is needed.

There are two main types or categories that can be used for semiconductor technology.

**RAM - Random Access Memory:** As the names suggest, the RAM or random access memory is a form of semiconductor memory technology that is used for reading and writing data in any order - in other words as it is required by the processor. It is used for such applications as the computer or processor memory where variables and other stored and are required on a random basis. Data is stored and read many times to and from this type of memory.

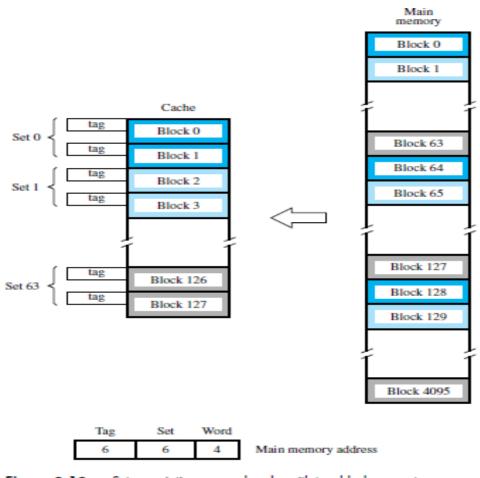

Block Diagram Representing 128 x 8 RAM (Random Access Memory)

| CS1 | CS2 | RD       | WR       | Memory function | State of data bus    |

|-----|-----|----------|----------|-----------------|----------------------|

| 0   | 0   | $\times$ | ×        | Inhibit         | High-impedance       |

| 0   | 1   | $\times$ | ×        | Inhibit         | High-impedance       |

| 1   | 0   | 0        | 0        | Inhibit         | High-impedance       |

| 1   | 0   | 0        | 1        | Write           | Input data to RAM    |

| 1   | 0   | 1        | ×        | Read            | Output data from RAM |

| 1   | 1   | ×        | $\times$ | Inhibit         | High-impedance       |

Function table

The RAM IC is in operation only when CS1 = 1 and  $\overline{CS2} = 0$ . The bar on top of the second select variable indicates that this input is enabled when it is equal to 0. CS1 = 1 and  $\overline{CS2} = 0$ , the memory can be placed in a write or read mode. When the WR input is enabled, the memory stores a byte from the data bus into a location specified by the address input lines. When the RD input is enabled, the content of the selected byte is placed into the data bus. The RD and WR signals control the memory operation as well as the bus buffers associated with the bidirectional data bus. When chip select signal lines are not enabled and either RD or WR are not enabled then the chip will be in High-impedance state.

**ROM - Read Only Memory**: A ROM is a form of semiconductor memory technology used where the data is written once and then not changed. In view of this it is used where data needs to be stored permanently, even when the power is removed - many memory technologies lose the data once the power is removed. As a result, this type of semiconductor memory technology is widely used for storing programs and data that must survive when a computer or processor is powered down. For example, the BIOS of a computer will be stored in ROM. As the name implies, data cannot be easily written to ROM. Depending on the technology used in the ROM, writing the data into the ROM initially may require special hardware. Although it is often possible to change the data, this gain requires special hardware to erase the data ready for new data to be written in.

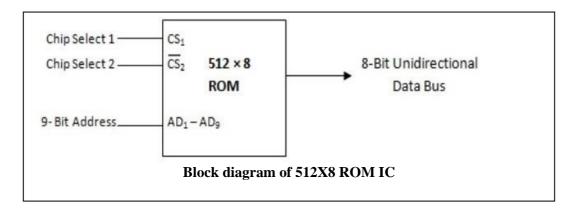

The nine address lines in the ROM chip specify any one of the 512 bytes stored in it. The two chip select inputs must be CS1=1 and  $\overline{CS2}=0$  for the IC to operate. Otherwise, the data bus is in a high-impedance state. There is no need for a read or write control because the unit can only read. Thus, when the chip is enabled by the two select inputs, the byte selected by the address lines appears on the data bus.

# The different memory types or memory technologies are detailed below:

**DRAM:** Dynamic RAM is a form of random access memory. DRAM uses a capacitor to store each bit of data, and the level of charge on each capacitor determines whether that bit is a logical 1 or 0. However, these capacitors do not hold their charge indefinitely, and therefore the data needs to be refreshed periodically. As a result of this dynamic refreshing, it gains its name of being a dynamic RAM. DRAM is the form of semiconductor memory that is often used in equipment including personal computers and workstations where it forms the main RAM for the computer.

**SRAM:** Static Random Access Memory. This form of semiconductor memory gains its name from the fact that, unlike DRAM, the data does not need to be refreshed dynamically. It is able to support faster read and write times than DRAM (typically 10 ns against 60 ns for DRAM), and in addition its cycle time is much shorter because it does not need to pause between accesses. However, it consumes more power, is less dense and more expensive than DRAM. As a result of this it is normally used for caches, while DRAM is used as the main semiconductor memory technology.

**PROM:** This stands for Programmable Read Only Memory. It is a semiconductor memory which can only have data written to it once - the data written to it is permanent. These memories are bought in a blank format and they are programmed using a special PROM programmer. Typically, a PROM will consist of an array of fusible links some of which are "blown" during the programming process to provide the required data pattern.

**EPROM:** This is an Erasable Programmable Read Only Memory. This form of semiconductor memory can be programmed and then erased at a later time. This is normally achieved by exposing the silicon to

ultraviolet light.

**EEPROM:** This is an Electrically Erasable Programmable Read Only Memory. Data can be written to it and it can be erased using an electrical voltage. This is typically applied to an erase pin on the chip. Like other types of PROM, EEPROM retains the contents of the memory even when the power is turned off.

# MEMORY ORGANIZATION

### **Memory Interleaving:**

Pipeline and vector processors often require simultaneous access to memory from two or more sources. An instruction pipeline may require the fetching of an instruction and an operand at the same time from two different segments.

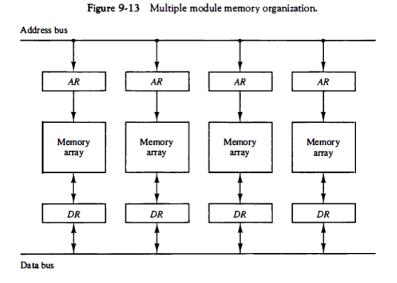

Similarly, an arithmetic pipeline usually requires two or more operands to enter the pipeline at the same time. Instead of using two memory buses for simultaneous access, the memory can be partitioned into a number of modules connected to a common memory address and data buses. A memory module is a memory array together with its own address and data registers. Figure below shows a memory unit with four modules. Each memory array has its own address register AR and data register DR.

The address registers receive information from a common address bus and the data registers communicate with a bidirectional data bus. The two least significant bits of the address can be used to distinguish between the four modules. The modular system permits one module to initiate a memory access while other modules are in the process of reading or writing a word and each module can honor a memory request independent of the state of the other modules.

The advantage of a modular memory is that it allows the use of a technique called interleaving. In an interleaved memory, different sets of addresses are assigned to different memory modules. For example, in a two-module memory system, the even addresses may be in one module and the odd addresses in the other.

## **Concept of Hierarchical Memory Organization**

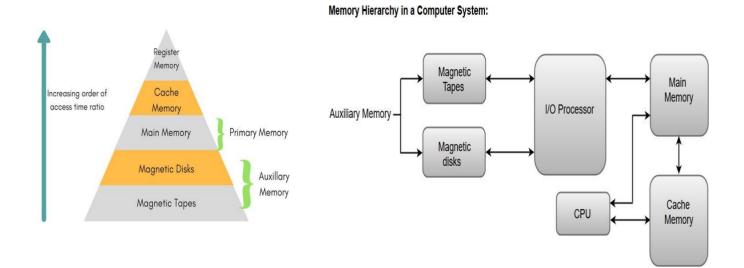

This Memory Hierarchy Design is divided into 2 main types:

# **External Memory or Secondary Memory**

Comprising of Magnetic Disk, Optical Disk, Magnetic Tape i.e. peripheral storage devices which are accessible by the processor via I/O Module.

# **Internal Memory or Primary Memory**

Comprising of Main Memory, Cache Memory & CPU registers. This is directly accessible by the processor.

### **Characteristics of Memory Hierarchy**

#### **Capacity:**

It is the global volume of information the memory can store. As we move from top to bottom in the Hierarchy, the capacity increases.

#### **Access Time:**

It is the time interval between the read/write request and the availability of the data. As we move from top to bottom in the Hierarchy, the access time increases.

#### **Performance:**

Earlier when the computer system was designed without Memory Hierarchy design, the speed gap increases between the CPU registers and Main Memory due to large difference in access time. This results in lower performance of the system and thus, enhancement was required. This enhancement was made in the form of Memory Hierarchy Design because of which the performance of the system increases.

## Cost per bit:

As we move from bottom to top in the Hierarchy, the cost per bit increases i.e. Internal Memory is costlier than External Memory.

## **Cache Memories:**

The cache is a small and very fast memory, interposed between the processor and the main memory. Its purpose is to make the main memory appear to the processor to be much faster than it actually is. The effectiveness of this approach is based on a property of computer programs called locality of reference.

Analysis of programs shows that most of their execution time is spent in routines in which many instructions are executed repeatedly. These instructions may constitute a simple loop, nested loops, or a

few procedures that repeatedly call each other.

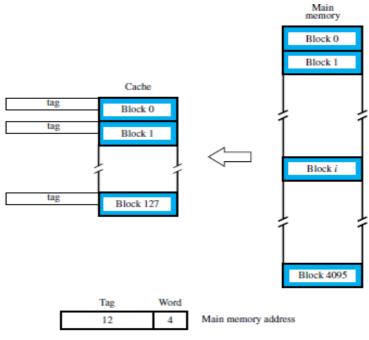

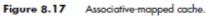

The cache memory can store a reasonable number of blocks at any given time, but this number is small compared to the total number of blocks in the main memory. The correspondence between the main memory blocks and those in the cache is specified by a mapping function.

When the cache is full and a memory word (instruction or data) that is not in the cache is referenced, the cache control hardware must decide which block should be removed to create space for the new block that contains the referenced word. The collection of rules for making this decision constitutes the cache's *replacement algorithm*.

### **Cache Hits**

The processor does not need to know explicitly about the existence of the cache. It simply issues Read andWrite requests using addresses that refer to locations in the memory. The cache control circuitry determines whether the requested word currently exists in the cache.

If it does, the Read orWrite operation is performed on the appropriate cache location. In this case, a *read* or *write hit* is said to have occurred.

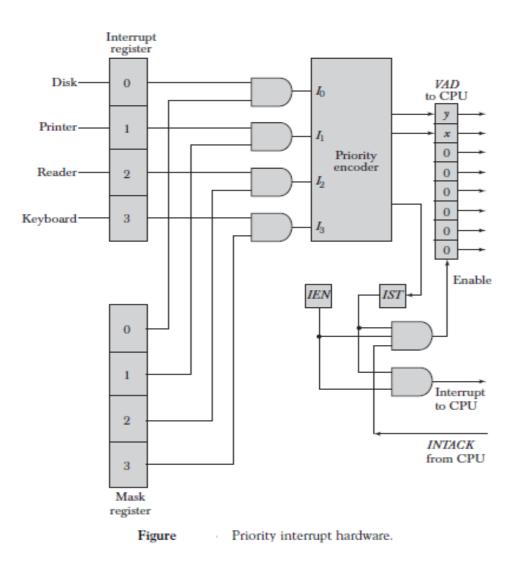

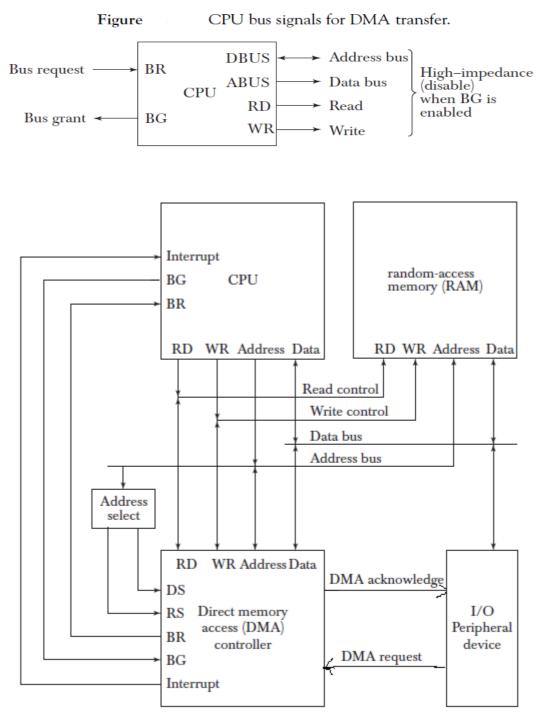

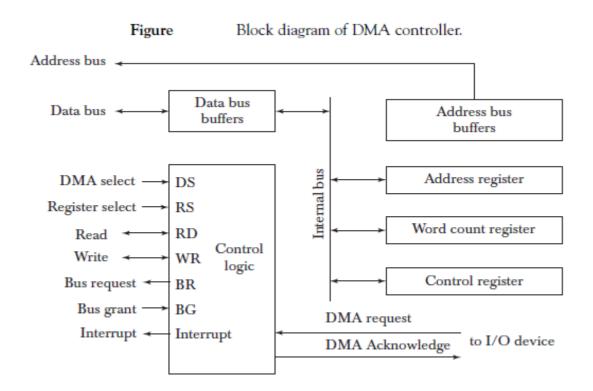

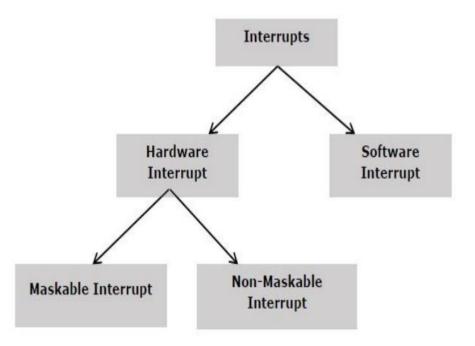

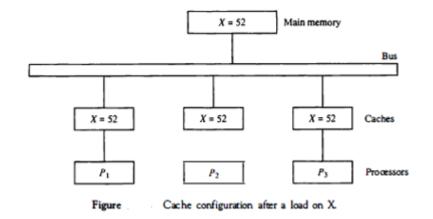

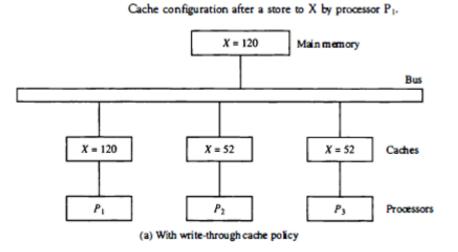

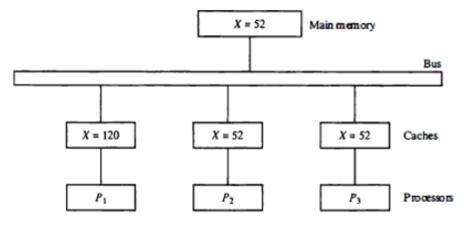

### **Cache Misses**