## **ANALOG CIRCUITS**

## **LECTURE NOTES**

B.TECH (II YEAR – II SEM) (2020-21)

## Prepared by:

**Dr. R. CHINNA RAO,** Associate Professor **Mr B.Ravichander,** Assistant Professor

**Department of Electronics and Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution – UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956

(Affiliated to JNTUH, Hyderabad, Approved by AICTE - Accredited by NBA & NAAC – 'A' Grade - ISO 9001:2015 Certified)

Maisammaguda, Dhulapally (Post Via. Kompally), Secunderabad – 500100, Telangana State, India

#### MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

II Year B.Tech. ECE-II Sem

L T/P/D C 3 -/ - /- 3

#### (R20 A0405) ANALOG CIRCUITS

#### **OBJECTIVE**

The main objectives of the course are:

- 1. Study about Wave shaping concepts of both linear and non-linear circuits.

- 2. Study about the designing of multivibrators.

- 3. Study about Time Base Generator, understanding sampling gates and Logic Gates.

- 4 .Analysis of basic transistor amplifier circuits and their frequency response Characteristics, feedback amplifiers, oscillators, large signal amplifiers

**UNIT – I BJT Amplifiers- Frequency Response:** Frequency response of an amplifier, Analysis at low and High Frequencies, Hybrid-pi  $(\pi)$  common emitter transistor model, validity of hybrid-  $\pi$  model, variation of hybrid –  $\pi$  parameters, Millers theorem and its dual, the CE short circuit current gain, current gain with resistive load, gain-bandwidth product.

**UNIT – II MULTISTAGE AMPLIFIERS:** Distortion in amplifiers, Analysis of cascaded BJT amplifier, Darlington pair, Coupling schemes-RC coupled amplifier, transformer coupled amplifier, Direct coupled Amplifier.

**UNIT - III LARGE SIGNAL AMPLIFIERS:** Classification, Distortion in amplifiers, class A large signal amplifiers, efficiency of class A amplifier, class B power amplifier, efficiency of class B amplifier, class B push pull amplifier, Complementary symmetry class B push pull amplifiers, class AB push pull amplifier, Single tuned amplifier, Principles of Staggered tuning.

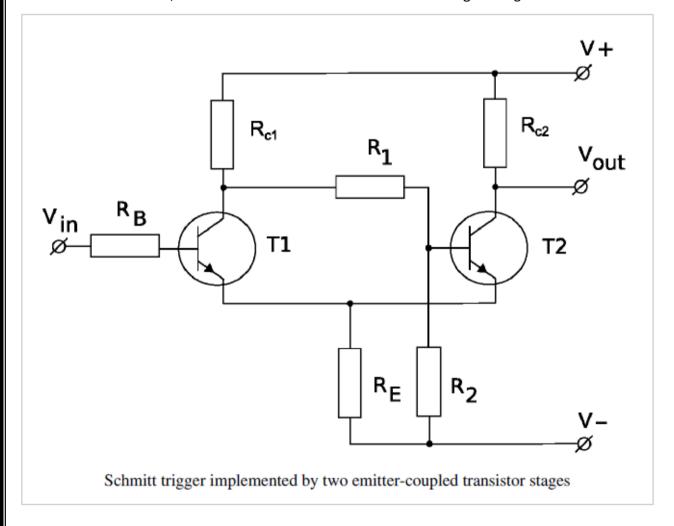

**UNIT – IV MULTIVIBRATORS:** Transistor as a switch, switching times of a transistor. Analysis of Bistable, Monostable and Astable Multivibrators, Schmitt trigger using transistors.

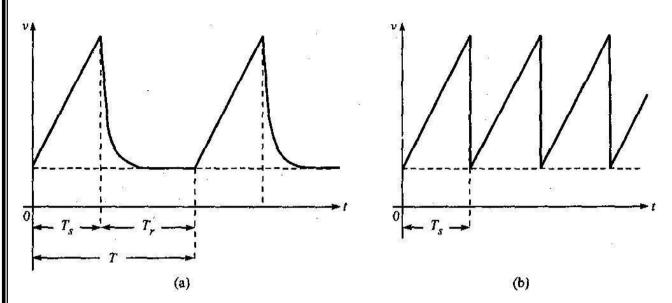

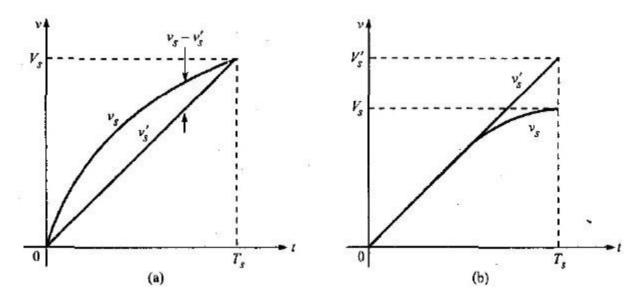

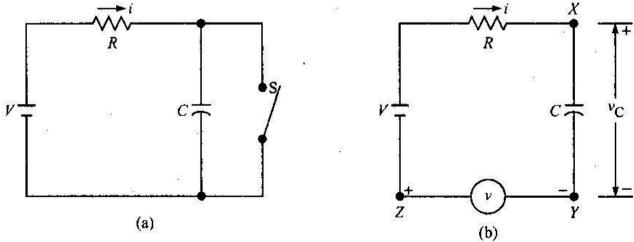

**UNIT –V TIME BASE GENARATORS:** General features of a Time Base Signal, Methods of Generating Time Base Wave forms, Basic Principles of Transistor Miller and Bootstrap Time Base Generator, Current Time Base Generator.

#### **TEXT BOOKS:**

- 1. Pulse, Digital and Switching Waveforms J. Millman and H. Taub, McGraw-Hill, 1991.

- 2. Integrated Electronics-Jacob Millman and Christos C. Halkias, 1991 Ed -2008, TMH.

#### **REFERENCE BOOKS:**

- 1. Pulse and Digital Circuits A. Anand Kumar, PHI, 2005.

- 2. Pulse, Digital Circuits and Computer Fundamentals R. Venkataraman.

- 3. Microelectric Circuits-Sedra and Smith-5 Ed., 2009, Oxford University press.

- 4. Electronic Circuit Analysis-K.LalKishore, 2004, BSP.

#### **COURSE OUTCOMES:**

At the end of the course, the student will be able to;

- 1. Understand the concepts of wave shaping circuits

- 2. Design of multivibrators for various applications,

- 3. Understand the concepts of Time Base Generators , sampling gates and logic gates

- 4. Analyzed the different types of amplifiers and oscillators

## UNIT-I BJT Amplifiers- Frequency Response

#### FREQUENCY RESPONSE OF AMPLIFIERS

For any electronic circuit, the behavior of amplifiers is affected by the frequency of the signal on their input terminal. This characteristic is known as the **frequency response**.

Frequency response is one of the most important property of amplifiers. In the frequency range that amplifiers have been designed for, they must deliver a constant and acceptable level of gain. The frequency response depends directly on the components and the architecture chosen for the design of the amplifier.

Before defining in details the frequency response, we need to present the unit of decibel (dB) and the logarithmic scale related to it. When studying the frequency response, it is indeed more suitable to convert either the power or voltage gain into dB and to represent the frequency scale in a logarithmic (log) scale.

If we consider an amplifier with power gain  $A_P$  and voltage gain  $A_V$ , the power and voltage gain in dB are defined by:

$$A_P(dB) = 10 \log(A_P)$$

$$A_V(dB) = 20 \log(A_V)$$

While the gains in linear scale are always positive  $(A_P,A_V\geq 0)$ , their equivalent in dB can either be positive if an amplification is being realized  $(A_P,A_V>1)$  or negative if the input signal is attenuated  $(A_P,A_V<1)$ .

Often, it is not the gain  $A_V(dB)$  that is investigated but rather a normalized ratio  $A_V/A_{V,mid}(dB)=20log(A_V/A_{V,mid})$ . Where  $A_{V,mid}$  is called the **midrange gain** and represents the maximum gain of the amplifier in its frequency working range, for example 20 Hz - 20 kHz for an audio amplifier.

Therefore, when  $A_V=A_{V,mid}$ , the normalized gain (written indifferently  $A_V$ ) is  $A_V(dB)=0$ . This sets a 0 dB reference when the gain is maximum. It is important to note that when the power is divided by two, we observe that  $A_P(dB)=10log(0.5)=-3$  dB.

The frequency at which the power drops to 50 % of its midrange value is known as the **cutoff frequency** and noted  $\mathbf{f}_c$ . Each time that the power is halved, a reduction of 3 dB of the normalized gain is observed. Therefore  $\mathbf{A}_P$ =-3 dB corresponds to  $\mathbf{A}_{V,mid}/\mathbf{2}$ ,  $\mathbf{A}_P$ =-6 dB corresponds to  $\mathbf{A}_{V,mid}/\mathbf{4}$  and so on ...

For this same frequency, the voltage (or current) is multiplied by a factor  $\sqrt{2}$ =0.7. Halving the voltage signal corresponds to a reduction of 6 dB and follows the same pattern as presented for the power gain.

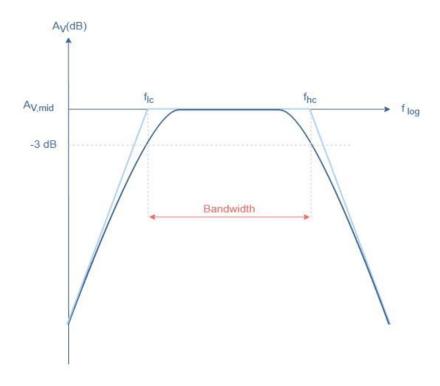

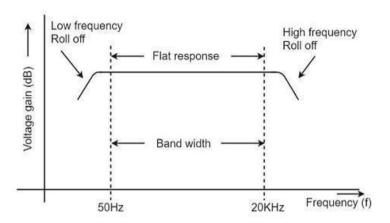

The most common tool used to represent the frequency response of any system is the **Bode plot**. It consists of the normalized gain  $A_V(dB)$  as a function of the frequency in log scale. A simplified Bode graph of an amplifier is shown in the **Figure 1** below:

Fig 1: Typical Bode graph of an amplifier

The light blue curve is called the asymptotic representation while the dark blue curve is the real frequency response of the circuit. In **Figure 1**, two different cutoff frequencies can be distinguished:  $\mathbf{f}_{lc}$  for "low cutoff" and  $\mathbf{f}_{hc}$  for "high cutoff". The quantity  $\mathbf{f}_{hc}$ - $\mathbf{f}_{lc}$  is called the **bandwidth** and represents the frequency range where the gain is above the -3 dB.

#### **EFFECT OF THE CAPACITORS:**

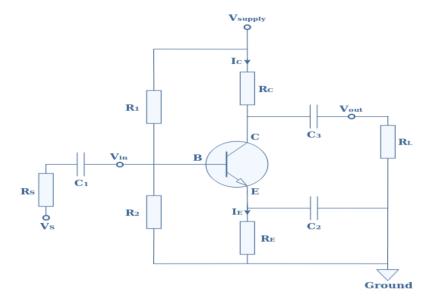

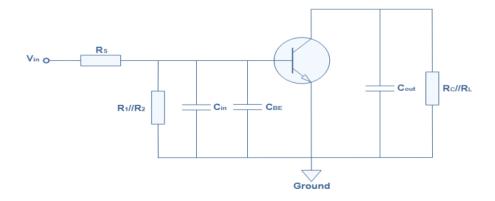

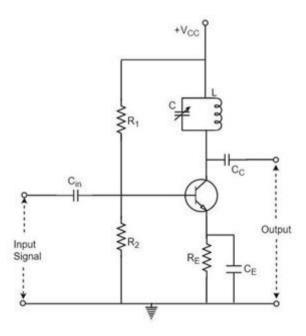

Let us consider a Common Emitter Amplifier (CEA) which configuration is shown in **Figure 2.** The structure around the BJT transistor consists of a voltage divider network ( $R_1$  and  $R_2$ ), a load ( $R_L$ ), coupling capacitors ( $C_1$  and  $C_3$ ) and a bypass capacitor  $C_2$ .

As capacitors have a property called **reactance** that is an equivalent of the resistance. The reactance  $(X_C)$  of capacitors depends on the frequency and the value of the capacitor, as in the below equation

$$X_C = \frac{1}{2\pi f C}$$

Fig 2: Common Emitter Amplifier

When the frequency is low,  $X_C$  tends to be high. Near DC signals, capacitors behave therefore as open circuits. On the other hand, when the frequency increases  $X_C$  tends to zero and capacitors act as short circuits.

At low input frequencies, the coupling capacitors will more likely block the signal, since  $X_{C1}$  and  $X_{C3}$  are higher, more voltage drop will be observed across  $C_1$  and  $C_3$ . This results in a lower voltage gain.

At high input frequencies the bypass capacitor  $C_2$  shortens the emitter branch to the ground and the voltage gain of the amplifier is  $A_V=(R_C//R_L)/r_e$  with  $r_e$  being the small diode emitter resistance. When the frequencies are lower, the resistance between the emitter and the ground is no longer only  $r_e$  but  $R_E+r_e$  and therefore the voltage gain decreases to  $A_V=(R_C//R_L)/(R_E+r_e)$ .

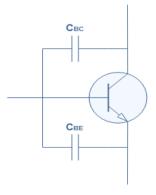

There is another type of capacitors that affect the frequency response of the amplifier and is not represented in **Figure 2**. They are known as **internal transistor capacitors** and represented in **Figure 3** below:

Fig 3: Internal transistor capacitors

Whereas the coupling and bypass capacitors act as **high-pass filter** (they block low frequencies), these internal capacitors behave differently. Indeed, if the frequency is low,  $C_{BC}$  and  $C_{BE}$  act as an open circuit and the transistor is not affected at all. However, if the frequency increases, more signal passes through them instead of going in the base branch of the transistor, therefore decreasing the voltage gain. The cutoff frequency of a RC filter:

$$f_c = \frac{1}{2\pi RC}$$

#### ANALYSIS AT LOW FREQUENCY

First of all we consider the input high-pass filter  $R_{in}C_1$ . Where  $R_{in}$  is the total input impedance of the amplifier which can be expressed as:

$$R_{in}=R_S+(R_1//R_2//\beta R_E)$$

The low cutoff frequency of the input will therefore be:

$$f_{cl.in}=1/(2\pi R_{in}C_1)$$

The same procedure can be done for the output where the output resistance is

$$R_{out}=R_C//R_L$$

The low cutoff frequency of the output filter is:

$$f_{cl,out}=1/(2\pi R_{out}C_3)$$

Finally, for the bypass capacitor, the resistance formula is more complex and given by

$$R_{bvpass} = R_E //((r_e + (R_S //\beta R_E)/\beta))$$

The low cutoff frequency of the bypass structure is thus:

$$f_{cl,bypass}=1/(2\pi R_{bypass}C_2)$$

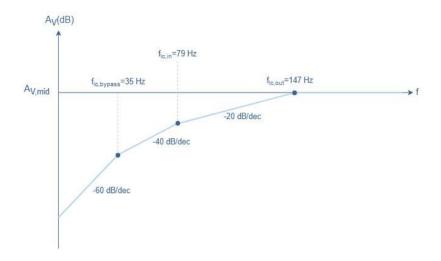

One last thing we need to understand before plotting the Bode graph is about the slope out of the midrange values. The decrease of  $A_{V,mid}$  with the frequency is called **roll-off** and its value for each simple RC filter is -20 dB/decade (dB/dec). This value means for high-pass filters (resp. low-pass filters) that each time the frequency is divided by 10 (resp. multiplied by 10), a decrease of -20 dB is observed for the gain of the amplifier.

When multiple filters are blocking the same range of frequencies, the roll-off is enhanced. In our example three filters are simultaneously blocking the frequencies below 35 Hz, the roll-off is therefore 3\*(-20 dB/dec)=-60 dB/dec.

Fig 4: Low frequency response of the CEA

#### **ANALYSIS AT HIGH FREQUENCY**

As stated previously, it is the internal transistor capacitors that will limit the gain at high frequencies acting as low-pass filters. It can be shown that the equivalent circuit of **Figure 2** at high frequency can be drawn such as presented in **Figure 5**:

Fig 5: Equivalent CEA at high frequency

We can note that the coupling capacitors are not represented since they behave as short circuits at high frequencies. Moreover, the emitter branch is shorten to the ground for the same reason applying to the bypass capacitor.

The internal capacitor  $C_{BC}$  is converted via **Miller's theorem** into the equivalent  $C_{in}$  and  $C_{out}$  capacitors. Moreover, this theorem states that

$$C_{in}=C_{BC}(A_{V,mid}+1)$$

and  $C_{out}=C_{BC}(A_{V,mid}+1)/A_{V,mid}$ .

The total input capacitance of this circuit is

$$C_{IN}=C_{BE}+C_{in}$$

;

The total input resistance is

$$R_{IN}=R_S//R_1//R_2//\beta r_e$$

.

The numerical application to our example gives

$$A_{V,mid}=(R_C//R_L)/r_e=108$$

,  $C_{IN}=575$  pF and  $R_{IN}=409$   $\Omega$ .

The high cutoff frequency of the input is therefore

$$f_{hc,in}=1/(2\pi R_{IN}C_{IN})=677 \text{ kHz}.$$

From the output point of view, the high cutoff frequency is simply given by the filter  $(R_C//R_L)C_{out}$  with  $C_{out}=5.3$  pF :  $f_{hc,out}=1/(2\pi(R_C//R_L)C_{out})=1.1$  MHz.

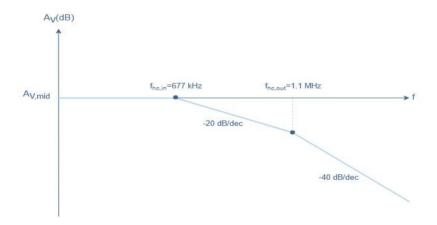

The information given here is summarized in a Bode plot representing the high frequency response of the CEA in asymptotic representation:

Fig 6: High frequency response of the CEA

By merging the two Bode graphs obtained for the low and high frequency responses in **Figure 4 and 6**, we can now plot the overall frequency response of the CEA configuration

Fig 7: Total frequency response of the CEA

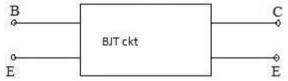

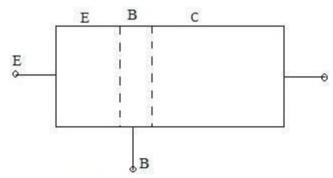

#### Hybrid-pi $(\pi)$ common emitter transistor model

For amplifier circuits Common Emitter configuration is preferred Because for Common Collector (hrc < 1). For Common Collector Configuration, voltage gain Av < 1. So even by cascading you can't increase voltage gain. For Common Base, current gain hib < 1. So overall voltage gain is < 1. But for Common Emitter, hre» 1. Therefore Voltage gain can be increased by cascading Common Emitter stage. So Common Emitter configuration is widely used.

Under reverse bias condition the capacitance at the junction is called transition or space charge capacitance. Under forward bias condition the capacitance is called diffusion or storage capacitance. At high frequencies, BJT cannot be analysed by h-parameters.

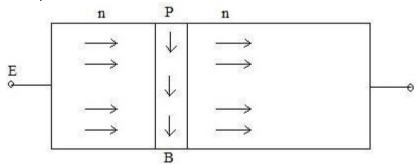

#### Giacolleto model - hybrid $\pi$ equivalent circuit

Desirable features of hybrid  $\pi$  equivalent circuit are:

- (1) The value of components in the equivalent circuit are independent of frequencies.

- (2) The values of all the resistive components in the equivalent circuit can be determined from the known or Specified values of h-parameters at low frequencies.

- (3) The results obtained by using this equivalent circuit agrees with the experimental result.

The components of the equivalent circuit exist in the form of  $\pi$  hence the name.

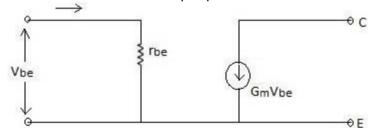

For small signal behaviour the transistor at its input port behaves as a resistor.

The output port is a dependent current source.

Because the base (B) is lightly doped all the depletion region lies entirely in the Base region. So, when the collector voltage is increased the depletion region in the base increases.

rce --> This resistance is added to compensate for the change in IC due to change in VCE.

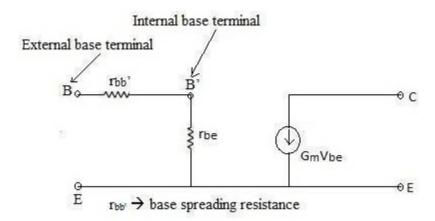

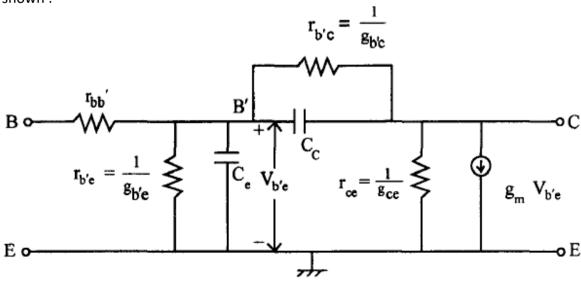

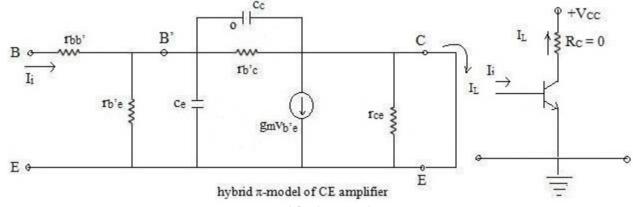

The  $Hybrid-\pi$  or  $Giacoletto\ Model$  for the Common Emitter amplifier circuit (single stage) is as shown:

Analysis of this circuit gives satisfactory results at *all* frequencies not only at *high* frequencies but also at low frequencies. All the parameters are assumed to be independent of frequency.

#### **Circuit Components**

B' is the internal node of the base of the Transconductance amplifier. It is not physically accessible.

The base spreading resistance rb'b is represented as a *lumped* parameter between base B and internal node B'.  $(g_m \ V_{b'e})$  is a current generator. Vb'e is the input voltage across the emitter junction. If  $V_{b'e}$  increases, more carriers are injected into the base of the transistor. So the increase in the number of carriers is  $\alpha \ V_{b'e}$ ). This results in small signal current (since we are taking into account changes in  $V_{b'e}$ ). This effect is represented by the current generator  $g_m \ V_{b'e}$ . This represents the current that results because of changes in  $V_{b'e}$  when C is shorted to E.

When the number of carriers injected into the base increase, base recombination also increases. So this effect is taken care of by  $g_{\rm b'e}$ . As recombination increases, base current increases. Minority carrier storage in the base is represented by  $c_e$  the diffusion capacitance.

According to Early Effect, the change in voltage between Collector and Emitter changes the base width. So base width will be modulated according to the voltage between Collector and Emitter. When base width changes, the minority carrier concentration in base changes. Hence the current which is proportional to carrier concentration also changes. So  $I_E$  changes and hence  $I_C$  changes. This feedback effect [ $I_E$  on input side,  $I_C$  on output side] is taken into account by connecting  $g_{b^Fc}$  between B', and C. The conductance between Collector and Base is  $g_{ce}$ .  $G_C$  represents the collector junction barrier capacitance.

The High frequency model parameters of a BJT in terms of low frequency hybrid parameters is given below

- Tran conductance  $g_m = I_C/V_T$

- Internal Base node to emitter resistance  $r_{b^Fe} = h_{fe}/g_m = (h_{fe} * V_T)/I_C$

- Internal Base node to collector resistance  $r_{b^Fc}=(h_{re}*r_{b^Fe})$  / (1- $h_{re}$ ) assuming hre << 1 it reduces to  $r_{b^Fc}=(h_{re}*r_{b^Fe})$

- Base spreading resistance  $r_{bb^F}$  =  $h_{ie}$   $r_{b^Fe}$  =  $h_{ie}$  ( $h_{fe}$ \* Vt )/ Ic

- Collector to emitter resistance  $r_{ce} = 1 / (h_{oe} (1 + h_{fe}) / r_{bF_c})$

#### Variation of Hybrid Parameters with $|I_C|$ , $|V_{CE}|$ and T

1) Transconductance Amplifier or Mutual Conductance (gm):

$$g_m = I_C/V_T$$

$g_m$  is  $\alpha I_C$

$V_T = T/II,600$

Therefore  $g_m \propto 1/T$

$g_m$  is independent of  $V_{\it CE}$ Since in the active region of the transconductance, Ic is independent of  $V_{\it CE}$

#### 2) Base Emitter Resistance (r b'e)

$$r_{b'e} = h_{fe}/g_m = (h_{fe}*V_T)/I_C$$

Therefore

$$r_{b'e} \propto \frac{1}{I-c}$$

$r_{b^{'}e}$  increases as T increases since  $r_{b^{'}e}$  lpha  $V_T$ .

#### 3) Base Spread Resistance $(r_{hh'})$

$r_{bb^{'}}$  decreases with increase in  $I_{\mathcal{C}}$

Since as  $I_{\mathcal{C}}$  increases, conductivity increases. So  $r_{bb^{'}}$  decreases, because of conductivity modulation. But  $r_{bb^{'}}$  increases with increase in Temperature. Because as T increases, mobility of the carriers decreases. So conductivity decreases. So  $r_{bb^{'}}$  increases.

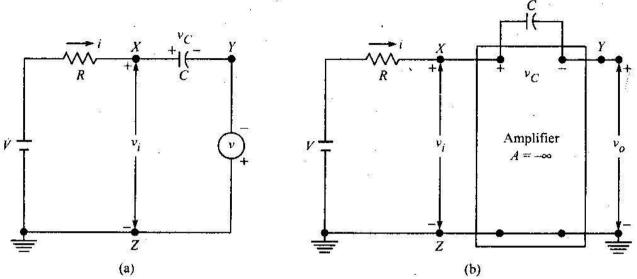

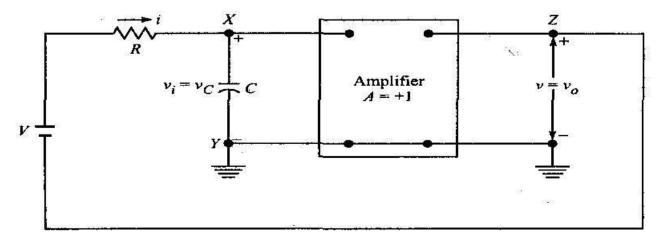

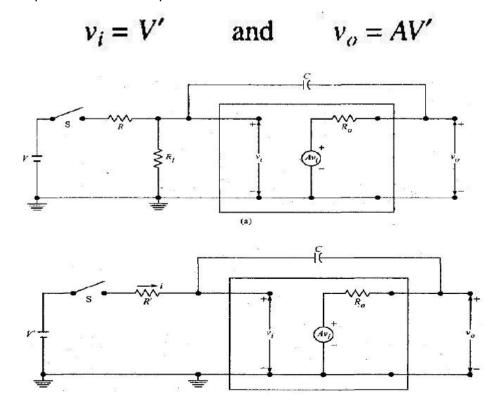

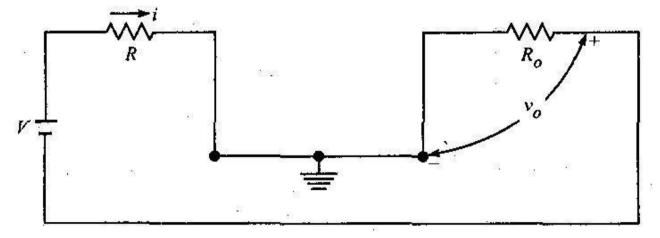

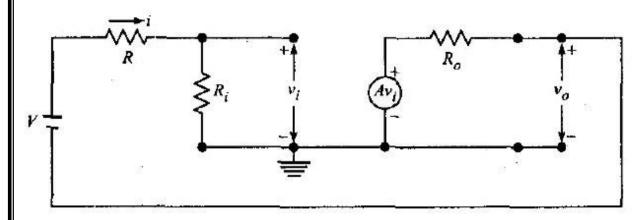

#### Miller's Theorem

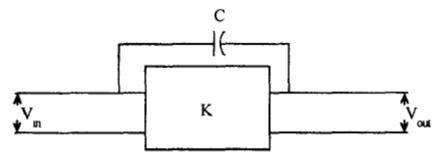

Fig. 9(a) shows an amplifier with a capacitor between input and output terminals. It is called as feedback capacitor. When the gain K is large, the feedback will change the input Z and output Z of the circuit.

Fig. 9 (a) Feedback Capacitor

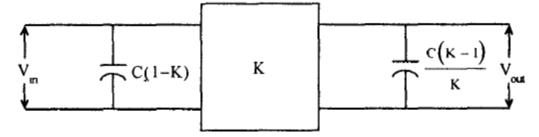

A circuit as shown above is difficult to analyze, because of capacitor. So according to the Miller's theorem, the feedback capacitor can be split into two values, one as connected in the input side and the other on the output side, as shown in Fig. 9 (b).

Fig. 9 (b) Splitting of feedback capacitor using Miller's Theorem

#### **Mathematical Proof of Miller's Theorem:**

The AC current passing through capacitor (C) in Fig. 9 (a) is

$$I_{C} = \frac{V_{in} - V_{out}}{\binom{1}{j_{WC}}} = \frac{(V_{in} - V_{out})}{-jX_{C}}$$

$$V_{out} = K V_{in}$$

Therefore

$$\mathcal{L} = \frac{(V_{in} - K V_{in})}{-jX_C} = \frac{V_{in}(1-K)}{-iX_C}$$

$$\frac{V_{in}}{I_C} = Z_{in} = \frac{\frac{V_{in}}{V_{in}(1-K)}}{-jX_C} = \frac{-jX_C}{(1-K)}$$

$$= \frac{-j}{2\pi f C(1-K)}$$

since  $X_C = \frac{1}{2\pi f C}$

$\frac{V_{in}}{I_c}$  is the input Z as seen from the input terminals.

Therefore

$$Z_{in} = \frac{-j}{2\pi f[C(1-K)]}$$

Therefore

$$C_{in} = C (1-K)$$

Similarly output capacitance can be derived as follows:

Current in the capacitor,

$$I_{C} = \frac{V_{out} - V_{in}}{-jX_{C}} = \frac{V_{out}(1 - \frac{V_{in}}{V_{out}})}{-jX_{C}}$$

$$I_C = \frac{V_{out}(1 - \frac{1}{K})}{-iX_C}$$

Rearranging the terms we get,

$$Z_{out} = \frac{-jX_{f}}{(1-K)} = \frac{-jX_{f}}{(K-1)}$$

$$= \frac{-j}{2\pi f C(K)}$$

since

$$Z_{out} = \frac{V_{f}}{Z_{out}}$$

$$Z_{out}$$

Therefore  $C_{out}$

(Miller) = C

$$\binom{K-1}{K}$$

#### Miller's Theorem

It states that if an impedance Z is connected between the input and output terminals, of a network, between which there is voltage gain, K, the same effect can be had by removing Z and connecting an impedance  $Z_i$  at the input =  $\frac{1}{(1-K)}$  and  $Z_o$  across the output =  $\frac{1}{(K-I)}$ .

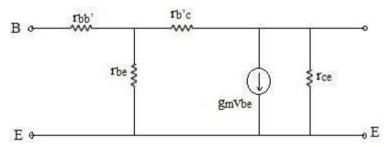

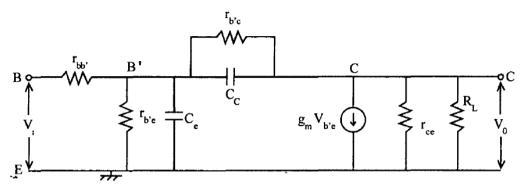

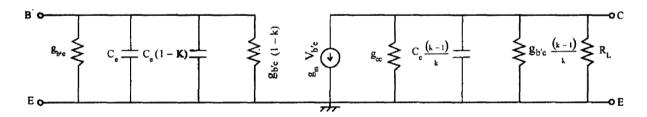

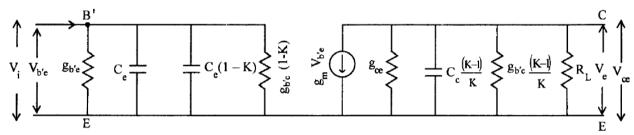

Fig 10: High Frequency equivalent circuit with resistive load

$$C_{b^Fc} = C_c$$

$r_{b'c}$  and  $C_{\ell'c}$  are between the input termed B' and output termed C. The voltage gain of the amplifier =  $\frac{C_{\ell'c}}{V_{b'c}}$  = K (> > 1). Therefore by Miller's theorem,  $C_{c}$  and  $C_{c}$  can be connected between

B' and E (input side) with values =  $\frac{C_c}{1-k_{D'c}K}$  and  $r_{b'c}(1-K)$  respectively. On the output side between Collector and emitter as  $C_c \frac{(K-1)}{K}$  and  $\frac{c_{D'c}K}{(K-1)}$  resting.

Therefore high frequency equivalent circuit using Miller's theorem reduces to, (neglecting rbb, )

$$K = \frac{V_{Ce}}{V_{b'e}}$$

$V_{Ce}$ = - $I_C.R_{L}$ , Negative is used since current direction is opposite

Fig 11: Circuit after applying Millers Theorem

$$\mathsf{K} = \frac{-I_C.R_L}{V_{b^{'}e}}$$

$$\operatorname{But} \frac{I_{\mathcal{C}}}{V_{\stackrel{'}{b'e}}} = g_m$$

Therefore  $K = -g_m \cdot R_L$

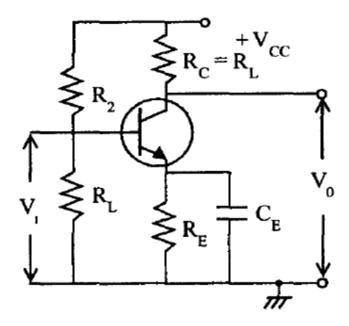

#### The CE Short Circuit Current gain (Ai)

This is the circuit of transistor amplifier in common emitter configuration

Fig.12 CE Amplifier Circuit

The approximate equivalent circuit at high frequencies, with output shorted is

Fig.13 Simplified equivalent circuit

$r_{b^Fe}$  is assumed to be very large. So it is open circuit.  $r_{ce}$  disappears since it is in shunt with short circuited output.

$$I_L = -g_m V_{b^F e}$$

Negative sign taking the direction of current into acount.  $I_L$  is contributed by the current source only.

$$V_{b^Fe} = I \times Z = I \times \frac{1}{Y}$$

$$V_{b^Fe} = \frac{I_i X_1}{g_{b^Fe} + j\omega C_e}$$

Therefore

$$I_L = \frac{-g_m I_i}{g_b F_e + j\omega C_e}$$

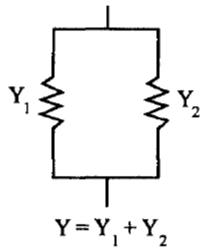

Conductances in parallel get added

Fig.14 Conductances in parallel

Therefore current gain under short circuit conditions is,

$$A_i = \frac{I_L}{I_i} = \frac{-g_m}{g_b F_e + j\omega C_e}$$

But

$$g_{b^Fe} = \frac{g_m}{h_{fe}}$$

$$C_e = \frac{g_m}{2\pi f_T}$$

Therefore by substituting all these terms in the above equation, we get

$$A_{i} = \frac{I_{L}}{I_{i}} = \frac{-g_{m}}{g_{m} - j\omega g_{m}}$$

$$= \frac{-1}{\frac{1}{h_{fe}} + \frac{j2\pi f}{2\pi fT}} = \frac{-h_{fe}}{\frac{jh_{fe} - f}{1 + \frac{j\pi f}{fT}}}$$

Since

$$\frac{f_T}{h_{fe}} = f_{\beta}$$

Therefore

$$A = \frac{-h_{fe}}{1 + j(\frac{f}{fR})}$$

When  $f=f_{\beta}$ ,  $A_i$  falls by  $\frac{1}{\sqrt{2}}$ , or by 3db. The frequency range  $f_{\beta}$  is called Bandwidth of the amplifiers.

$f_{\beta}$ : Is the frequency at which the short circuit gain in common emitter configuration falls by 3 db.

$f_T$ : This is defined as the frequency at which the common emitter shunt circuit current gain becomes 1.

Let

$$f = f_T$$

,  $A_i = 1$

Therefore 1=

$$\frac{h_{fe}}{\sqrt{1+(\frac{f_T}{f_{\beta}})^2}}$$

$$1 + \left(\frac{f_T}{f_\beta}\right)^2 = h_{fe}^2$$

$$\left(\frac{f_T}{f_\beta}\right)^2 = h_{fe}^2 - 1 = h_{fe}^2 \quad \text{since } h_{fe} >> 1$$

Therefore

$$f_T=f_{\beta}.\,h_{fe}$$

Where

$f_{eta}$  - is the Bandwidth of the transistor

$h_{fe}$  - is the current gain

$f_T$  - is the current gain, Bandwidth product

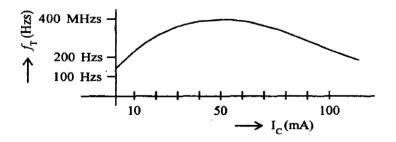

In Common Emitter configurations,  $A_i >> 1$ . But as frequency increases  $A_i$  decreases.  $f_T$  depends on the operating point of the transistor. The graph of  $f_T$  versus  $I_C$  for a transistor is as shown,

Fig.15 Variation of  $I_{\mathcal{C}}$  with frequency

For a typical transistor,  $f_T$  = 80 MHz

$$f_{\beta}$$

= 1.6 MHz

#### **Current gain with resistive load**

$$f_T = f_\beta$$

.  $h_\beta = \frac{g_m}{2\pi(C_e + C_c)}$

Considering the load resistance $R_L$ ,

$V_{b^Fe}$  is the input voltage and is equal to  $V_1$  $V_{Ce}$  is the output voltage and is equal to  $V_2$

$$K_2 = \frac{V_{Ce}}{V_{b}F_e}$$

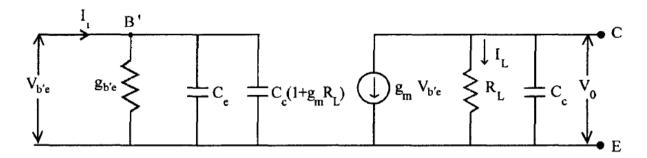

The equivalent circuit is as shown below:

Fig.16 Equivalent circuit taking Load resistance into account

This circuit is still complicated for analysis.

Because, there are two time constants associated with the input and the other associated with the output. The output time constant will be much smaller than the input time constant. So it can be neglected.

K = Voltage gain. It will be >> 1

Therefore

$$g_{b^Fc}\left(\frac{K-1}{K}\right) = g_{b^Fc}$$

$g_{b^Fc} < g_{Ce}$  since  $r_{b^Fc}$  = 4 M $\Omega$ ,  $r_{Ce}$  = 80 K (typical values)

So  $g_{\it b'c}$  can be neglected in the equivalent circuit.

In a wide band amplifier  $R_L$  will not exceed 2K $\Omega$ , since  $f_H$  lpha  $\frac{1}{R_L}$  . If  $R_L$  is small,  $f_H$  is large.

$$f_H = \frac{1}{2\pi C_S(R_C || R_L)}$$

Therefore  $g_{Ce}$  can be neglected compared with  $R_L$ .

Therefore the output circuit consists of current generator  $g_m V_{b'e}$  feeding the load  $R_L$  so the Circuit simplifies as shown in Fig. 17

Fig.17 Simplified equivalent circuit

$$K = \frac{V_{Ce}}{V_{b}F_{e}} = -g_m R_L$$

;  $g_m = 50 \text{ mA/V}$ ,  $R_L = 2K\Omega$  (typical values)

$$K = -100$$

So the maximum value is  $g_{b^Fc}$  (1-K) = 0.02595. So this can be neglected compared to  $g_{b^Fe}$ = 1mA\V.

$R_L$  Should not exceed 2K $\Omega$ , therefore if  $R_L$  > 2K $\Omega$ ,  $C_C$ (1 +  $g_mR_L$ ) becomes very large and so band pass becomes very small.

$$C \atop C \left(\frac{K-1}{K}\right) = C \atop C$$

When  $R_L = 2K\Omega$ ,

The output time constant is,

$$R_L$$

.  $C_C$ = 2 x 10<sup>3</sup> x 3 x 10<sup>-12</sup> = 6 x 10<sup>-9</sup> s (typical value)

Input time constant is,

$$r_{b^Fe} \left[ C_e + C_C [1 + g_m R_L] \right] = 403 \times 10^{-6} \, \mathrm{s}$$

So the band pass of the amplifier will be determined by the time constant of the input circuit.

The 3db frequency

$$f_M = \frac{1}{2\pi r \int_{b}^{F} C} = \frac{g_b F_e}{2\pi C}$$

Where

$$C = [C_e + C_C[1 + g_m R_L]]$$

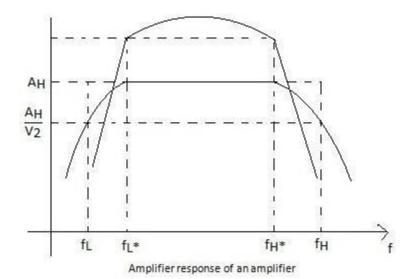

#### Bandwidth of a multistage amplifier

The range of frequencies which are amplified without much variation in gain is called bandwidth of amplifiers. Human ears are insensitive to the variation of power gain of about 3dB. Hence, frequency range from lower 3dB to upper 3dB is considered as bandwidth of single stage amplifier. Bandwidth of single stage amplifier.

Bandwidth (BW) =  $fH - fL \sim fH$

#### Lower 3dB frequency of multistage amplifier

The lower 3db frequency of n identical cascaded stages as  $f_L(n)$ . It is the frequency for which the overall gain falls to  $\frac{1}{\sqrt{2}}$  (3 db) of its midband value.

$$\frac{1}{\sqrt{1+\left[\frac{f_L}{f_L}\right]^2}} = \frac{1}{\sqrt{2}}$$

$$\begin{bmatrix} f_{L(n)} \end{bmatrix}$$

$$\left[\sqrt{1 + \left[\frac{f_L}{f_L(n)}\right]^2}\right]^n = \sqrt{2}$$

Squaring on both sides we get

$$\left[1 + \left[\frac{f_L}{f_L(n)}\right]^2\right]^n = 2$$

Taking nth root on both sides

$$1 + \left[\frac{f_L}{f_L(n)}\right]^2 = 2^{\frac{1}{n}}$$

$$\left[\frac{f_L}{f_L(\mathbf{n})}\right]^2 = 2^{\frac{1}{n}} - 1$$

Taking square root on both sides

$$\left[\frac{f_L}{f_L(\mathbf{n})}\right] = \sqrt{2^{\frac{1}{n}} - 1}$$

$$f_L(\mathbf{n}) = \frac{f_L}{\sqrt{2^{\frac{1}{n}} - 1}}$$

#### Higher 3dB frequency of multistage amplifier

The higher 3db frequency of n identical cascaded stages as  $f_H(n)$ . It is the frequency for which the overall gain falls to  $\frac{1}{\sqrt{2}}$  (3 db) of its midband value.

$$\frac{1}{\sqrt{1+\left[\frac{f_H(n)}{f_H}\right]^2}} = \frac{1}{\sqrt{2}}$$

$$\left[\sqrt{1+\left[\frac{f_H(n)}{f_H}\right]^2}\right]^n = \sqrt{2}$$

Squaring on both sides we get

$$\left[1 + \frac{f_H(n)^2}{f_H}\right]^n = 2$$

Taking nth root on both sides

$$1 + \left[\frac{f_H(n)}{f_H}\right]^2 = 2^{\frac{1}{n}}$$

$$\left[\frac{f_H(n)}{f_H}\right]^2 = 2^{\frac{1}{n}} - 1$$

Taking square root on both sides

$$\left[\frac{f_H(n)}{f_H}\right] = \sqrt{2^{\frac{1}{n}} - 1}$$

$$f(n) = f\sqrt{2^{\frac{1}{n}} - 1}$$

#### **UNIT-II**

#### Multi-stage amplifiers

In practical applications, the output of a single state amplifier is usually insufficient, though it is a voltage or power amplifier. Hence they are replaced by **Multi-stage transistor amplifiers**.

In Multi-stage amplifiers, the output of first stage is coupled to the input of next stage using a coupling device. These coupling devices can usually be a capacitor or a transformer. This process of joining two amplifier stages using a coupling device can be called as **Cascading**.

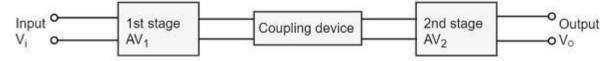

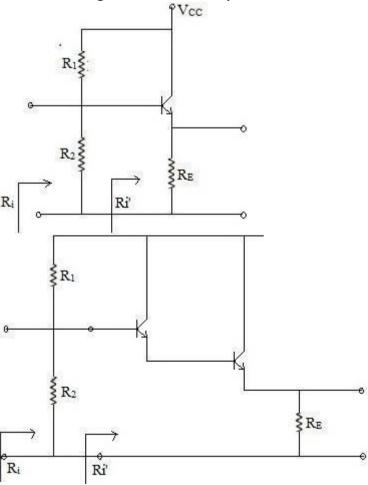

The following figure shows a two-stage amplifier connected in cascade.

The overall gain is the product of voltage gain of individual stages.

$$A = A \times A \times A = V_2 \times V_0 = V_0$$

Where  $A_V = Overall gain$ ,

$A_{V1}$  = Voltage gain of 1<sup>st</sup> stage, and

A<sub>V2</sub>= Voltage gain of 2<sup>nd</sup> stage.

If there is n number of stages, the product of voltage gains of those **n** stages will be the overall gain of that multistage amplifier circuit.

#### Purpose of coupling device

The basic purposes of a coupling device are

- To transfer the AC from the output of one stage to the input of next stage.

- To block the DC to pass from the output of one stage to the input of next stage, which means to isolate the DC conditions.

#### **Types of Coupling**

Joining one amplifier stage with the other in cascade, using coupling devices form a **Multi-stage amplifier circuit**. There are **four** basic methods of coupling, using these coupling devices such as resistors, capacitors, transformers etc. Let us have an idea about them.

#### Resistance-Capacitance Coupling

This is the mostly used method of coupling, formed using simple **resistor- capacitor** combination. The capacitor which allows AC and blocks DC is the main coupling element used

The coupling capacitor passes the AC from the output of one stage to the input of its next stage. While blocking the DC components from DC bias voltages to effect the next stage. Let us get into the details of this method of coupling in the coming chapters.

#### **Impedance Coupling**

The coupling network that uses **inductance** and **capacitance** as coupling elements can be called as Impedance coupling network. In this impedance coupling method, the impedance of coupling coil depends on its inductance and signal frequency which is **jwL**. This method is not so popular and is seldom employed.

#### **Transformer Coupling**

The coupling method that uses a **transformer** as the coupling device can be called as Transformer coupling. There is no capacitor used in this method of coupling because the transformer itself conveys the AC component directly to the base of second stage.

The secondary winding of the transformer provides a base return path and hence there is no need of base resistance. This coupling is popular for its efficiency and its impedance matching and hence it is mostly used.

#### **Direct Coupling**

If the previous amplifier stage is connected to the next amplifier stage directly, it is called as **direct coupling**. The individual amplifier stage bias conditions are so designed that the stages can be directly connected without DC isolation.

The direct coupling method is mostly used when the load is connected in series, with the output terminal of the active circuit element. For example, head-phones, loud speakers etc.

#### **Role of Capacitors in Amplifiers**

Other than the coupling purpose, there are other purposes for which few capacitors are especially employed in amplifiers. To understand this, let us know about the role of capacitors in Amplifiers.

#### The Input Capacitor Cin

The input capacitor  $C_{in}$  present at the initial stage of the amplifier, couples AC signal to the base of the transistor. This capacitor  $C_{in}$  if not present, the signal source will be in parallel to resistor  $R_2$  and the bias voltage of the transistor base will bechanged.

Hence C<sub>in</sub> allows, the AC signal from source to flow into input circuit, without affecting the bias conditions.

#### The Emitter By-pass Capacitor Ce

The emitter by-pass capacitor  $C_e$  is connected in parallel to the emitter resistor. It offers a low reactance path to the amplified AC signal.

In the absence of this capacitor, the voltage developed across  $R_E$  will feedback to the input side thereby reducing the output voltage. Thus in the presence of  $C_e$  the amplified AC will pass through this.

#### **Coupling Capacitor CC**

The capacitor  $C_C$  is the coupling capacitor that connects two stages and prevents DC interference between the stages and controls the operating point from shifting. This is also called as **blocking capacitor** because it does not allow the DC voltage to pass through it.

In the absence of this capacitor,  $R_C$  will come in parallel with the resistance  $R_1$  of the biasing network of the next stage and thereby changing the biasing conditions of the next stage.

#### **Amplifier Consideration**

For an amplifier circuit, the overall gain of the amplifier is an important consideration. To achieve maximum voltage gain, let us find the most suitable transistor configuration for cascading.

#### **CC** Amplifier

- Its voltage gain is less than unity.

- It is not suitable for intermediate stages.

#### **CB** Amplifier

- Its voltage gain is less than unity.

- Hence not suitable for cascading.

#### **CE Amplifier**

- Its voltage gain is greater than unity.

- Voltage gain is further increased by cascading.

The characteristics of CE amplifier are such that, this configuration is very suitable for cascading in amplifier circuits. Hence most of the amplifier circuits use CE configuration.

#### **Two Stage CE-CE Cascade Amplifier**

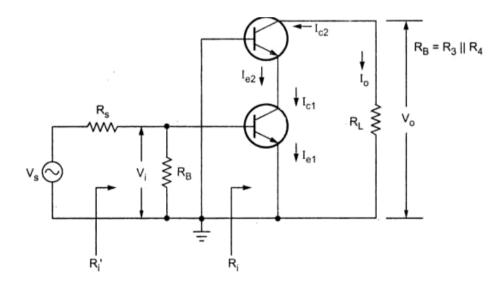

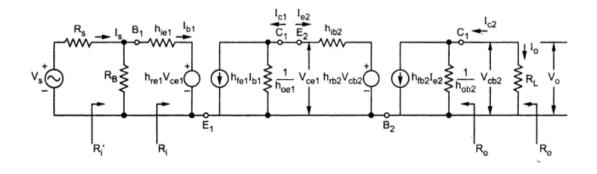

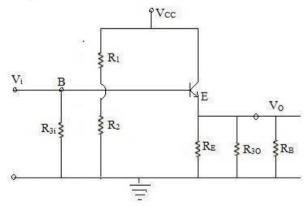

The impact of input and output loading can be minimized by cascading two amplifiers with appropriate input and output characteristics. Multistage cascading can be used to create amplifiers with high input resistance, low output resistance and large gains.

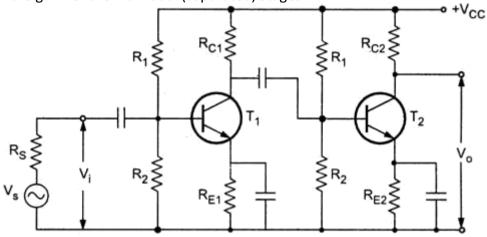

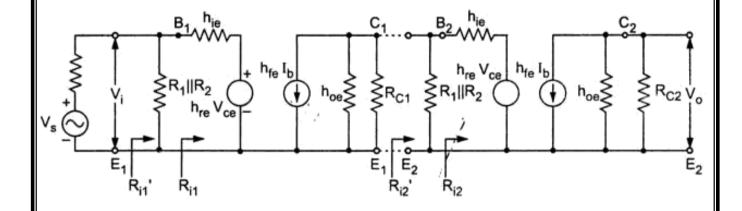

The complication in calculating the gain of cascaded stages comes from the non-ideal coupling between stages due to loading. Two cascaded common emitter stages are shown in below figure. Because the input resistance of the second stage (resistors  $R_1$  and  $R_2$ ) forms a voltage divider with the output resistance ( $R_{C1}$ ) of the first stage, the total gain is not simply the product of the gain for the individual (separated) stages.

#### h-parameter equivalent circuit

## **Cascode Amplifier**

## Cascode Amplifier

#### AC equivalent circuit

## h-parameter equivalent circuit

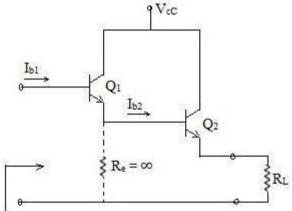

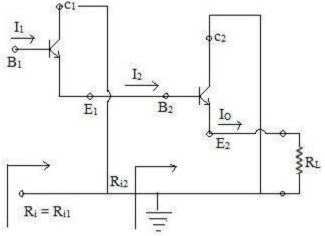

## **Darlington pair**

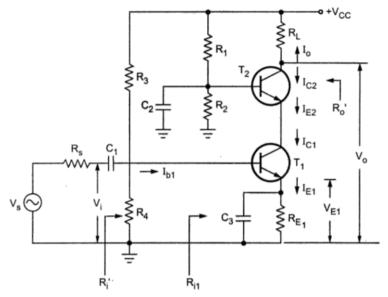

Darlington pair 1- Two emitter follower stages in cascade with infinite emitter resistance in the first stage constitute a Darlington circuit.

#### **Second Stage**

Let us assume , hoe RL< 0.1

$$A_{I_2} = \frac{I_o}{I_2} = 1 + h_{fe} \simeq h_{fe} - - - - (1)$$

$$R_{i2} = h_{ie} + (1+h_{fe}) R_L \sim h_{ie} + h_{fe} R_L h_{fe} R_L$$

(2)

$$R_{L1} = R_{i2} = h_{fe} R_{L}$$

(3)

#### **First Stage**

$h_{oe}R_{L1}$  =  $h_{oe}h_{fe}R_{L}$ < 0.1 . If this inequality is satisfied, then we can use simplified equivalent ckt in the first stage. Using exact solution

$$A_{I_1} = \frac{-h_{fe}}{1 + h_{oe}R_{L1}}$$

$$A_{I_{\text{1}}} = \frac{1 + h_{\text{fe}}}{1 + h_{\text{oe}} h_{\text{fe}} R_{L}} - - - - - - (4)$$

$$R_{i1} = h_{ie} + h_{rc} A_{i1} R_{L1}$$

$$= h_{ie} + \frac{h_{fe} \; h_{fe} \, R_L}{1 + h_{oe} \; h_{fe} R_L}$$

$$= h_{ie} + \frac{{h_{fe}}^2 R_L}{1 + h_{oe} h_{fe} R_L}$$

For emitter follower

$$R_i = h_{ie} + (1+h_{fe}) R_L$$

=  $h_{ie} + h_{fe} R_L$

Overall current gain

$$A_{I} = A_{1}A_{2} = \frac{h_{fe}^{2}}{1 + h_{oe}h_{fe}R_{L}}$$

Emitter follower,

$$A_{V} = \frac{1 - h_{ie}}{R_{L}} - - - - - - (1)$$

Darlington ckt ,  $A_V = A_{V1} A_{V2}$

$$=\frac{1-h_{ie\,2}}{R_{ie}}(2+h_{oe}h_{fe}R_{L})-----(2)$$

Effect of biasing network on the input resistance of emitter follower or Darlington ckt.

Effective input resistance  $R_i = R_1 \mid R_2 \mid R_i'$  where  $R_i'$  is a large input resistance of emitter follower or Darlington ckt.

$$R_i = R_B \mid R_i'$$

~ R<sub>B</sub>

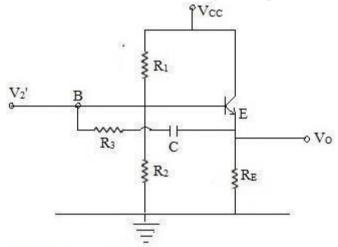

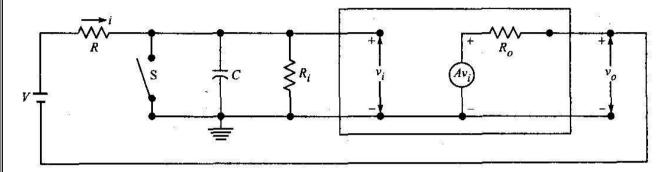

#### **Emitter follower with Boot Strap Biasing**

The reactance offered by the capacitor is very low for all frequencies.

$$A_V = \frac{V_o}{V_i}$$

$$\therefore \quad V_{o} = A_{V}V_{i} \approx V_{i}$$

R<sub>3</sub> can be replaced by Miller's theorem

$$R_{3i}=\frac{R_3}{1-A_V}=\infty$$

$$R_{30} = \frac{R_3}{1 - 1/A_V} = \frac{R_3 A_V}{A_V - 1}$$

Effective output resistance

$$R_L = R_O \mid \mid R_{3O} \mid \mid R_B$$

$$\approx R_O$$

#### **Coupling Schemes**

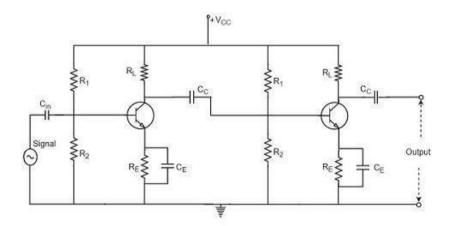

#### **Two-stage RC Coupled Amplifier**

The resistance-capacitance coupling is, in short termed as RC coupling. This is the mostly used coupling technique in amplifiers.

#### **Construction of a Two-stage RC Coupled Amplifier**

The constructional details of a two-stage RC coupled transistor amplifier circuit are as follows. The two stage amplifier circuit has two transistors, connected in CE configuration and a common power supply  $V_{CC}$  is used. The potential divider network  $R_1$  and  $R_2$  and the resistor  $R_e$  form the biasing and stabilization network. The emitter by-pass capacitor  $C_e$  offers a low reactance path to the signal.

The resistor  $R_L$  is used as a load impedance. The input capacitor  $C_{in}$  present at the initial stage of the amplifier couples AC signal to the base of the transistor. The capacitor  $C_C$  is the coupling capacitor that connects two stages and prevents DC interference between the stages and controls the shift of operating point. The figure below shows the circuit diagram of RC coupled amplifier.

#### **Operation of RC Coupled Amplifier**

When an AC input signal is applied to the base of first transistor, it gets amplified and appears at the collector load  $R_L$  which is then passed through the coupling capacitor  $C_C$  to the next stage. This becomes the input of the next stage, whose amplified output again appears across its collector load. Thus the signal is amplified in stage by stage action.

The important point that has to be noted here is that the total gain is less than the product of the gains of individual stages. This is because when a second stage is made to follow the first stage, the **effective load resistance** of the first stage is reduced due to the shunting

effect of the input resistance of the second stage. Hence, in a multistage amplifier, only the gain of the last stage remains unchanged.

As we consider a two stage amplifier here, the output phase is same as input. Because the phase reversal is done two times by the two stage CE configured amplifier circuit.

#### **Frequency Response of RC Coupled Amplifier**

Frequency response curve is a graph that indicates the relationship between voltage gain and function of frequency. The frequency response of a RC coupled amplifier is as shown in the following graph.

From the above graph, it is understood that the frequency rolls off or decreases for the frequencies below 50Hz and for the frequencies above 20 KHz. whereas the voltage gain for the range of frequencies between 50Hz and 20 KHz is constant.

We know that.

$$X_c=1/2\pi f_c$$

It means that the capacitive reactance is inversely proportional to the frequency.

#### At Low frequencies (i.e. below 50 Hz)

The capacitive reactance is inversely proportional to the frequency. At low frequencies, the reactance is quite high. The reactance of input capacitor  $C_{in}$  and the coupling capacitor  $C_{C}$  are so high that only small part of the input signal is allowed. The reactance of the emitter by pass capacitor  $C_{E}$  is also very high during low frequencies. Hence it cannot shunt the emitter resistance effectively. With all these factors, the voltage gain rolls off at low frequencies.

At High frequencies (i.e. above 20 KHz): Again considering the same point, we know that the capacitive reactance is low at high frequencies. So, a capacitor behaves as a short

circuit, at high frequencies. As a result of this, the loading effect of the next stage increases, which reduces the voltage gain. Along with this, as the capacitance of emitter diode decreases, it increases the base current of the transistor due to which the current gain  $(\beta)$  reduces. Hence the voltage gain rolls off at high frequencies.

#### At Mid-frequencies (i.e. 50 Hz to 20 KHz)

The voltage gain of the capacitors is maintained constant in this range of frequencies, as shown in figure. If the frequency increases, the reactance of the capacitor  $C_C$  decreases which tends to increase the gain. But this lower capacitance reactive increases the loading effect of the next stage by which there is a reduction in gain.

Due to these two factors, the gain is maintained constant.

#### AdvantagesofRC Coupled Amplifier

The following are the advantages of RC coupled amplifier.

- The frequency response of RC amplifier provides constant gain over a wide frequency range, hence most suitable for audio applications.

- The circuit is simple and has lower cost because it employs resistors and capacitors which are cheap.

- It becomes more compact with the upgrading technology.

#### DisadvantagesofRC CoupledAmplifier

The following are the disadvantages of RC coupled amplifier.

- The voltage and power gain are low because of the effective load resistance.

- They become noisy with age.

- Due to poor impedance matching, power transfer will be low.

#### ApplicationsofRC CoupledAmplifier

The following are the applications of RC coupled amplifier.

- They have excellent audio fidelity over a wide range of frequency.

- Widely used as Voltage amplifiers

- Due to poor impedance matching, RC coupling is rarely used in the final stages.

#### Frequency response

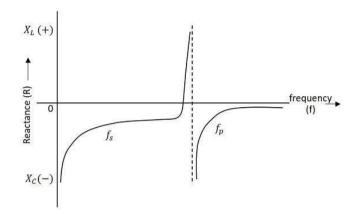

The frequency response of a crystal is as shown below. The graph shows the reactance  $(X_L \text{ or } X_C)$  versus frequency (f). It is evident that the crystal has two closely spaced resonant frequencies.

The first one is the series resonant frequency ( $f_s$ ), which occurs when reactance of the inductance (L) is equal to the reactance of the capacitance C. In that case, the impedance of the equivalent circuit is equal to the resistance R and the frequency of oscillation is given by the relation,

$$f = \frac{1}{2\pi\sqrt{L.\,C}}$$

The second one is the parallel resonant frequency ( $f_p$ ), which occurs when the reactance of R-L-C branch is equal to the reactance of capacitor  $C_m$ . At this frequency, the crystal offers a very high impedance to the external circuit and the frequency of oscillation is given by the relation.

$$f_p = rac{1}{2\pi \sqrt{L.\,C_T}}$$

Where

$$C_T = \frac{CC_m}{(C+C_m)}$$

The value of  $C_m$  is usually very large as compared to  $C_m$ . Therefore, the value of  $C_m$  is approximately equal to  $C_m$  and hence the series resonant frequency is approximately equal to the parallel resonant frequency (i.e.,  $f_s = f_p$ ).

# UNIT-III LARGE SIGNAL AMPLIFIERS

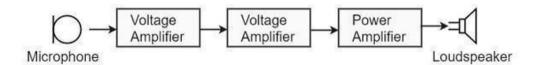

In practice, any amplifier consists of few stages of amplification. If we consider audio amplification, it has several stages of amplification, depending upon our requirement.

#### **Power Amplifier**

After the audio signal is converted into electrical signal, it has several voltage amplifications done, after which the power amplification of the amplified signal is done just before the loud speaker stage. This is clearly shown in the below figure.

While the voltage amplifier raises the voltage level of the signal, the power amplifier raises the power level of the signal. Besides raising the power level, it can also be said that a power amplifier is a device which converts DC power to AC power and whose action is controlled by the input signal.

The DC power is distributed according to the relation, DC

power input = AC power output + losses

#### **Power Transistor**

For such Power amplification, a normal transistor would not do. A transistor that is manufactured to suit the purpose of power amplification is called as a **Power transistor**.

A Power transistor differs from the other transistors, in the following factors.

- It is larger in size, in order to handle large powers.

- The collector region of the transistor is made large and a heat sink is placed at the collector-base junction in order to minimize heat generated.

- The emitter and base regions of a power transistor are heavily doped.

- Due to the low input resistance, it requires low input power.

Hence there is a lot of difference in voltage amplification and power amplification. So, let us now try to get into the details to understand the differences between a voltage amplifier and a power amplifier.

#### **Difference between Voltage and Power Amplifiers:**

Let us try to differentiate between voltage and power amplifier.

#### **Voltage Amplifier**

The function of a voltage amplifier is to raise the voltage level of the signal. A voltage

amplifier is designed to achieve maximum voltage amplification.

The voltage gain of an amplifier is given by

$Av=\theta(Rc/Rin)$

The characteristics of a voltage amplifier are as follows -

- The base of the transistor should be thin and hence the value of  $\beta$  should be greater than 100.

- The resistance of the input resistor  $R_{in}$  should be low when compared to collector load  $R_{\rm C}$ .

- The collector load R<sub>C</sub> should be relatively high. To permit high collector load, the voltage amplifiers are always operated at low collector current.

- The voltage amplifiers are used for small signal voltages.

#### **Power Amplifier**

The function of a power amplifier is to raise the power level of input signal. It is required to deliver a large amount of power and has to handle large current.

The characteristics of a power amplifier are as follows –

- The base of transistor is made thicken to handle large currents. The value of  $\beta$  being ( $\beta$  > 100) high.

- The size of the transistor is made larger, in order to dissipate more heat, which is produced during transistor operation.

- Transformer coupling is used for impedance matching.

- Collector resistance is made low.

The comparison between voltage and power amplifiers is given below in a tabular form.

| S.No | Particular        | Voltage Amplifier    | Power Amplifier                 |

|------|-------------------|----------------------|---------------------------------|

| 1    | β                 | High (>100)          | Low (5 to 20)                   |

| 2    | Rc                | High (4-10 KΩ)       | Low (5 to 20 Ω)                 |

| 3    | Coupling          | Usually R-C coupling | Invariably transformer coupling |

| 4    | Input voltage     | Low (a few m V)      | High (2-4 V)                    |

| 5    | Collector current | Low (≈ 1 mA)         | High (> 100 mA)                 |

| 6    | Power output      | Low                  | High                            |

| 7    | Output impendence | High (≈ 12 K Ω)      | Low (200 Ω                      |

The Power amplifiers amplify the power level of the signal. This amplification is done in the last stage in audio applications. The applications related to radio frequencies employ radio power amplifiers. But the **operating point** of a transistor plays a very important role in determining the efficiency of the amplifier. The **main classification** is done based on this mode of operation.

The classification is done based on their frequencies and also based on their mode of operation.

# **Classification Based on Frequencies**

Power amplifiers are divided into two categories, based on the frequencies they handle. They are as follows.

- Audio Power Amplifiers The audio power amplifiers raise the power level of signals that have audio frequency range (20 Hz to 20 KHz). They are also known as Small signal power amplifiers.

- Radio Power Amplifiers Radio Power Amplifiers or tuned power amplifiers raise

the power level of signals that have radio frequency range (3 KHz to 300 GHz). They

are also known as large signal power amplifiers.

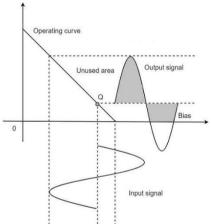

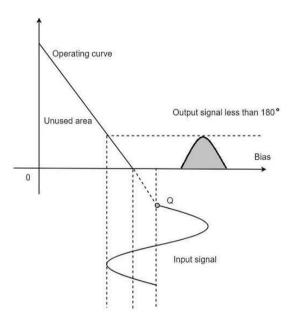

# **Classification Based on Mode of Operation**

On the basis of the mode of operation, i.e., the portion of the input cycle during which collector current flows, the power amplifiers may be classified as follows.

- Class A Power amplifier When the collector current flows at all times during the full cycle of signal, the power amplifier is known as class A power amplifier.

- Class B Power amplifier When the collector current flows only during the positive half cycle of the input signal, the power amplifier is known as class B power amplifier.

- Class C Power amplifier When the collector current flows for less than half cycle of the input signal, the power amplifier is known as class C power amplifier.

There forms another amplifier called Class AB amplifier, if we combine the class A and class B amplifiers so as to utilize the advantages of both. Before going into the details of these amplifiers, let us have a look at the important terms that have to be considered to determine the efficiency of an amplifier.

#### **Terms Considering Performance**

The primary objective of a power amplifier is to obtain maximum output power. In order to

achieve this, the important factors to be considered are collector efficiency, power dissipation capability and distortion. Let us go through them in detail.

#### **Collector Efficiency**

This explains how well an amplifier converts DC power to AC power. When the DC supply is given by the battery but no AC signal input is given, the collector output at such a condition is observed as **collector efficiency**.

The collector efficiency is defined as

$\eta$ =average a.c poweroutput / average d.c powerinputtotransisto

The main aim of a power amplifier is to obtain maximum collector efficiency. Hence the higher the value of collector efficiency, the efficient the amplifier will be.

#### **Power Dissipation Capacity**

Every transistor gets heated up during its operation. As a power transistor handles large currents, it gets more heated up. This heat increases the temperature of the transistor, which alters the operating point of the transistor. So, in order to maintain the operating point stability, the temperature of the transistor has to be kept in permissible limits. For this, the heat produced has to be dissipated. Such a capacity is called as Power dissipation capability.

**Power dissipation capability** can be defined as the ability of a power transistor to dissipate the heat developed in it. Metal cases called heat sinks are used in order to dissipate the heat produced in power transistors.

#### Distortion

A transistor is a non-linear device. When compared with the input, there occur few variations in the output. In voltage amplifiers, this problem is not pre-dominant as small currents are used. But in power amplifiers, as large currents are in use, the problem of distortion certainly arises.

**Distortion** is defined as the change of output wave shape from the input wave shape of the amplifier. An amplifier that has lesser distortion produces a better output and hence considered efficient.

We have already come across the details of transistor biasing, which is very important for the operation of a transistor as an amplifier. Hence to achieve faithful amplification, the biasing of the transistor has to be done such that the amplifier operates over the linear region.

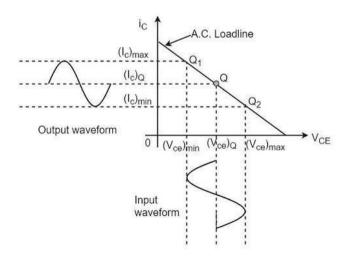

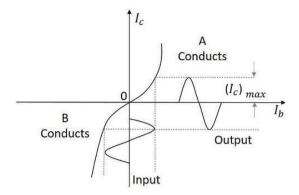

A Class A power amplifier is one in which the output current flows for the entire cycle of the AC input supply. Hence the complete signal present at the input is amplified at the output. The following figure shows the circuit diagram for Class A Power amplifier.

From the above figure, it can be observed that the transformer is present at the collector as a load. The use of transformer permits the impedance matching, resulting in the transference of maximum power to the load e.g. loud speaker.

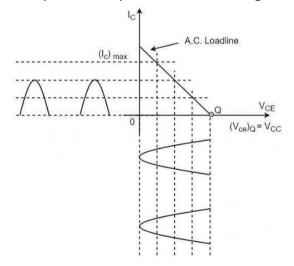

The operating point of this amplifier is present in the linear region. It is so selected that the current flows for the entire ac input cycle. The below figure explains the selection of operating point.

The output characteristics with operating point Q is shown in the figure above. Here  $(I_c)_Q$  and  $(V_{ce})_Q$  represent no signal collector current and voltage between collector and emitter respectively. When signal is applied, the Q-point shifts to  $Q_1$  and  $Q_2$ . The output current increases to  $(I_c)_{max}$  and decreases to  $(I_c)_{min}$ . Similarly, the collector-emitter voltage increases to  $(V_{ce})_{max}$  and decreases to  $(V_{ce})_{min}$ .

D.C. Power drawn from collector battery V<sub>cc</sub> is given by

$$Pin=voltage \times current = V_{CC}(I_C)_Q$$

This power is used in the following two parts -

Power dissipated in the collector load as heat is given by

$$P_{RC}$$

=(current)<sup>2</sup>×resistance=(IC)<sup>2</sup> $_{Q}R_{C}$

Power given to transistor is given by

$$P_{tr}=P_{in}-P_{RC}=V_{CC}-(I_C)_{2Q}R_C$$

When signal is applied, the power given to transistor is used in the following two parts –

A.C. Power developed across load resistors RC which constitutes the a.c. power output.

$$(P_O)ac=I^2R_C=V^2/R_C=(V_m/V_2)/R_C=V_2m/2R_C$$

- Where I is the R.M.S. value of a.c. output current through load, V is the R.M.S. value of a.c. voltage, and  $V_m$  is the maximum value of V.

- The D.C. power dissipated by the transistor (collector region) in the form of heat, i.e.,

(Pc)<sub>dc</sub>

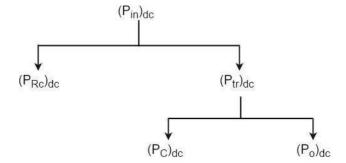

We have represented the whole power flow in the following diagram.

This class A power amplifier can amplify small signals with least distortion and the output will be an exact replica of the input with increased strength.

# Let us now try to draw some expressions to represent efficiencies.

#### Overall Efficiency

The overall efficiency of the amplifier circuit is given by

$$(\eta)_{overall} = rac{a.\ c\ power\ delivered\ to\ the\ load}{total\ power\ delivered\ by\ d.\ c\ supply}$$

$$= rac{(P_O)_{ac}}{(P_{in})_{dc}}$$

# Collector Efficiency

The collector efficiency of the transistor is defined as

$$(\eta)_{collector} = rac{average~a.~c~power~output}{average~d.~c~power~input~to~transistor} \ = rac{(P_O)_{ac}}{(P_{tr})_{dc}}$$

Expression for overall efficiency

$$\begin{split} (P_O)_{ac} &= V_{rms} \times I_{rms} \\ &= \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max} - (V_{ce})_{min}}{2} \right] \times \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max} - (I_C)_{min}}{2} \right] \\ &= \frac{\left[ (V_{ce})_{max} - (V_{ce})_{min} \right] \times \left[ (I_C)_{max} - (I_C)_{min} \right]}{8} \end{split}$$

# **Advantages of Class A Amplifiers**

The advantages of Class A power amplifier are as follows -

- The current flows for complete input cycle

- It can amplify small signals

- The output is same as input

- No distortion is present

#### **Disadvantages of Class A Amplifiers**

The advantages of Class A power amplifier are as follows -

- Low power output

- Low collector efficiency

The class A power amplifier as discussed in the previous chapter, is the circuit in which the output current flows for the entire cycle of the AC input supply. We also have learnt about the

disadvantages it has such as low output power and efficiency. In order to minimize those effects, the transformer coupled class A power amplifier has been introduced.

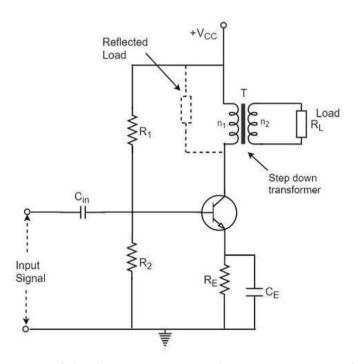

The **construction of class A power amplifier** can be understood with the help of below figure. This is similar to the normal amplifier circuit but connected with a transformer in the collector load.

Here  $R_1$  and  $R_2$  provide potential divider arrangement. The resistor Re provides stabilization,  $C_e$  is the bypass capacitor and  $R_e$  to prevent a.c. voltage. The transformer used here is a step-down transformer. The high impedance primary of the transformer is connected to the high impedance collector circuit. The low impedance secondary is connected to the load (generally loud speaker).

#### **Transformer Action:**

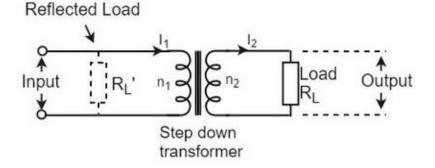

The transformer used in the collector circuit is for impedance matching.  $R_L$  is the load connected in the secondary of a transformer.  $R_L'$  is the reflected load in the primary of the transformer.

The number of turns in the primary are  $n_1$  and the secondary are  $n_2$ . Let  $V_1$  and  $V_2$  be the primary and secondary voltages and  $I_1$  and  $I_2$  be the primary and secondary currents respectively. The below figure shows the transformer clearly.

We know that

$$\frac{V_1}{V_2} = \frac{n_1}{n_2} \ and \ \frac{I_1}{I_2} = \frac{n_1}{n_2}$$

Or

$$V_1 = \frac{n_1}{n_2} V_2 \ and I_1 = \frac{n_1}{n_2} I_2$$

Hence

$$rac{V_1}{I_1} = \left(rac{n_1}{n_2}

ight)^2 rac{V_2}{I_2}$$

But  $V_1/I_1 = R_L' = effective input resistance$

And  $V_2/I_2 = R_L = effective$  output resistance

Therefore,

$$R_L' = \left(\frac{n_1}{n_2}\right)^2 R_L = n^2 R_L$$

Where

$$n = \frac{number\ of\ turns\ in\ primary}{number\ of\ turns\ in\ secondary} = \frac{n_1}{n_2}$$

A power amplifier may be matched by taking proper turn ratio in step down transformer.

# **Circuit Operation**

If the peak value of the collector current due to signal is equal to zero signal collector current, then the maximum a.c. power output is obtained. So, in order to achieve complete amplification, the operating point should lie at the center of the load line.

The operating point obviously varies when the signal is applied. The collector voltage varies in opposite phase to the collector current. The variation of collector voltage appears across the primary of the transformer.

# **Circuit Analysis**

The power loss in the primary is assumed to be negligible, as its resistance is very small.

The input power under dc condition will be

$$(P_{in})_{dc} = (P_{tr})_{dc} = V_{CC} \times (I_C)_Q$$

Under maximum capacity of class A amplifier, voltage swings from  $(V_{\text{Ce}})_{\text{max}}$  to zero and current from  $(I_{\text{c}})_{\text{max}}$  to zero.

Hence

$$\begin{split} V_{rms} &= \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max} - (V_{ce})_{min}}{2} \right] = \frac{1}{\sqrt{2}} \left[ \frac{(V_{ce})_{max}}{2} \right] = \frac{2V_{CC}}{2\sqrt{2}} \\ &= \frac{V_{CC}}{\sqrt{2}} \end{split}$$

$$\begin{split} I_{rms} &= \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max} - (I_C)_{min}}{2} \right] = \frac{1}{\sqrt{2}} \left[ \frac{(I_C)_{max}}{2} \right] = \frac{2(I_C)_Q}{2\sqrt{2}} \\ &= \frac{(I_C)_Q}{\sqrt{2}} \end{split}$$

Therefore,

$$(P_O)_{ac} = V_{rms} \times I_{rms} = \frac{V_{CC}}{\sqrt{2}} \times \frac{(I_C)_Q}{\sqrt{2}} = \frac{V_{CC} \times (I_C)_Q}{2}$$

Therefore,

Collector Efficiency =

$$\frac{(Po)_{ac}}{(P_{tr})_{dc}}$$

Or,

$$\begin{split} (\eta)_{collector} &= \frac{V_{CC} \times (I_C)_Q}{2 \times V_{CC} \times (I_C)_Q} = \frac{1}{2} \\ &= \frac{1}{2} \times 100 = 50\% \end{split}$$

The efficiency of a class A power amplifier is nearly than 30% whereas it has got improved to 50% by using the transformer coupled class A power amplifier.

# **Advantages**

The advantages of transformer coupled class A power amplifier are as follows.

- No loss of signal power in the base or collector resistors.

- Excellent impedance matching is achieved.

- · Gain is high.

- DC isolation is provided.

#### Disadvantages

The disadvantages of transformer coupled class A power amplifier are as follows.

• Low frequency signals are less amplified comparatively.

- Hum noise is introduced by transformers.

- Transformers are bulky and costly.

- Poor frequency response.

#### **Applications**

The applications of transformer coupled class A power amplifier are as follows.

- This circuit is where impedance matching is the main criterion.

- These are used as driver amplifiers and sometimes as output amplifiers.

- When the collector current flows only during the positive half cycle of the input signal, the power amplifier is known as class B power amplifier.

# **Class B Operation**

The biasing of the transistor in class B operation is in such a way that at zero signal condition, there will be no collector current. The **operating point** is selected to be at collector cut off voltage. So, when the signal is applied, **only the positive half cycle** is amplified at the output.

The figure below shows the input and output waveforms during class B operation.

When the signal is applied, the circuit is forward biased for the positive half cycle of the input and hence the collector current flows. But during the negative half cycle of the input, the circuit is reverse biased and the collector current will be absent. Hence **only the positive half cycle** is amplified at the output.

As the negative half cycle is completely absent, the signal distortion will be high. Also, when the applied signal increases, the power dissipation will be more. But when compared to class A power amplifier, the output efficiency is increased. Well, in order to minimize the disadvantages and achieve low distortion, high efficiency and high output power, the push-pull configuration is used in this class B amplifier.

# **Class B Push-Pull Amplifier**

Though the efficiency of class B power amplifier is higher than class A, as only one half cycle of the input is used, the distortion is high. Also, the input power is not completely utilized. In order to compensate these problems, the push-pull configuration is introduced in class B amplifier.

#### **Construction:**

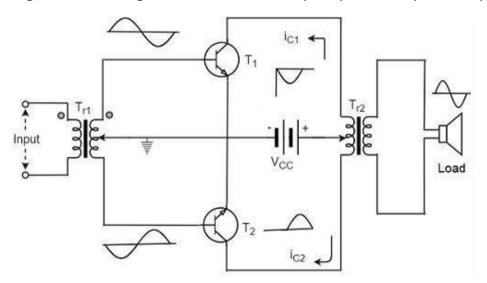

The circuit of a push-pull class B power amplifier consists of two identical transistors  $T_1$  and  $T_2$  whose bases are connected to the secondary of the center-tapped input transformer  $T_{r1}$ . The emitters are shorted and the collectors are given the  $V_{CC}$  supply through the primary of the output transformer  $T_{r2}$ .

The circuit arrangement of class B push-pull amplifier, is same as that of class A push-pull amplifier except that the transistors are biased at cut off, instead of using the biasing resistors. The figure below gives the detailing of the construction of a push-pull class B power amplifier.

The circuit operation of class B push pull amplifier is detailed below.

#### **Operation**

The circuit of class B push-pull amplifier shown in the above figure clears that both the transformers are center-tapped. When no signal is applied at the input, the transistors  $T_1$  and  $T_2$  are in cut off condition and hence no collector currents flow. As no current is drawn from  $V_{CC}$ , no power is wasted.

When input signal is given, it is applied to the input transformer  $T_{r1}$  which splits the signal into two signals that are  $180^{\circ}$  out of phase with each other. These two signals are given to the two identical transistors  $T_1$  and  $T_2$ . For the positive half cycle, the base of the transistor  $T_1$  becomes positive and collector current flows. At the same time, the transistor  $T_2$  has negative half cycle, which throws the transistor  $T_2$  into cutoff condition and hence no collector current flows. The waveform is produced as shown in the following figure.

For the next half cycle, the transistor  $T_1$  gets into cut off condition and the transistor  $T_2$  gets into conduction, to contribute the output. Hence for both the cycles, each transistor conducts alternately. The output transformer  $T_{r3}$  serves to join the two currents producing an almost undistorted output waveform.

#### **Power Efficiency of Class B Push-Pull Amplifier**

The current in each transistor is the average value of half sine loop. For half sine loop,  $I_{dc}$  is given by  $I_{dc} = \frac{(I_C)_{max}}{\pi}$

Therefore,

$$(p_{in})_{dc} = 2 imes \left[rac{(I_C)_{max}}{\pi} imes V_{CC}

ight]$$

Here factor 2 is introduced as there are two transistors in push-pull amplifier.

R.M.S. value of collector current =  $(I_C)_{max}/\sqrt{2}$

R.M.S. value of output voltage =  $V_{CC}/\sqrt{2}$

Under ideal conditions of maximum power

Therefore,

$$(P_O)_{ac} = rac{(I_C)_{max}}{\sqrt{2}} imes rac{V_{CC}}{\sqrt{2}} = rac{(I_C)_{max} imes V_{CC}}{2}$$

Now overall maximum efficiency

$$egin{aligned} \eta_{overall} &= rac{(P_O)_{ac}}{(P_{in})_{dc}} \ &= rac{(I_C)_{max} imes V_{CC}}{2} imes rac{\pi}{2(I_C)_{max} imes V_{CC}} \ &= rac{\pi}{4} = 0.785 = 78.5\% \end{aligned}$$

The collector efficiency would be the same.

Hence the class B push-pull amplifier improves the efficiency than the class A push-pull amplifier.

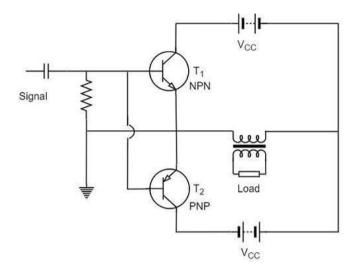

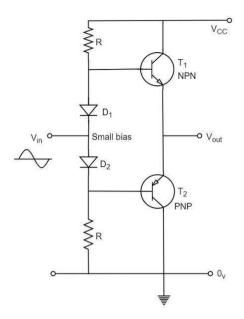

# **Complementary Symmetry Push-Pull Class B Amplifier**

The push pull amplifier which was just discussed improves efficiency but the usage of center-tapped transformers makes the circuit bulky, heavy and costly. To make the circuit simple and to improve the efficiency, the transistors used can be complemented, as shown in the following circuit diagram.

The above circuit employs a NPN transistor and a PNP transistor connected in push pull configuration. When the input signal is applied, during the positive half cycle of the input signal, the NPN transistor conducts and the PNP transistor cuts off. During the negative half cycle, the NPN transistor cuts off and the PNP transistor conducts.

In this way, the NPN transistor amplifies during positive half cycle of the input, while PNP transistor amplifies during negative half cycle of the input. As the transistors are both complement to each other, yet act symmetrically while being connected in push pull configuration of class B, this circuit is termed as **Complementary symmetry push pull class B amplifier**.

#### **Advantages**

The advantages of Complementary symmetry push pull class B amplifier are as follows.

- As there is no need of center tapped transformers, the weight and cost are reduced.

- Equal and opposite input signal voltages are not required.

# **Disadvantages**

The disadvantages of Complementary symmetry push pull class B amplifier are as follows.

- It is difficult to get a pair of transistors (NPN and PNP) that have similar characteristics.

- We require both positive and negative supply voltages.

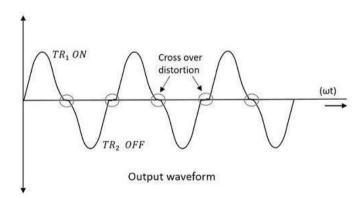

The class A and class B amplifier so far discussed has got few limitations. Let us now try to combine these two to get a new circuit which would have all the advantages of both class A and class B amplifier without their inefficiencies. Before that, let us also go through another important problem, called as **Cross over distortion**, the output of class B encounters with.

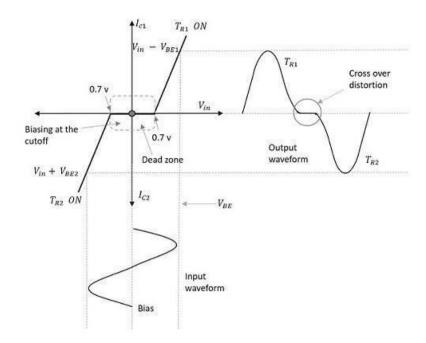

#### **Cross-over Distortion:**

In the push-pull configuration, the two identical transistors get into conduction, one after the other and the output produced will be the combination of both.

When the signal changes or crosses over from one transistor to the other at the zero voltage point, it produces an amount of distortion to the output wave shape. For a transistor in order to conduct, the base emitter junction should cross 0.7v, the cut off voltage. The time taken for a transistor to get ON from OFF or to get OFF from ON state is called the **transition period**.

At the zero voltage point, the transition period of switching over the transistors from one to the other, has its effect which leads to the instances where both the transistors are OFF at a time. Such instances can be called as **Flat spot** or **Dead band** on the output wave shape.

The above figure clearly shows the cross over distortion which is prominent in the output waveform. This is the main disadvantage. This cross over distortion effect also reduces the overall peak to peak value of the output waveform which in turn reduces the maximum power output. This can be more clearly understood through the non-linear characteristic of the waveform as shown below.

It is understood that this cross-over distortion is less pronounced for large input signals, where as it causes severe disturbance for small input signals. This cross over distortion can be eliminated if the conduction of the amplifier is more than one half cycle, so that both the transistors won't be OFF at the same time.

This idea leads to the invention of class AB amplifier, which is the combination of both class A and class B amplifiers, as discussed below.

# **Class AB Power Amplifier**

As the name implies, class AB is a combination of class A and class B type of amplifiers. As class A has the problem of low efficiency and class B has distortion problem, this class AB is emerged to eliminate these two problems, by utilizing the advantages of both the classes.

The cross over distortion is the problem that occurs when both the transistors are OFF at the same instant, during the transition period. In order to eliminate this, the condition has to be chosen for more than one half cycle. Hence, the other transistor gets into conduction, before the operating transistor switches to cut off state. This is achieved only by using class AB configuration, as shown in the following circuit diagram.

Therefore, in class AB amplifier design, each of the push-pull transistors is conducting for slightly more than the half cycle of conduction in class B, but much less than the full cycle of conduction of class A.

The conduction angle of class AB amplifier is somewhere between 180° to 360° depending upon the operating point selected. This is understood with the help of below figure.

The small bias voltage given using diodes  $D_1$  and  $D_2$ , as shown in the above figure, helps the operating point to be above the cutoff point. Hence the output waveform of class AB results as seen in the above figure. The crossover distortion created by class B is overcome by this class AB, as well the inefficiencies of class A and B don't affect the circuit.

So, the class AB is a good compromise between class A and class B in terms of efficiency and linearity having the efficiency reaching about 50% to 60%. The class A, B and AB amplifiers are called as **linear amplifiers** because the output signal amplitude and phase are linearly related to the input signal amplitude and phase.

# **Class C Power Amplifier**

When the collector current flows for less than half cycle of the input signal, the power amplifier is known as **class C power amplifier**. The efficiency of class C amplifier is high while linearity is poor. The conduction angle for class C is less than 180°. It is generally around 90°, which means the transistor remains idle for more than half of the input signal. So, the output current will be delivered for less time compared to the application of input signal.

The following figure shows the operating point and output of a class C amplifier.

This kind of biasing gives a much improved efficiency of around 80% to the amplifier, but introduces heavy distortion in the output signal. Using the class C amplifier, the pulses produced at its output can be converted to complete sine wave of a particular frequency by using LC circuits in its collector circuit.

The types of amplifiers that we have discussed so far cannot work effectively at radio frequencies, even though they are good at audio frequencies. Also, the gain of these amplifiers is such that it will not vary according to the frequency of the signal, over a wide range. This allows the amplification of the signal equally well over a range of frequencies and does not permit the selection of particular desired frequency while rejecting the other frequencies.

# **Single Tuned Amplifier**

An amplifier circuit with a single tuner section being at the collector of the amplifier circuit is called as Single tuner amplifier circuit.

#### Construction

A simple transistor amplifier circuit consisting of a parallel tuned circuit in its collector load, makes a single tuned amplifier circuit. The values of capacitance and inductance of the tuned circuit are selected such that its resonant frequency is equal to the frequency to be amplified.

The following circuit diagram shows a single tuned amplifier circuit.

The output can be obtained from the coupling capacitor  $C_{\text{C}}$  as shown above or from a secondary winding placed at L.

#### **Operation**

The high frequency signal that has to be amplified is applied at the input of the amplifier. The resonant frequency of the parallel tuned circuit is made equal to the frequency of the signal applied by altering the capacitance value of the capacitor C, in the tuned circuit. At this stage, the tuned circuit offers high impedance to the signal frequency, which helps to offer high output across the tuned circuit. As high impedance is offered only for the tuned frequency, all the other frequencies which get lower impedance are rejected by the tuned circuit. Hence the tuned amplifier selects and amplifies the desired frequency signal.

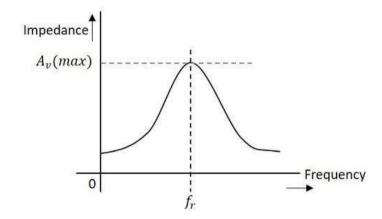

# **Frequency Response**

The parallel resonance occurs at resonant frequency  $f_r$  when the circuit has a high Q. the resonant frequency  $f_r$  is given by

$$fr=1/\sqrt{2\pi LC}$$

The following graph shows the frequency response of a single tuned amplifier circuit.

At resonant frequency  $f_r$  the impedance of parallel tuned circuit is very high and is purely resistive. The voltage across  $R_L$  is therefore maximum, when the circuit is tuned to resonant frequency. Hence the voltage gain is maximum at resonant frequency and drops off above and below it. The higher the Q, the narrower will the curve be.

# **Stagger Tuning**

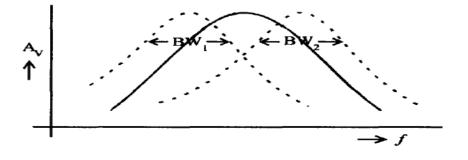

Tuned amplifiers have large gain, since at resonance, Z is maximum. So Av is maximum. To get this large Av over a wide range of frequencies, stagger tuned amplifiers are employed. This is done by taking two single tuned circuits of a certain Bandwidth, and displacing or staggering their resonance peaks by an amount equal to their Bandwidth. The resultant staggered pair will have a Bandwidth,  $\sqrt{2}$  times as great as that of each of individual pairs.

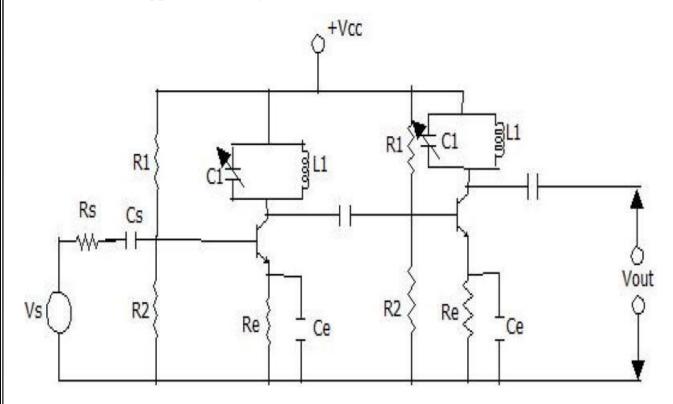

The circuit of stagger tuned amplifier is as shown below:

Stagger Tuned Amplifiers are used to improve the overall frequency response of tuned Amplifiers. Stagger tuned Amplifiers are usually designed so that the overall response exhibits maximal flatness around the centre frequency.

It needs a number of tuned circuit operating in union. The overall frequency response of a Stagger tuned amplifier is obtained by adding the individual response together. Since the resonant Frequencies of different tuned circuits are displaced or staggered, they are referred as Stagger Tuned Amplifier.

The main advantage of stagger tuned amplifier is increased bandwidth. Its Drawback is Reduced Selectivity and critical tuning of many tank circuits. They are used in RF amplifier stage in Radio Receivers.

The stagger tuning in this circuit is achieved by resonating the tuned circuits L1 C1, L2 C2 to slightly different Frequencies

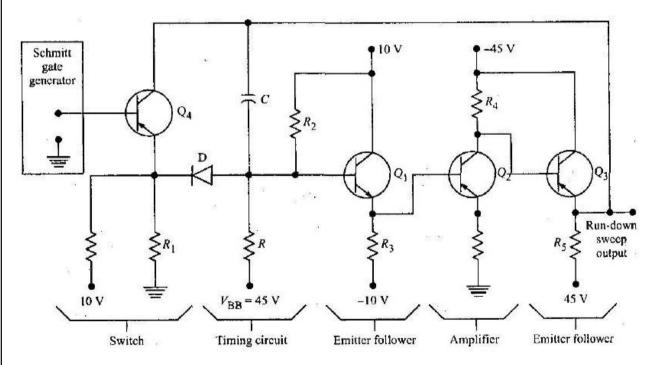

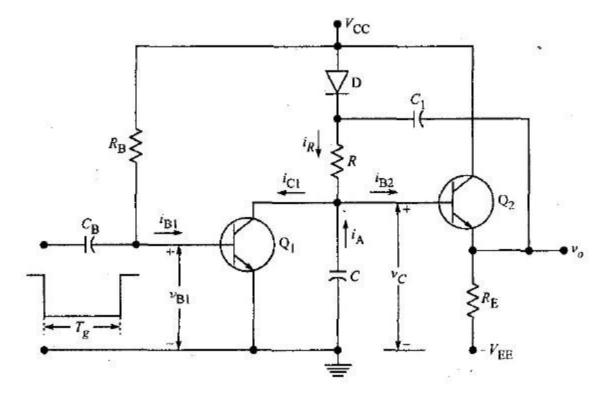

# UNIT IV MULTIVIBRATORS

#### TRANSISTOR AS A SWITCH

A transistor can be used as a switch. It has three regions of operation. When both Emitter-to-base and collector-base junctions are reverse biased, the transistor operates in the cut-off region and it acts as an open switch. When the emitter base junction is forward biased and the Collector base junction is reverse biased, it operates in the active region and acts as auf amplifier. When both the emitter-base and collector-base junctions are forward biased, it Operates in the saturation region and acts as a closed switch. When the transistor is switched! from cut-off to saturation and from saturation to cut-off with negligible active region, the transistor is operated as a switch. When the transistor is in saturation, junction voltages are'i very small but the operating currents are large. When the transistor is in cut-off, the currents\* are zero (except small leakage current) but the junction voltages are large.

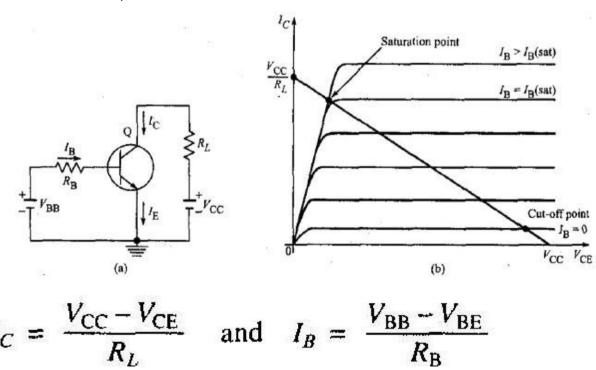

In Below Figure the transistor Q can be used to connect and disconnect the load *RL* from the source Vcc When Q is saturated it is like a closed switch from collector to emitter and when Q is cutoff it is like an open switch from collector to emitter.

Referring to the output characteristics shown in Figure (b), the region below the IB = 0 curve is the cut-off region. The intersection of the load line with IB = 0 curve is the cut-off point. At this point, the base current is zero and the collector current is negligible. The emitter diode comes out of forward bias and the normal transistor action is lost, i.e, VCE(cut-off) = Vcc. The transistor appears like an open switch.

The intersection of the load line with the IB = IB(sat) curve is called the saturation point. At this point, the base current is IB(sat) and the collector current is maximum. 'At saturation, the collector diode comes out of cut-off and again the normal transistor action is lost, i.e. Ic(sat) = Vcc / RL. IB(sat) represents the minimum base current required to bring the transistor into saturation. For 0 < IB < IB(sat), the transistor operates in the active region. If the base current is greater than IB(sat), the collector current approximately equals Vcc / RL and the transistor appears like a closed switch.

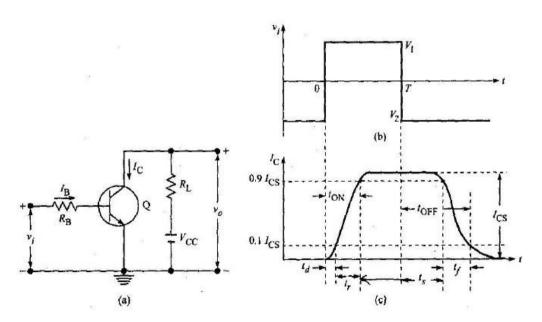

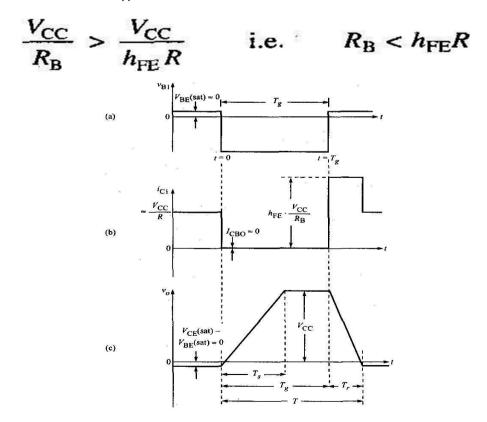

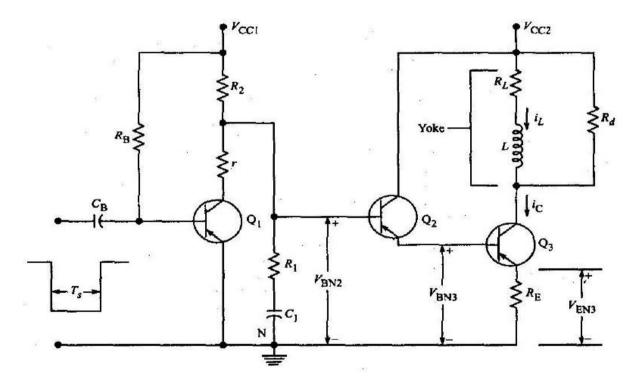

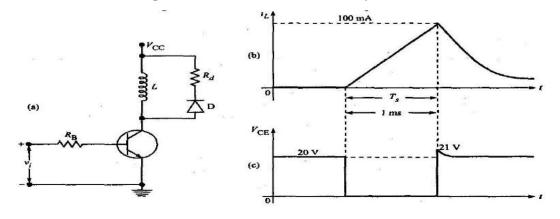

#### TRANSISTOR SWITCHING TIMES