# DIGITAL SIGNAL PROCESSORS & ARCHITECTURES (R18A0427)

Lecture Notes B. TECH (IV YEAR - II SEM) (2021-2022)

### Prepared by:

Dr. N. Subash, Associate ProfessorMr. M. Anantha Guptha, Assistant Professor

### **Department of Electronics and Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY (Autonomous Institution - UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956 (Affiliated to JNTUH, Hyderabad, Approved by AICTE-Accredited by NBA & NAAC-'A'Grade-ISO9001:2015Certified)

Maisammaguda, Dhulapally (PostVia.Kompally), Secunderabad–500100, TelanganaState, India

#### MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

IV Year B.Tech. ECE-II Sem

L T/P/D C 3 -/-/- 3

## PROFESSIONAL ELECTIVE - IV (R18A0427) DIGITAL SIGNAL PROCESSORS AND ARCHITECTURES

#### **COURSE OBJECTIVES**

- 1. To introduce architectural features of programmable DSP Processors of TI and Analog Devices.

- 2. To recall digital transform techniques.

- 3. To give practical examples of DSP Processor architectures for better understanding.

- 4. To develop the programming knowledge using Instruction set of DSP Processors.

- 5. To understand interfacing techniques to memory and I/O devices.

#### UNIT- I:

#### **Introduction to Digital Signal Processing:**

Introduction, A Digital signal-processing system, The sampling process, Discrete time sequences. Discrete Fourier Transform (DFT) and Fast Fourier Transform (FFT), Linear time- invariant systems, Digital filters, Decimation and interpolation.

### **Computational Accuracy in DSP Implementations:**

Number formats for signals and coefficients in DSP systems, Dynamic Range and Precision, Sources of error in DSP implementations, A/D Conversion errors, DSP Computational errors, D/A Conversion Errors, Compensating filter.

#### **UNIT-II:**

#### **Architectures for Programmable DSP Devices:**

Basic Architectural features, DSP Computational Building Blocks, Bus Architecture and Memory, Data Addressing Capabilities, Address Generation UNIT, Programmability and Program Execution, Speed Issues, Features for External interfacing.

#### **UNIT-III:**

#### **Programmable Digital Signal Processors:**

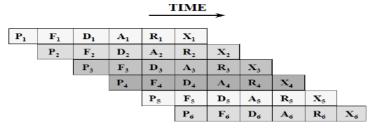

Commercial Digital signal-processing Devices, Data Addressing modes of TMS320C54XX DSPs, Data Addressing modes of TMS320C54XX Processors, Memory space of TMS320C54XX Processors, Program Control, TMS320C54XX instructions and Programming, On-Chip Peripherals, Interrupts of TMS320C54XX processors, Pipeline operation of TMS320C54XX Processors.

#### UNIT - IV:

#### **Analog Devices Family of DSP Devices:**

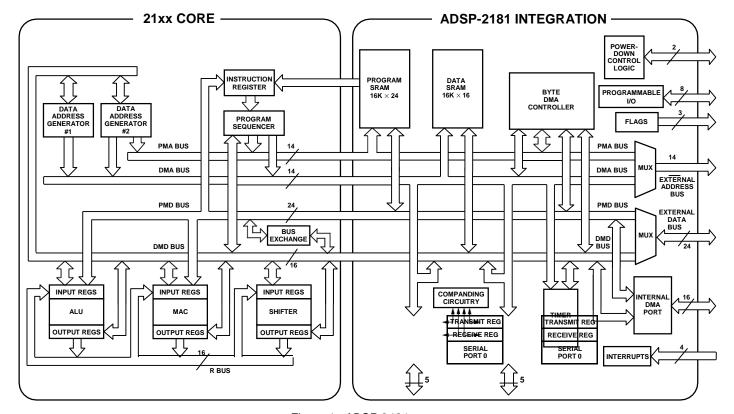

Analog Devices Family of DSP Devices – ALU and MAC block diagram, Shifter Instruction, Base Architecture of ADSP 2100, ADSP-2181 high performance Processor.

Introduction to Blackfin Processor - The Blackfin Processor, Introduction to Micro Signal Architecture, Overview of Hardware Processing Units and Register files, Address ArithmeticUnit, Control Unit,

Bus Architecture and Memory, Basic Peripherals.

#### UNIT - V:

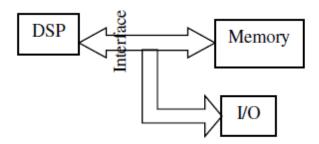

### Interfacing Memory and I/O Peripherals to Programmable DSP Devices:

Memory space organization, External bus interfacing signals, Memory interface, Parallel I/Ointerface, Programmed I/O, Interrupts and I/O, Direct memory access (DMA).

#### **TEXT BOOKS:**

- 1. Digital Signal Processing Avtar Singh and S. Srinivasan, Thomson Publications, 2004.

- 2. A Practical Approach to Digital Signal Processing K Padmanabhan, R. Vijayarajeswaran, Ananthi. S, New Age International, 2006/2009

- 3. Embedded Signal Processing with the Micro Signal Architecture Publisher: Woon-Seng Gan, Sen M. Kuo, Wiley-IEEE Press, 2007

#### **REFERENCE BOOKS:**

- 1. Digital Signal Processors, Architecture, Programming and Applications B. Venkataramani and M. Bhaskar, 2002, TMH.

- 2. Digital Signal Processing Jonatham Stein, 2005, John Wiley.

- 3. DSP Processor Fundamentals, Architectures & Features Lapsley et al. 2000, S. Chand & Co.

- 4.Digital Signal Processing Applications Using the ADSP-2100 Family by The Applications Engineering Staff of Analog Devices, DSP Division, Edited by Amy Mar, PHI

- 5.The Scientist and Engineer's Guide to Digital Signal Processing by Steven W. Smith, Ph.D., California Technical Publishing, ISBN 0-9660176-3-3, 1997 6.Embedded Media Processing by David J. Katz and Rick Gentile of Analog Devices, Newnes, ISBN 0750679123, 2005

#### **COURSE OUTCOMES:**

Upon completion of the course the student will be able to:

- 1. To distinguish between the architectural features of general purpose processors and DSPprocessors

- 2. Understand the architectures of TMS 320C54XX and ADSP2100 DSP devices

- 3. Able to write assembly language programs using instruction set of TMS320C54XX

- 4. Can interface various devices to DSP Processors

### UNIT-1

### **Introduction to Digital Signal Processing**

#### 1.1 What is DSP?

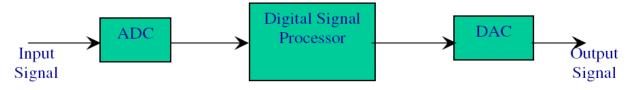

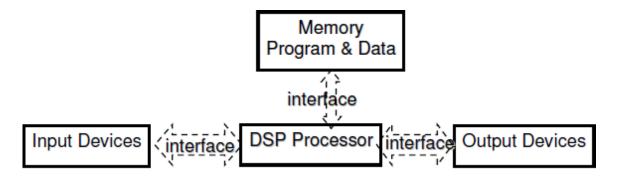

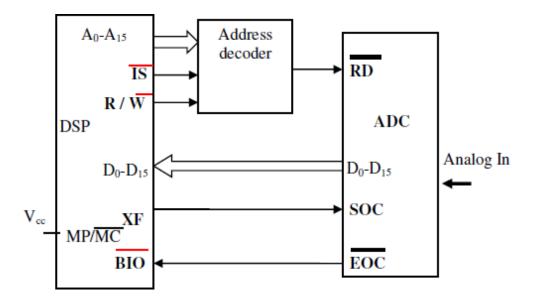

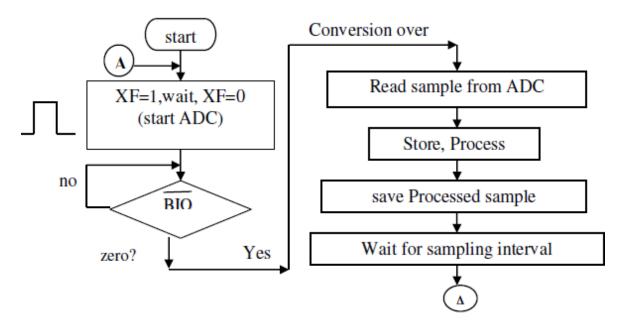

DSP is a technique of performing the mathematical operations on the signals in digital domain. As real time signals are analog in nature we need first convert the analog signal to digital, then we have to process the signal in digital domain and again converting back to analog domain. Thus ADC is required at the input side whereas a DAC is required at the output end. A typical DSP system is as shown in figure 1.1.

Fig 1.1: A Typical DSP System

#### 1.2 Need for DSP

Analog signal Processing has the following drawbacks:

- They are sensitive to environmental changes

- Aging

- Uncertain performance in production units

- Variation in performance of units

- Cost of the system will be high

- Scalability

If Digital Signal Processing would have been used we can overcome the above shortcomings of ASP.

### 1.3 A Digital Signal Processing System

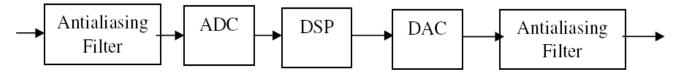

A computer or a processor is used for digital signal processing. Anti aliasing filter is a LPF which passes signal with frequency less than or equal to half the sampling frequency in order to avoid Aliasing effect. Similarly at the other end, reconstruction filter is used to reconstruct the samples from the staircase output of the DAC (Figure 1.2).

Fig 1.2 The Block Diagram of a DSP System

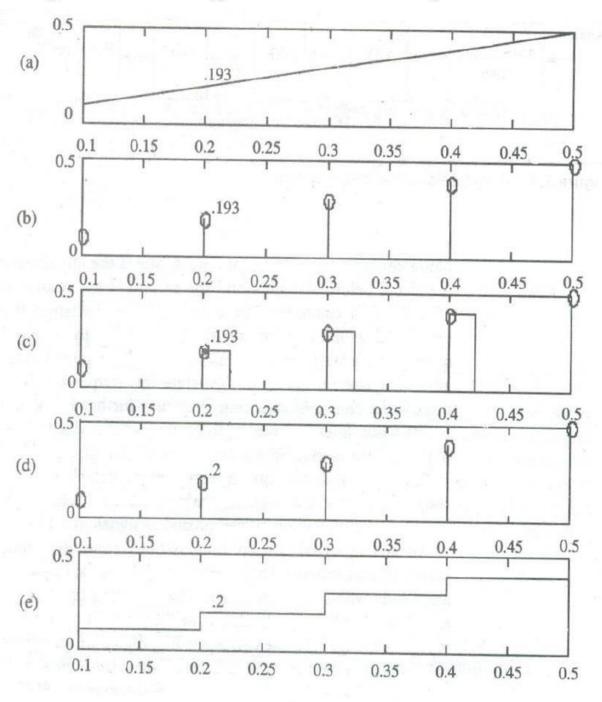

Signals that occur in a typical DSP are as shown in figure 1.3.

Fig 1.3: (a) Continuous time signal (b) Sampled Signal (c) Sampled Data Signal (d) Quantized Signal (e) DAC Output

### **1.4** The Sampling Process

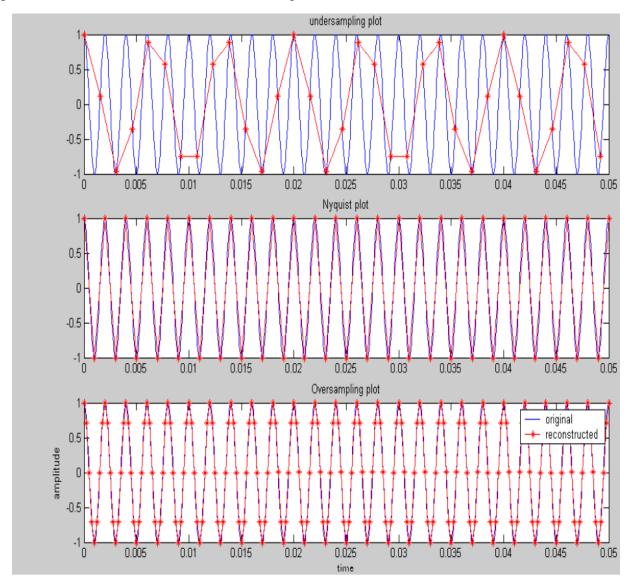

ADC process involves sampling the signal and then quantizing the same to a digital value. In order to avoid Aliasing effect, the signal has to be sampled at a rate at least equal to the Nyquist rate. The condition for Nyquist Criterion is as given below, fs=1/T  $\Box$  2 fm

Where, fs is the sampling frequency, fm is the maximum frequency component in the message signal. If the sampling of the signal is carried out with a rate less than the Nyquist rate, the higher frequency components of the signal cannot be reconstructed properly. The plots of the reconstructed outputs for various conditions are as shown in figure 1.4.

Fig 1.4 Verification of Sampling Theorem

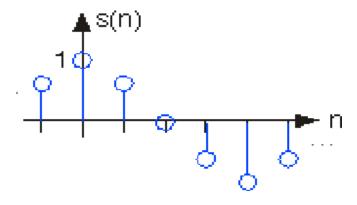

#### 1.5 Discrete Time Sequences

Consider an analog signal x(t) given by, x(t)= A cos ( $2 \Box ft$ ). If this signal is sampled at a Sampling Interval T, in the above equation replacing t by nT we get, x (nT) = A cos ( $2 \Box fnT$ )

where n = 0,1, 2,...etc

For simplicity denote x (nT) as x (n)

$\rightarrow$  x (n) = A cos (2 $\pi$ fnT) where n= 0,1, 2,..etc

We have fs=1/T also  $\theta \Box = 2\Pi fnT$

Arr  $\Box x$  (n) = A cos (2πfnT)= A cos (2πfn/fs) = A cos πnθ

The quantity  $\Box$  is called as digital frequency.

$\theta = 2\pi fT = 2\pi f/fs$  radians

Fig 1.5 A Cosine Waveform

A sequence that repeats itself after every period N is called a periodic sequence.

Consider a periodic sequence x (n) with period N x (n)=x (n+N) n=....,-1,0,1,2,.....

Frequency response gives the frequency domain equivalent of a discrete time sequence. It is denoted as  $X(e^{j\theta})=\sum x(n) e^{-jn\theta}$

Frequency response of a discrete sequence involves both magnitude response and phase response.

#### **1.6** Discrete Fourier Transform and Fast Fourier Transform

### 1.6.1 DFT Pair:

DFT is used to transform a time domain sequence x (n) to a frequency domain sequence X(K). The equations that relate the time domain sequence x (n) and the corresponding frequency domain sequence x (K) are called DFT Pair and is given by,

DFT(FFT):

$$X(k) = \sum_{n=0}^{N-1} x(n) \cdot e^{-j\left(\frac{2\pi}{N}\right)nk} (k = 0, 1, ..., N-1)$$

IDFT(IFFT):

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) \cdot e^{j\left(\frac{2\pi}{N}\right)nk} (n = 0, 1, ..., N-1)$$

### 1.6.2 The Relationship between DFT and Frequency Response:

We have,

$$X (e^{j\theta}) = \Sigma x(n) e^{-jn\theta}$$

Also

$$X(K)=\Sigma x(n) e^{-j2\pi n^{k/N}}$$

$$\therefore$$

X (K)= X (e  $j^{\theta}$ ) at  $\theta = 2\pi k/N$

From the above expression it is clear that we can use DFT to find the Frequency response of a discrete signal. Spacing between the elements of X(k) is given as  $\Box f = fs/N = 1/NT = 1/T0$ . Where T0 is the signal record length.

It is clear from the expression of  $\Box$ f that, in order to minimize the spacing between the samples N has to be a large value. Although DFT is an efficient technique of obtaining the frequency response of a sequence, it requires more number of complex operations like additions and multiplications.

Thus many improvements over DFT were proposed. One such technique is to use the periodicity property of the twiddle factor  $e^-$ . Those algorithms were called as Fast Fourier Transform Algorithms. The following table depicts the complexity involved in the computation using DFT algorithms.

Table 1.1 Complexity in DFT algorithm

| Operations              | Number of Computations |

|-------------------------|------------------------|

| Complex Multiplications | $N^2$                  |

| Complex Additions       | N (N-1)                |

| Real Multiplications    | $4N^2$                 |

| Real Additions          | 2N (2N-1)              |

| Trigonometric Functions | $2N^2$                 |

FFT algorithms are classified into two categories via

- 1. Decimation in Time FFT

- 2. Decimation in Frequency FFT

In decimation in time FFT the sequence is divided in time domain successively till we reach the sequences of length 2. Whereas in Decimation in Frequency FFT, the sequence X(K) is divided successively. The complexity of computation will get reduced considerably in case of FFT algorithms.

#### **1.7** Linear Time Invariant Systems

A system which satisfies superposition theorem is called as a linear system and a system that has same input output relation at all times is called a Time Invariant System. Systems, which satisfy both the properties, are called LTI systems.

Fig 1.6 An LTI System

LTI systems are characterized by its impulse response or unit sample response in time domain whereas it is characterized by the system function in frequency domain.

### 1.7.1 Convolution

Convolution is the operation that related the input output of an LTI system, to its unit sample response. The output of the system y(n) for the input x(n) and the impulse response of the system

being h (n) is given as y (n) =  $x(n) * h(n) = \sum \Box x(k) h(n-k)$ , x(n) is the input of the system, h(n) is the impulse response of the system, y(n) is the output of the system.

### 1.7.2 Z Transformation

Z Transformations are used to find the frequency response of the system. The Z Transform for a discrete sequence x (n) is given by,  $\mathbf{X}(\mathbf{Z}) = \sum \mathbf{x}(\mathbf{n}) \mathbf{z}^{-\mathbf{n}}$

### 1.7.3 The System Function

An LTI system is characterized by its System function or the transfer function. The system function of a system is the ratio of the Z transformation of its output to that of its input. It is denoted as H(Z) and is given by H(Z) = Y(Z)/X(Z).

The magnitude and phase of the transfer function H (Z) gives the frequency response of the system. From the transfer function we can also get the poles and zeros of the system by solving its numerator and denominator respectively.

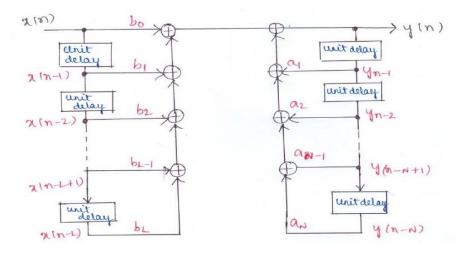

#### **1.8** Digital Filters

Filters are used to remove the unwanted components in the sequence. They are characterized by the impulse response h (n). The general difference equation for an Nth order filter is given by

$$y(n) = \square \sum a_k y(n-k) + \sum \square b_k x(n-k)$$

A typical digital filter structure is as shown in figure 1.7.

Fig 1.7 Structure of a Digital Filter

Values of the filter coefficients vary with respect to the type of the filter. Design of a digital filter involves determining the filter coefficients. Based on the length of the impulse response, digital filters are classified into two categories via Finite Impulse Response (FIR) Filters and Infinite Impulse Response (IIR) Filters.

### 1.8.1 FIR Filters

FIR filters have impulse responses of finite lengths. In FIR filters the present output depends only on the past and present values of the input sequence but not on the previous output sequences. Thus they are non recursive hence they are inherently stable.FIR filters possess linear phase response. Hence they are very much applicable for the applications requiring linear phase response.

The difference equation of an FIR filter is represented as

$$y(n) = \sum b_k x(n-k)$$

The frequency response of an FIR filter is given as

H (e

$$j^{\theta}$$

)= $\sum b_k e^{-jk\theta}$

$$H(Z)=\Sigma b_k Z^{-k}$$

The major drawback of FIR filters is, they require more number of filter coefficients to realize a desired response as compared to IIR filters. Thus the computational time required will also be more.

### 1.8.2 IIR Filters

Unlike FIR filters, IIR filters have infinite number of impulse response samples. They are recursive filters as the output depends not only on the past and present inputs but also on the past outputs. They generally do not have linear phase characteristics. Typical system function of suchfilters is given by,

$$H(Z) = (b_0 + b_1 z^{-1} + b_2 z^{-2} + \dots b_L z^{-L}) / (1 - a_1 z^{-1} - a_2 z^{-2} - \dots a_N z^{-N})$$

Stability of IIR filters depends on the number and the values of the filter coefficients. The major advantage of IIR filters over FIR is that, they require lesser coefficients compared to FIR filters for the same desired response, thus requiring less computation time.

### 1.8.3 FIR Filter Design

Frequency response of an FIR filter is given by the following expression,

$$H(e j^{\theta}) = \Sigma b_k e^{-jk\theta}$$

Design procedure of an FIR filter involves the determination of the filter coefficients bk.

$$b_k = (1/2\pi) \int H(e^{j\theta}) e^{-jk\theta} d\theta$$

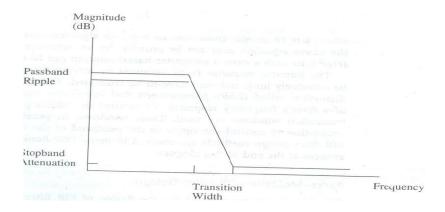

### 1.8.4 IIR Filter Design

IIR filters can be designed using two methods viz using windows and direct method. In this approach, a digital filter can be designed based on its equivalent analog filter. An analog filter is designed first for the equivalent analog specifications for the given digital specifications. Then using appropriate

frequency transformations, a digital filter can be obtained. The filter specifications consist of passband and stopband ripples in dB and Passband and Stopband frequencies in rad/sec.

Fig 1.11 Lowpass Filter Specifications

Direct IIR filter design methods are based on least squares fit to a desired frequency response. These methods allow arbitrary frequency response specifications.

### 1.9 Decimation and Interpolation

Decimation and Interpolation are two techniques used to alter the sampling rate of a sequence. Decimation involves decreasing the sampling rate without violating the sampling theorem whereas interpolation increases the sampling rate of a sequence appropriately by considering its neighboring samples.

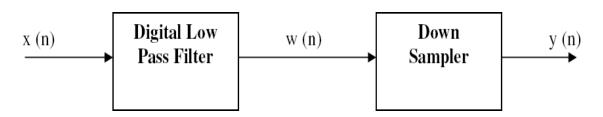

#### 1.9.1 Decimation

Decimation is a process of dropping the samples without violating sampling theorem. The factor by which the signal is decimated is called as decimation factor and it is denoted by M. It is given by,  $y(m)=w(mM)=\sum b_k x(mM-k)$  where  $w(n)=\sum b_k x(n-k)$

Fig 1.12 Decimation Process

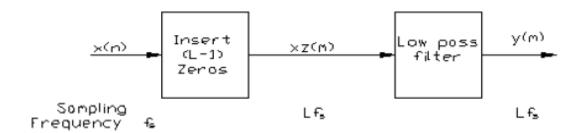

### 1.9.2 Interpolation

Interpolation is a process of increasing the sampling rate by inserting new samples in between. The input output relation for the interpolation, where the sampling rate is increased by a factor L, is given as,

$$y(m) = \sum b_k w(m-k)$$

where

$$w(n)=x(m/L)$$

,  $m=0,\pm L, \pm 2L...$

0 Otherwise

Fig 1.13 Interpolation Process

#### **Problems:**

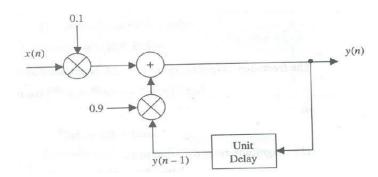

1. Obtain the transfer function of the IIR filter whose difference equation is given by y (n)=0.9y (n-1)+0.1x (n)

y(n) = 0.9y(n-1) + 0.1x(n)

Taking Z transformation both sides

Y(Z) = 0.9 Z-1 Y(Z) + 0.1 X(Z)

Y(Z)[1-0.9 Z-1] = 0.1 X(Z)

The transfer function of the system is given by the expression,

H(Z)=Y(Z)/X(Z)

$= 0.1/[1-0.9 Z^{-1}]$

Realization of the IIR filter with the above difference equation is as shown in figure.

### UNIT-2

# <u>Architectures for Programmable Digital Signal Processing</u> <u>Devices</u>

#### **2.1** Basic Architectural Features

A programmable DSP device should provide instructions similar to a conventional microprocessor. The instruction set of a typical DSP device should include the following,

- a. Arithmetic operations such as ADD, SUBTRACT, MULTIPLY etc.

- b. Logical operations such as AND, OR, NOT, XOR etc

- c. Multiply and Accumulate (MAC) operation

- d. Signal scaling operation

In addition to the above provisions, the architecture should also include,

- a. On chip registers to store immediate results

- b. On chip memories to store signal samples (RAM)

- c. On chip memories to store filter coefficients (ROM)

#### 2.2 DSP Computational Building Blocks

Each computational block of the DSP should be optimized for functionality and speed and in the meanwhile the design should be sufficiently general so that it can be easily integrated with other blocks to implement overall DSP systems.

### 2.2.1 Multipliers

The advent of single chip multipliers paved the way for implementing DSP functions on a VLSI chip. Parallel multipliers replaced the traditional shift and add multipliers now days. Parallel multipliers take a single processor cycle to fetch and execute the instruction and to store the result. They are also called as Array multipliers. The key features to be considered for a multiplier are:

- a. Accuracy

- b. Dynamic range

- c. Speed

The number of bits used to represent the operands decides the accuracy and the dynamic range of the multiplier. Whereas speed is decided by the architecture employed. If the multipliers are implemented using hardware, the speed of execution will be very high but the circuit complexity will also increases considerably. Thus there should be a tradeoff between the speed of execution and the circuit complexity. Hence the choice of the architecture normally depends on the application.

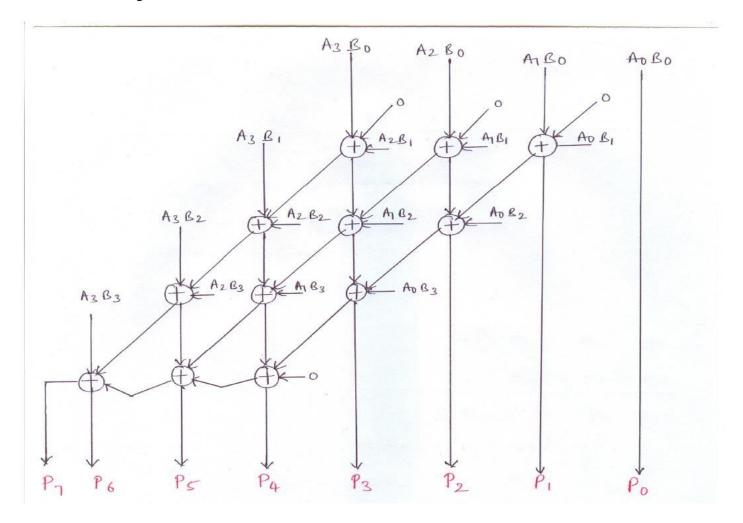

### 2.2.2 Parallel Multipliers

Consider the multiplication of two unsigned numbers A and B. Let A be represented using m bits as (Am-1 Am-2 ....... A1 A0) and B be represented using n bits as (Bn-1 Bn-2 ....... B1 B0). Then the product of these two numbers is given by,

|            |            |            |          |          | $\mathbf{B}_3$ | $B_2$ $B_1$ | $\mathbf{B_0}$ |

|------------|------------|------------|----------|----------|----------------|-------------|----------------|

|            |            |            |          | $A_3B_0$ | $A_2B_0$       | $A_1B_0$    | $A_0B_0$       |

|            |            |            | $A_3B_1$ | $A_2B_1$ | $A_1B_1$       | $A_0B_1$    |                |

|            |            | $A_3B_2$   | $A_2B_2$ | $A_1B_2$ | $A_0B_2$       |             |                |

| 7          | $A_3B_3$   | $A_2B_3$   | $A_1B_3$ | $A_0B_3$ |                |             |                |

| <b>P</b> 7 | <b>P</b> 6 | <b>P</b> 5 | P4       | Р3       | P2             | P1          | Ρ0             |

This operation can be implemented paralleling using Braun multiplier whose hardware structure is as shown in the figure 2.1.

Fig 2.1 Braun Multiplier for a 4X4 Multiplication

### 2.2.3 Multipliers for Signed Numbers

In the Braun multiplier the sign of the numbers are not considered into account. In order to implement a multiplier for signed numbers, additional hardware is required to modify the Braun multiplier. The modified multiplier is called as Baugh-Wooley multiplier.

Consider two signed numbers A and B,

$$\begin{split} \mathbf{A} &= -\mathbf{A}_{m-1} 2^{m-1} + \sum_{i=0}^{m-2} \mathbf{A}_{i} 2^{i} \\ \mathbf{B} &= -\mathbf{B}_{n-1} 2^{n-1} + \sum_{j=0}^{n-2} \mathbf{B}_{j} 2^{j} \\ \mathbf{P} &= \mathbf{P}_{m+n-1} \dots \mathbf{P}_{1} \mathbf{P}_{0} \\ \mathbf{P} &= \mathbf{A}_{m-1} \mathbf{B}_{n-1} 2^{m+n-2} + \sum_{i=0}^{m-2} \sum_{j=0}^{n-2} \mathbf{A}_{i} \mathbf{B}_{j} 2^{i+j} - \sum_{i=0}^{m-2} \mathbf{A}_{i} \mathbf{B}_{n-1} 2^{n-1+1} - \sum_{j=0}^{m-2} \mathbf{A}_{m-1} \mathbf{B}_{j} 2^{m-1+j} \end{split}$$

### 2.2.4 **Speed**

Conventional Shift and Add technique of multiplication requires n cycles to perform the multiplication of two n bit numbers. Whereas in parallel multipliers the time required will be the longest path delay in the combinational circuit used. As DSP applications generally require very high speed, it is desirable to have multipliers operating at the highest possible speed by having parallel implementation.

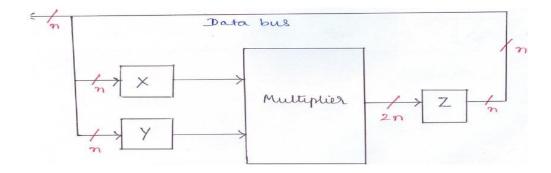

### 2.2.5 Bus Widths

Consider the multiplication of two n bit numbers X and Y. The product Z can be at most 2n bits long. In order to perform the whole operation in a single execution cycle, we require two buses of width n bits each to fetch the operands X and Y and a bus of width 2n bits to store the result Z to the memory. Although this performs the operation faster, it is not an efficient way of implementation as it is expensive. Many alternatives for the above method have been proposed. One such method is to use the program bus itself to fetch one of the operands after fetching the instruction, thus requiring only one bus to fetch the operands. And the result Z can be stored back to the memory using the same operand bus. But the problem with this is the result Z is 2n bits long whereas the operand bus is just n bits long. We have two alternatives to solve this problem, a. Use the n bits operand bus and save Z at two successive memory locations. Although it stores the exact value of Z in the memory, it takes two cycles to store the result.

b. Discard the lower n bits of the result Z and store only the higher order n bits into the memory. It is not applicable for the applications where accurate result is required. Another alternative can be used for the applications where speed is not a major concern. In which latches are used for inputs and outputs thus requiring a single bus to fetch the operands and to store the result (Fig 2.2).

Fig 2.2: A Multiplier with Input and Output Latches

### 2.2.6 Shifters

Shifters are used to either scale down or scale up operands or the results. The following scenarios give the necessity of a shifter

- a. While performing the addition of N numbers each of n bits long, the sum can grow up to n+log2 N bits long. If the accumulator is of n bits long, then an overflow error will occur. This can be overcome by using a shifter to scale down the operand by an amount of log2N.

- b. Similarly while calculating the product of two n bit numbers, the product can grow up to 2n bits long. Generally the lower n bits get neglected and the sign bit is shifted to save the sign of the product.

- c. Finally in case of addition of two floating-point numbers, one of the operands has to be shifted appropriately to make the exponents of two numbers equal.

From the above cases it is clear that, a shifter is required in the architecture of a DSP.

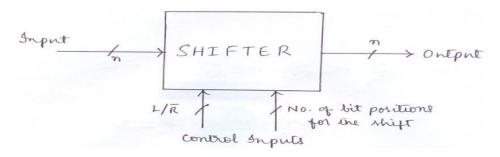

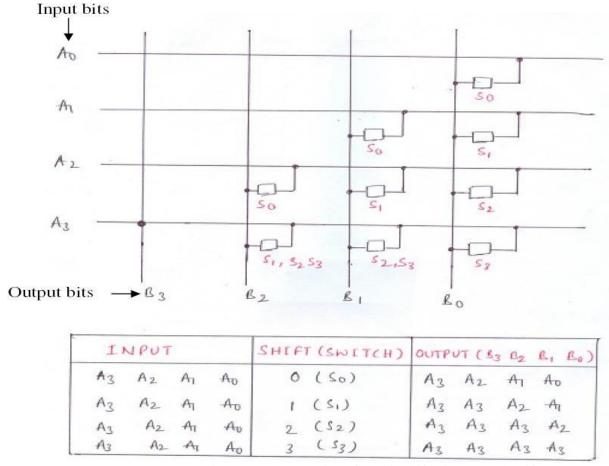

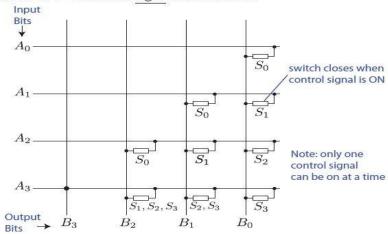

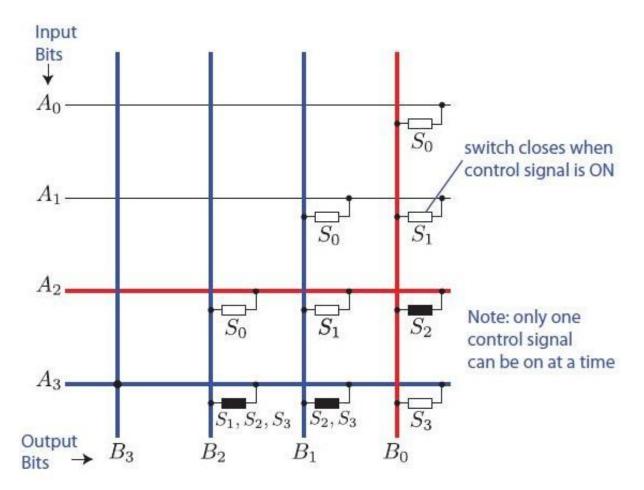

### 2.2.7 Barrel Shifters

In conventional microprocessors, normal shift registers are used for shift operation. As it requires one clock cycle for each shift, it is not desirable for DSP applications, which generally involves more shifts. In other words, for DSP applications as speed is the crucial issue, several shifts are to be accomplished in a single execution cycle. This can be accomplished using a barrel shifter, which connects the input lines representing a word to a group of output lines with the required shifts determined by its control inputs. For an input of length n, log2 n control lines are required. And an additional control line is required to indicate the direction of the shift.

The block diagram of a typical barrel shifter is as shown in figure 2.3.

Fig 2.3 A Barrel Shifter

Fig 2.4 Implementation of a 4 bit Shift Right Barrel Shifter

Figure 2.4 depicts the implementation of a 4 bit shift right barrel shifter. Shift to right by 0, 1, 2 or 3 bit positions can be controlled by setting the control inputs appropriately.

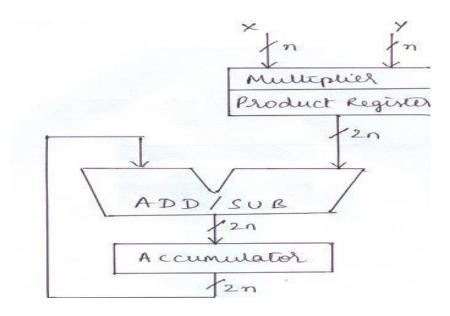

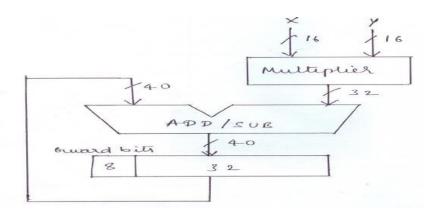

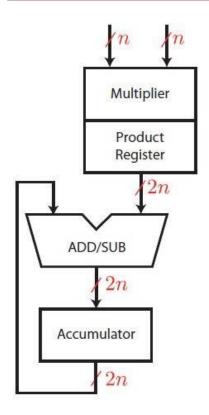

### 2.3 Multiply and Accumulate Unit

Most of the DSP applications require the computation of the sum of the products of a series of successive multiplications. In order to implement such functions a special unit called a multiply and Accumulate (MAC) unit is required. A MAC consists of a multiplier and a special register called Accumulator. MACs are used to implement the functions of the type A+BC. A typical MAC unit is as shown in the figure 2.5.

Fig 2.5 A MAC Unit

Although addition and multiplication are two different operations, they can be performed in parallel. By the time the multiplier is computing the product, accumulator can accumulate the product of the previous multiplications. Thus if N products are to be accumulated, N-1 multiplications can overlap with N-1 additions. During the very first multiplication, accumulator will be idle and during the last accumulation, multiplier will be idle. Thus N+1 clock cycles are required to compute the sum of N products.

### 2.3.1 Overflow and Underflow

While designing a MAC unit, attention has to be paid to the word sizes encountered at the input of the multiplier and the sizes of the add/subtract unit and the accumulator, as there is a possibility of overflow and underflows. Overflow/underflow can be avoided by using any of the following methods viz

- a. Using shifters at the input and the output of the MAC

- b. Providing guard bits in the accumulator

- c. Using saturation logic

### **Shifters**

Shifters can be provided at the input of the MAC to normalize the data and at the output to de normalize the same.

#### Guard bits

As the normalization process does not yield accurate result, it is not desirable for some applications. In such cases we have another alternative by providing additional bits called guard bits in the accumulator so that there will not be any overflow error. Here the add/subtract unit also has to be

modified appropriately to manage the additional bits of the accumulator.

#### Saturation Logic

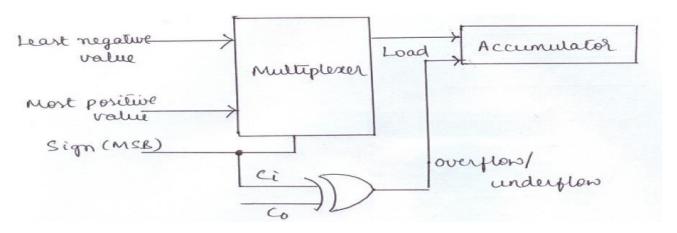

Overflow/ underflow will occur if the result goes beyond the most positive number or below the least negative number the accumulator can handle. Thus the overflow/underflow error can be resolved by loading the accumulator with the most positive number which it can handle at the time of overflow and the least negative number that it can handle at the time of underflow. This method is called as saturation logic. A schematic diagram of saturation logic is as shown in figure 2.7. In saturation logic, as soon as an overflow or underflow condition is satisfied the accumulator will be loaded with the most positive or least negative number overriding the result computed by the MAC unit.

Fig 2.7: Schematic Diagram of the Saturation Logic

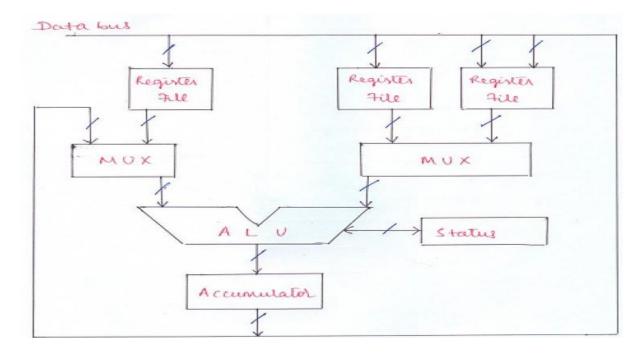

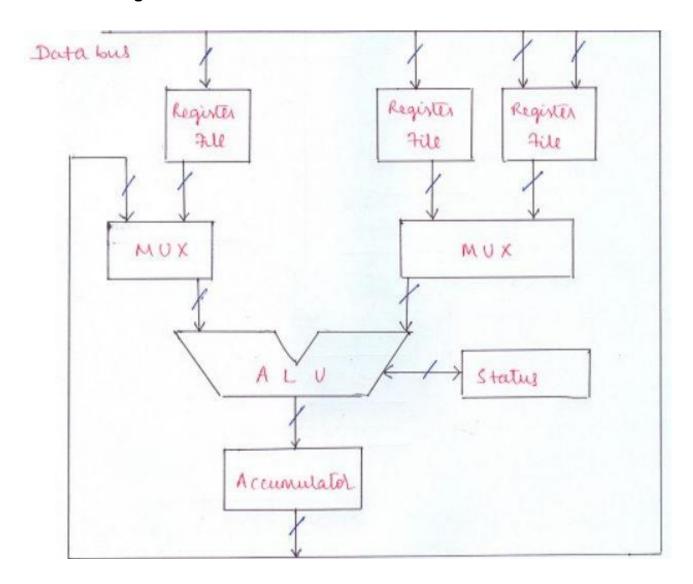

### 2.4 Arithmetic and Logic Unit

A typical DSP device should be capable of handling arithmetic instructions like ADD, SUB, INC, DEC etc and logical operations like AND, OR, NOT, XOR etc. The block diagram of a typical ALU for a DSP is as shown in the figure 2.8.

It consists of status flag register, register file and multiplexers.

Fig 2.8 Arithmetic Logic Unit of a DSP

### Status Flags

ALU includes circuitry to generate status flags after arithmetic and logic operations. These flags include sign, zero, carry and overflow.

### Overflow Management

Depending on the status of overflow and sign flags, the saturation logic can be used to limit the accumulator content.

### Register File

Instead of moving data in and out of the memory during the operation, for better speed, a large set of general purpose registers are provided to store the intermediate results.

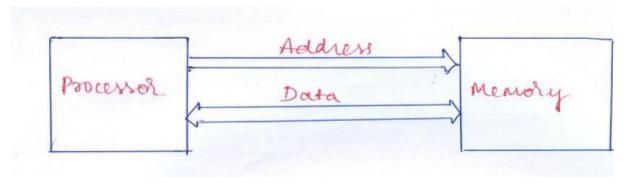

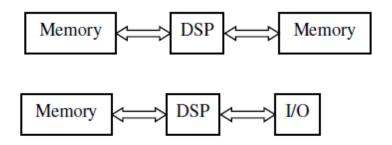

### **2.5** Bus Architecture and Memory

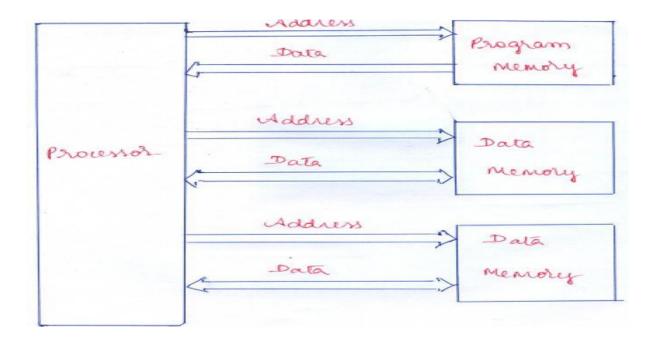

Conventional microprocessors use Von Neumann architecture for memory management wherein the same memory is used to store both the program and data (Fig 2.9). Although this architecture is simple, it takes more number of processor cycles for the execution of a single instruction as the same bus is used for both data and program.

Fig 2.9 Von Neumann Architecture

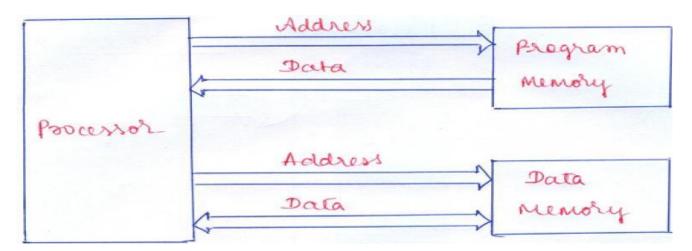

In order to increase the speed of operation, separate memories were used to store program and data and a separate set of data and address buses have been given to both memories, the architecture called as Harvard Architecture. It is as shown in figure 2.10.

Fig 2.10 Harvard Architecture

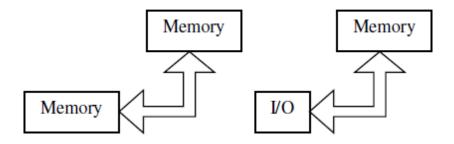

Although the usage of separate memories for data and the instruction speeds up the processing, it will not completely solve the problem. As many of the DSP instructions require more than one operand, use of a single data memory leads to the fetch the operands one after the other, thusincreasing the delay of processing. This problem can be overcome by using two separate data memories for storing operands separately, thus in a single clock cycle both the operands can be fetchedtogether (Figure 2.11).

Fig 2.11 Harvard Architecture with Dual Data Memory

Although the above architecture improves the speed of operation, it requires more hardware and interconnections, thus increasing the cost and complexity of the system. Therefore there should be a trade off between the cost and speed while selecting memory architecture for a DSP.

### 2.5.1 On-chip Memories

In order to have a faster execution of the DSP functions, it is desirable to have some memory located on chip. As dedicated buses are used to access the memory, on chip memories are faster. Speed and size are the two key parameters to be considered with respect to the on-chip memories.

#### Speed

On-chip memories should match the speeds of the ALU operations in order to maintain the single cycle instruction execution of the DSP.

#### Size

In a given area of the DSP chip, it is desirable to implement as many DSP functions as possible. Thus the area occupied by the on-chip memory should be minimum so that there will be a scope for implementing more number of DSP functions on- chip.

### 2.5.2 Organization of On-chip Memories

Ideally whole memory required for the implementation of any DSP algorithm has to reside onchip so that the whole processing can be completed in a single execution cycle. Although it looks as a better solution, it consumes more space on chip, reducing the scope for implementing any functional block on-chip, which in turn reduces the speed of execution. Hence some other alternatives have to be thought of. The following are some other ways in which the on-chip memory can be organized.

a. As many DSP algorithms require instructions to be executed repeatedly, the instruction can bestored in the external memory, once it is fetched can reside in the instruction cache.

- b. The access times for memories on-chip should be sufficiently small so that it can be accessed morethan once in every execution cycle.

- c. On-chip memories can be configured dynamically so that they can serve different purpose atdifferent times.

### 2.6 Data Addressing Capabilities

Data accessing capability of a programmable DSP device is configured by means of its addressing modes. The summary of the addressing modes used in DSP is as shown in the table below.

| Addressing<br>Mode | Operand                                      | Sample Format | Operation      |

|--------------------|----------------------------------------------|---------------|----------------|

| Immediate          | Immediate Value                              | ADD #imm      | #imm +A →A     |

| Register           | Register Contents                            | ADD reg       | reg +A → A     |

| Direct             | Memory Address Register                      | ADD mem       | mem+A → A      |

| Indirect           | Memory contents with address in the register | ADD *addreg   | *addreg +A → A |

Table 2.1 DSP Addressing Modes

### 2.6.1 Immediate Addressing Mode

In this addressing mode, data is included in the instruction itself.

### 2.6.2 Register Addressing Mode

In this mode, one of the registers will be holding the data and the register has to be specified in the instruction.

### 2.6.3 Direct Addressing Mode

In this addressing mode, instruction holds the memory location of the operand.

### 2.6.4 Indirect Addressing Mode

In this addressing mode, the operand is accessed using a pointer. A pointer is generally a register, which holds the address of the location where the operands resides. Indirect addressing mode can be extended to inculcate automatic increment or decrement capabilities, which has lead to the following addressing modes.

Table 2.2 Indirect Addressing Modes

| Addressing Mode | Sample Format           | Operation                       |

|-----------------|-------------------------|---------------------------------|

| D I             | ADD * 11                | A > A . ¥ 11                    |

| Post Increment  | ADD *addreg+            | A → A + *addreg                 |

|                 | 155 / 11                | addreg — addreg+1               |

| Post Decrement  | ADD *addreg-            | $A \longrightarrow A + *addreg$ |

|                 |                         | addreg → addreg-1               |

| Pre Increment   | ADD +*addreg            | addreg → addreg+1               |

|                 |                         | A → A + *addreg                 |

| Pre Decrement   | ADD -*addreg            | addreg → addreg-1               |

|                 |                         | A → A + *addreg                 |

| Post_Add_Offset | ADD *addreg, offsetreg+ | $A \longrightarrow A + *addreg$ |

|                 |                         | addreg → addreg+offsetreg       |

| Post_Sub_Offset | ADD *addreg, offsetreg- | A → A + *addreg                 |

|                 |                         | addreg → addreg-offsetreg       |

| Pre_Add_Offset  | ADD offsetreg+,*addreg  | addreg → addreg+offsetreg       |

|                 |                         | A → A + *addreg                 |

| Pre_Sub_Offset  | ADD offsetreg-,*addreg  | addreg → addreg-offsetreg       |

|                 |                         | A → A + *addreg                 |

### 2.7 Special Addressing Modes

For the implementation of some real time applications in DSP, normal addressing modes will not completely serve the purpose. Thus some special addressing modes are required for such applications.

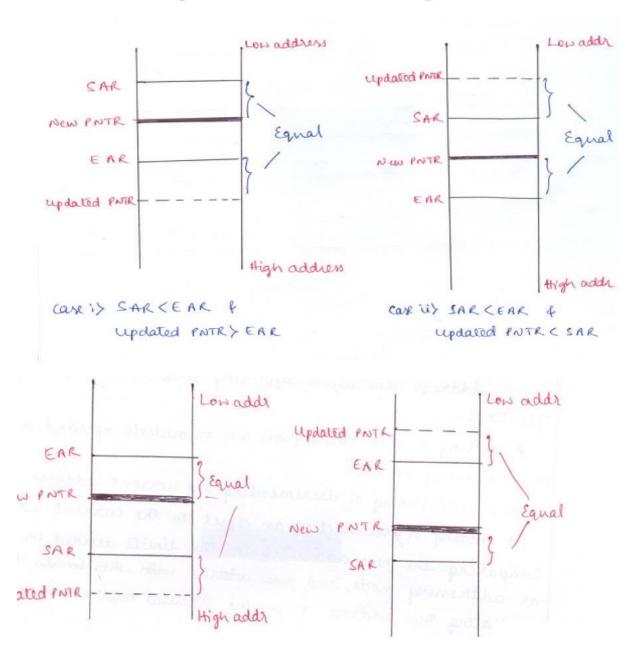

### 2.7.1 Circular Addressing Mode

While processing the data samples coming continuously in a sequential manner, circularbuffers are used. In a circular buffer the data samples are stored sequentially from the initial location till the buffer gets filled up. Once the buffer gets filled up, the next data samples will get stored once again from the initial location. This process can go forever as long as the data samples are processed in a rate faster than the incoming data rate.

Circular Addressing mode requires three registers viz

- a. Pointer register to hold the current location (PNTR)

- b. Start Address Register to hold the starting address of the buffer (SAR)

- c. End Address Register to hold the ending address of the buffer (EAR)

There are four special cases in this addressing mode. They are

- a. SAR < EAR & updated PNTR > EAR

- b. SAR < EAR & updated PNTR < SAR

- c. SAR >EAR & updated PNTR > SAR

- d. SAR > EAR & updated PNTR < EAR

The buffer length in the first two case will be (EAR-SAR+1) whereas for the next tow cases (SAR-EAR+1)

The pointer updating algorithm

; Pointer Updating Algorithm

Updated PNTR ← PNTR ± increment

If SAR < EAR

And if Updated PNTR > EAR, then

And if Updated PNTR < SAR then

New PNTR Updated PNTR + Buffer size

If SAR > EAR

And if Updated PNTR > SAR then

And if Updated PNTR < EAR, then

New PNTR ◀ Updated PNTR + Buffer size

Else

Four cases explained earlier are as shown in the figure 2.12.

Fig 2.12 Special Cases in Circular Addressing Mode

### 2.7.2 Bit Reversed Addressing Mode

To implement FFT algorithms we need to access the data in a bit reversed manner. Hence a special addressing mode called bit reversed addressing mode is used to calculate the index of the next data to be fetched. It works as follows. Start with index 0. The present index can be calculated by adding half the FFT length to the previous index in a bit reversed manner, carry being propagated from MSB to LSB.

### Current index= Previous index+ B (1/2(FFT Size))

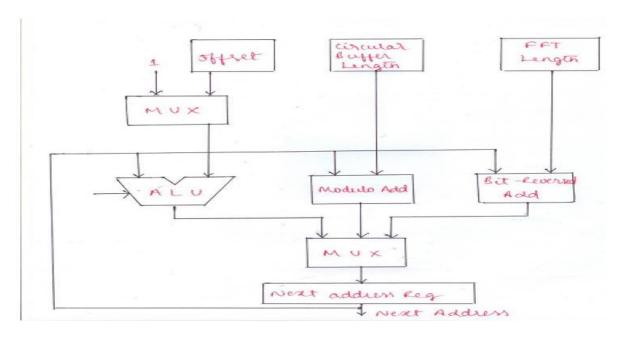

#### 2.8 Address Generation Unit

The main job of the Address Generation Unit is to generate the address of the operands required to carry out the operation. They have to work fast in order to satisfy the timing constraints. As the address generation unit has to perform some mathematical operations in order to calculate the operand address, it is provided with a separate ALU.

Address generation typically involves one of the following operations.

- a. Getting value from immediate operand, register or a memory location

- b. Incrementing/ decrementing the current address

- c. Adding/subtracting the offset from the current address

- d. Adding/subtracting the offset from the current address and generating new address according tocircular addressing mode

- e. Generating new address using bit reversed addressing mode

The block diagram of a typical address generation unit is as shown in figure 2.13.

Fig 2.13 Address generation unit

### 2.9 Programmability and program Execution

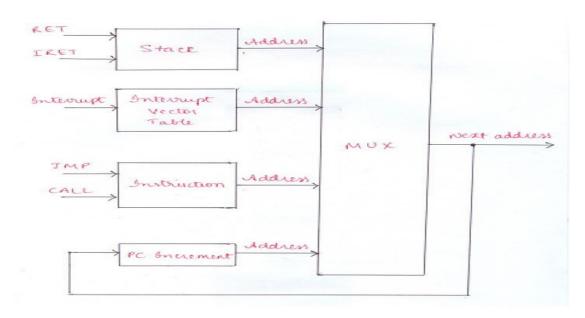

A programmable DSP device should provide the programming capability involving branching, looping and subroutines. The implementation of repeat capability should be hardware based so that it can be programmed with minimal or zero overhead. A dedicated register can be used as a counter. In a normal subroutine call, return address has to be stored in a stack thus requiring memory access for storing and retrieving the return address, which in turn reduces the speed of operation. Hence a LIFO memory can be directly interfaced with the program counter.

### 2.9.1 Program Control

Like microprocessors, DSP also requires a control unit to provide necessary control and timing signals for the proper execution of the instructions. In microprocessors, the controlling is micro coded based where each instruction is divided into microinstructions stored in micro memory. As this mechanism is slower, it is not applicable for DSP applications. Hence in DSP the controlling is hardwired base where the Control unit is designed as a single, comprehensive, hardware unit. Although it is more complex it is faster.

### 2.9.2 Program Sequencer

It is a part of the control unit used to generate instruction addresses in sequence needed to access instructions. It calculates the address of the next instruction to be fetched. The next address can be from one of the following sources.

- a. Program Counter

- b. Instruction register in case of branching, looping and subroutine calls

- c. Interrupt Vector table

- d. Stack which holds the return address

The block diagram of a program sequencer is as shown in figure 2.14.

Fig 2.14 Program Sequencer

Program sequencer should have the following circuitry:

- a. PC has to be updated after every fetch

- b. Counter to hold count in case of looping

- c. A logic block to check conditions for conditional jump instructions

- d. Condition logic-status flag

#### **Problems:**

1). Investigate the basic features that should be provided in the DSP architecture to be used toimplement the following N<sup>th</sup> order FIR filter.

#### Solution:-

### $y(n) = \sum h(i) x(n-i) n = 0,1,2...$

In order to implement the above operation in a DSP, the architecture requires the following features

- i. A RAM to store the signal samples x (n)

- ii. A ROM to store the filter coefficients h (n)

- iii. An MAC unit to perform Multiply and Accumulate operation

- iv. An accumulator to store the result immediately

- v. A signal pointer to point the signal sample in the memory

- vi. A coefficient pointer to point the filter coefficient in the memory

- vii. A counter to keep track of the count

- viii. A shifter to shift the input samples appropriately

- 2). It is required to find the sum of 64, 16 bit numbers. How many bits should theaccumulator have so that the sum can be computed without the occurrence of overflow error or loss of accuracy?

The sum of 64, 16 bit numbers can grow up to  $(16 + \log 2 64) = 22$  bits long. Hence the accumulator should be 22 bits long in order to avoid overflow error from occurring.

1. In the previous problem, it is decided to have an accumulator with only 16 bitsbut shift the numbers before the addition to prevent overflow, by how many bits should each number be shifted?

As the length of the accumulator is fixed, the operands have to be shifted by an amount of  $\log 2.64 = 6$  bits prior to addition operation, in order to avoid the condition of overflow.

2. If all the numbers in the previous problem are fixed point integers, what is theactual sum of the numbers?

The actual sum can be obtained by shifting the result by 6 bits towards left side after the sum being computed. Therefore

Actual Sum= Accumulator content X 2 6

3. If a sum of 256 products is to be computed using a pipelined MAC unit, and if the MAC execution time of the unit is 100nsec, what will be the total time required to complete theoperation?

As N=256 in this case, MAC unit requires N+1=257execution cycles. As the single MAC execution time is 100nsec, the total time required will be, (257\*100nsec)=25.7usec

4. Consider a MAC unit whose inputs are 16 bit numbers. If 256 products are to be summed up in this MAC, how many guard bits should be provided for the

accumulator to prevent overflow condition from occurring?

As it is required to calculate the sum of 256, 16 bit numbers, the sum can be as long as  $(16 + \log 2\ 256) = 24$  bits. Hence the accumulator should be capable of handling these 22 bits. Thus the guard bits required will be (24-16) = 8 bits.

The block diagram of the modified MAC after considering the guard or extention bits is as shown in the figure

- 5. What are the memory addresses of the operands in each of the following cases of indirect addressing modes? In each case, what will be the content of the *addreg* after the memory access? Assume that the initial contents of the *addreg* and the *offsetreg* are 0200h and 0010h,respectively.

- a. ADD \*addreg

- b. ADD +\*addreg

- c. ADD offsetreg+,\*addreg

- d. ADD \*addreg,offsetreg-

| Instruction            | Addressing<br>Mode | Operand Address | addreg Content<br>after Access |

|------------------------|--------------------|-----------------|--------------------------------|

| ADD *addreg-           | Post Decrement     | 0200h           | 0200-01=01FFh                  |

| ADD +*addreg           | Pre Increment      | 0200+01=0201h   | 0201h                          |

| ADD offsetreg+,*addreg | Pre_Add_Offset     | 0200+0010=0210h | 0210h                          |

| ADD *addreg,offsetreg- | Post_Sub_Offset    | 0200h           | 0200-0010=01F0h                |

6. A DSP has a circular buffer with the start and the end addresses as 0200h and 020Fh respectively. What would be the new values of the address pointer of the buffer if, in the courseof address computation, it gets updated to

0212h

b. 01FCh

Buffer Length= (EAR-SAR+1) = 020F-0200+1=10h

- a. New Address Pointer= Updated Pointer-buffer length = 0212-10=0202h

- b. New Address Pointer= Updated Pointer+ buffer length = 01FC+10=020Ch

- 7. Repeat the previous problem for SAR= 0210h and EAR=0201h Buffer Length= (SAR-EAR+1)=0210-0201+1=10h

- c. New Address Pointer= Updated Pointer- buffer length = 0212-10=0202h

- d. New Address Pointer= Updated Pointer+ buffer length = 01FC+10=020Ch

- **9.** Compute the indices for an 8-point FFT using Bit reversed Addressing Mode Start with index 0. Therefore the first index would be (000)

Next index can be calculated by adding half the FFT length, in this case it is (100)

to the previous index. i.e. Present Index= (000)+B(100)=(100)

Similarly the next index can be calculated as

Present Index= (100)+B(100)=(010)

The process continues till all the indices are calculated. The following table summarizes the calculation.

| BCD value | Bit reversed index         | BCD value                                                                                                 |

|-----------|----------------------------|-----------------------------------------------------------------------------------------------------------|

| 0         | 000                        | 0                                                                                                         |

| 1         | 100                        | 4                                                                                                         |

| 2         | 010                        | 2                                                                                                         |

| 3         | 110                        | 6                                                                                                         |

| 4         | 001                        | 1                                                                                                         |

| 5         | 101                        | 5                                                                                                         |

| 6         | 011                        | 3                                                                                                         |

| 7         | 111                        | 7                                                                                                         |

|           | 0<br>1<br>2<br>3<br>4<br>5 | 0     000       1     100       2     010       3     110       4     001       5     101       6     011 |

### **UNIT-3**

### **Programmable Digital Signal Processors**

#### **3.1** Introduction:

Leading manufacturers of integrated circuits such as Texas Instruments (TI), Analog devices & Motorola manufacture the digital signal processor (DSP) chips. These manufacturers have developed a range of DSP chips with varied complexity.

The TMS320 family consists of two types of single chips DSPs: 16-bit fixed point &32-bit floating-point. These DSPs possess the operational flexibility of high-speed controllers and the numerical capability of array processors

### 3.2 Commercial Digital Signal-Processing Devices:

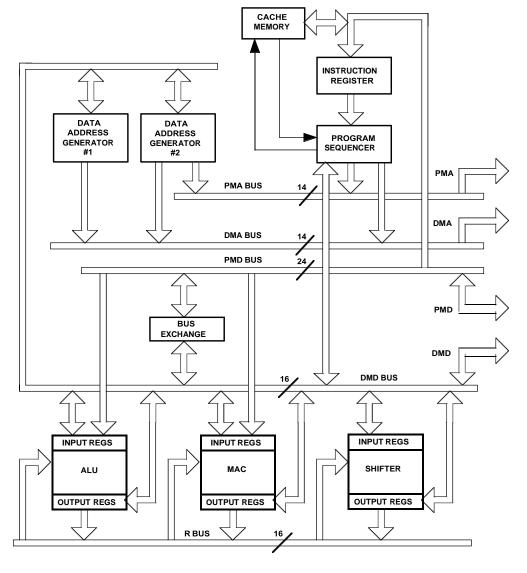

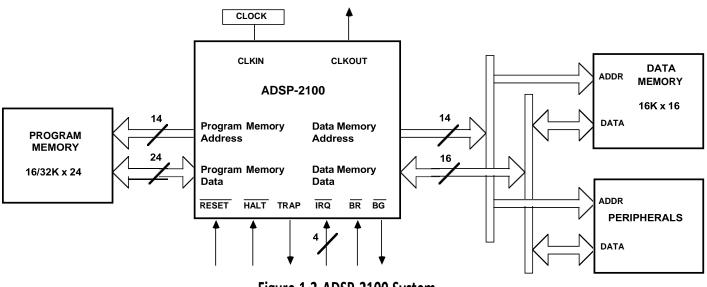

There are several families of commercial DSP devices. Right from the early eighties, when these devices began to appear in the market, they have been used in numerous applications, such as communication, control, computers, Instrumentation, and consumer electronics. The architectural features and the processing power of these devices have been constantly upgraded based on the advances in technology and the application needs. However, their basic versions, most of them have Harvard architecture, a single-cycle hardware multiplier, an address generation unit with dedicated address registers, special addressing modes, on-chip peripherals interfaces. Of the various families of programmable DSP devices that are commercially available, the three most popular ones are those from Texas Instruments, Motorola, and Analog Devices. Texas Instruments was one of the first to come out with a commercial programmable DSP with the introduction of its TMS32010 in 1982.

### Summary of the Architectural Features of three fixed-Points DSPs

| Architectural Feature | TMS320C25          | DSP 56000          | ADSP2100        |

|-----------------------|--------------------|--------------------|-----------------|

| Data representation   | #                  | <u> </u>           | 16-bit fixed    |

| format                | 16-bit fixed       | 24-bit fixed point | point           |

| Hardware multiplier   | 16 x 16            | 24 x 24            | 16 x 16         |

| ALU                   | 32 bits            | 56 bits            | 40 bits         |

|                       |                    |                    | 24-bit program  |

| Internal buses        | 16-bit program bus | 24-bit program bus | bus             |

|                       |                    | 2 x 24-bit data    |                 |

|                       | 16-bit data bus    | buses              | 16-bit data bus |

|                       |                    | 24-bit global      | 16-bit result   |

| External buses         | 16-bit<br>program/data bus | databus<br>24-bit program/data<br>bus | bus<br>24-bit program<br>bus |

|------------------------|----------------------------|---------------------------------------|------------------------------|

| On-chip Memory         | 544 words RAM              | 512 words PROM                        | 16-bit data bus<br>-         |

|                        |                            | 2 x 256 words data                    |                              |

|                        | 4K words ROM               | RAM                                   |                              |

|                        |                            | 2 x 256 words data                    |                              |

|                        |                            | ROM                                   |                              |

|                        | 64 K words                 |                                       | 16K words                    |

| Off-chip memory        | program                    | 64K words program                     | program                      |

|                        | 64k words data             | 2 x 64K words data                    | 16K words data               |

|                        |                            |                                       | 16 words                     |

| Cache memory           | =                          | -                                     | program                      |

| Instruction cycle time | 100 nsec                   | 97.5 nsec.                            | 125 nsecc.                   |

| Special addressing     |                            |                                       |                              |

| modes                  | Bit reversed               | Modulo                                | Modulo                       |

|                        |                            | Bit reversed                          | Bit reversed                 |

| Data address           |                            |                                       |                              |

| generators             | 1                          | 2                                     | 2                            |

|                        | Synchronous serial         |                                       |                              |

| Interfacing features   | I/O                        | Synchronous and                       | DMA                          |

|                        | DMA                        | Asynchronous serial                   |                              |

|                        |                            | I/O DMA                               |                              |

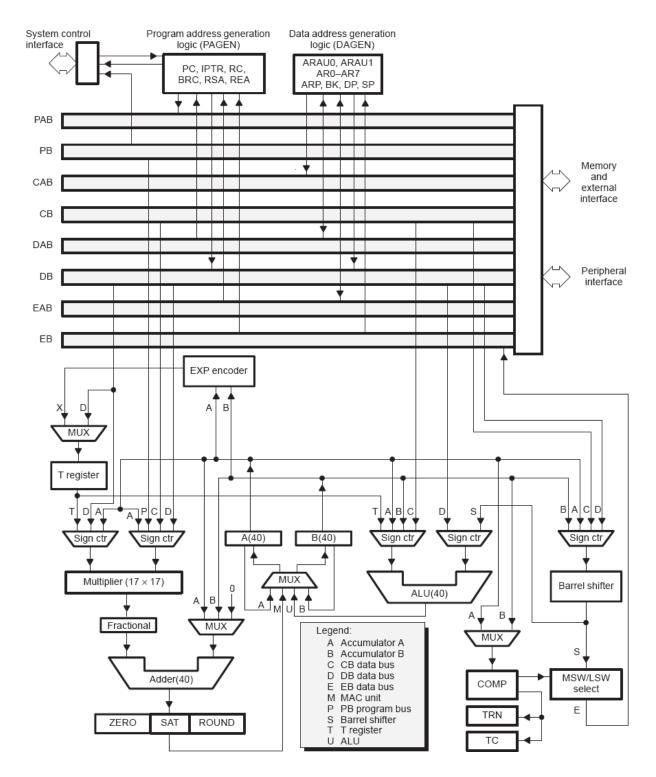

### 3.3. The architecture of TMS320C54xx digital signal processors:

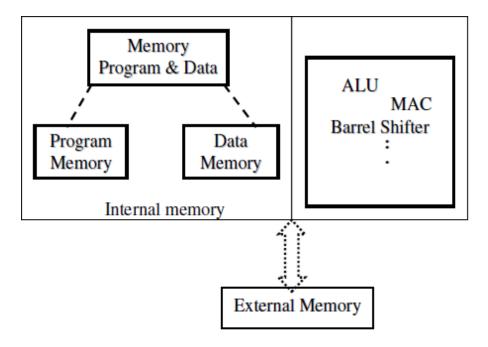

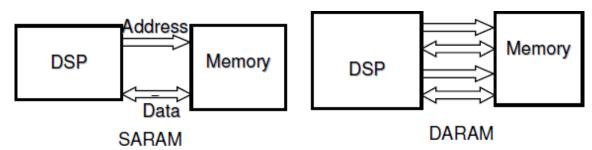

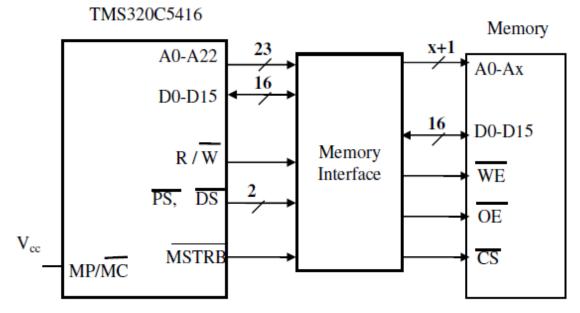

TMS320C54xx processors retain in the basic Harvard architecture of their predecessor, TMS320C25, but have several additional features, which improve their performance over it. Figure 3.1 shows a functional block diagram of TMS320C54xx processors. They have one program and three data memory spaces with separate buses, which provide simultaneous accesses to program instruction and two data operands and enables writing of result at the same time. Part of the memory is implemented on-chip and consists of combinations of ROM, dual-access RAM, and single-access RAM. Transfers between the memory spaces are also possible.

The central processing unit (CPU) of TMS320C54xx processors consists of a 40- bit arithmetic logic unit (ALU), two 40-bit accumulators, a barrel shifter, a 17x17 multiplier, a 40-bit adder, data address generation logic (DAGEN) with its own arithmetic unit, and program address generation logic (PAGEN). These major functional units are supported by a number of registers and logic in the architecture. A powerful instruction set with a hardware-supported, single-instruction repeat and block repeat operations, block memory move instructions, instructions that pack two or three simultaneous reads, and arithmetic instructions with parallel store and load make these devices very efficient for running high-speed DSP algorithms.

Several peripherals, such as a clock generator, a hardware timer, a wait state generator, parallel I/O ports, and serial I/O ports, are also provided on-chip. These peripherals make it convenient to interface the signal processors to the outside world. In these following sections, we examine in detail the various architectural features of the TMS320C54xx family of processors.

Figure 3.1. Functional architecture for TMS320C54xx processors.

### 3.3.1 Bus Structure:

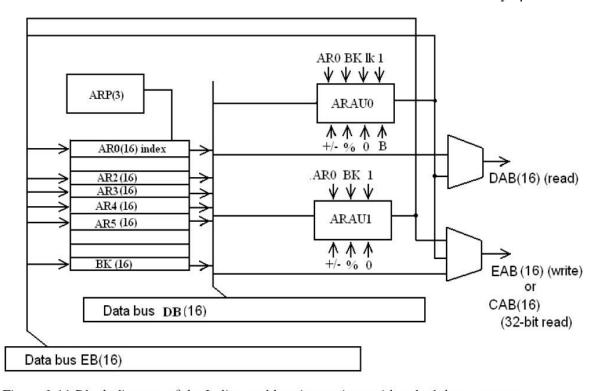

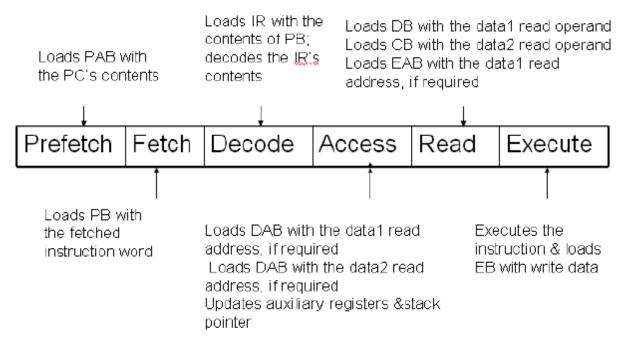

The performance of a processor gets enhanced with the provision of multiple buses to provide simultaneous access to various parts of memory or peripherals. The 54xx architecture is built around four pairs of 16-bit buses with each pair consisting of an address bus and a data bus. As shown in Figure

3.1, these are The program bus pair (**PAB**, **PB**); which carries the instruction code from the program memory. Three data bus pairs (**CAB**, **CB**; **DAB**, **DB**; and **EAB**, **EB**); which interconnected the various units within the CPU. In Addition the pair CAB, CB and DAB, DB are used to read from the data memory, while The pair **EAB**, **EB**; carries the data to be written to the memory. The '54xxcan generate up to two data-memory addresses per cycle using the two auxiliary register arithmeticunit (ARAU0 and ARAU1) in the DAGEN block. This enables accessing two operands simultaneously.

### **3.3.2** Central Processing Unit (CPU):

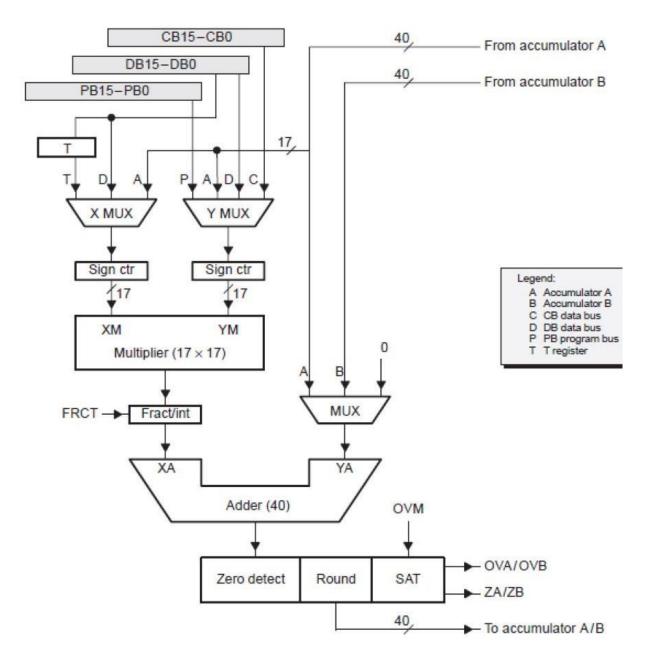

The '54xx CPU is common to all the '54xx devices. The '54xx CPU contains a 40-bitarithmetic logic unit (**ALU**); two 40-bit accumulators (**A** and **B**); a barrel shifter; a

17 x 17-bit multiplier; a 40-bit adder; a compare, select and store unit (**CSSU**); an exponent encoder(**EXP**); a data address generation unit (**DAGEN**); and a program address generation unit (**PAGEN**).

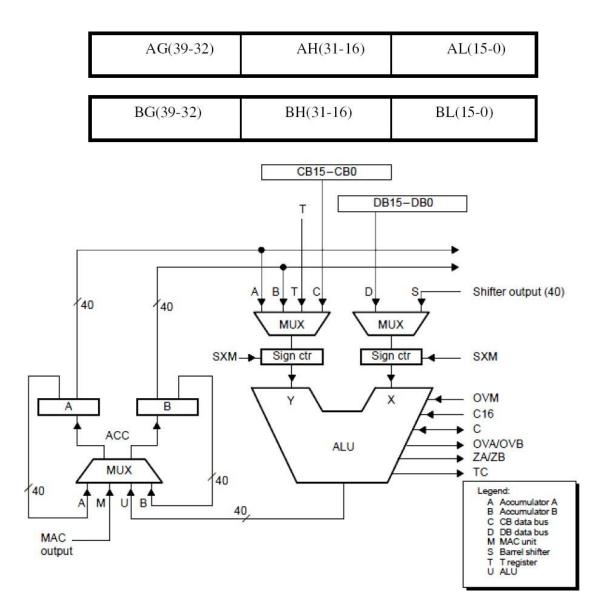

The ALU performs 2's complement arithmetic operations and bit-level Boolean operations on 16, 32, and 40-bit words. It can also function as two separate 16-bit ALUs and perform two 16-bit operations simultaneously. Figure 3.2 show the functional diagram of the ALU of the TMS320C54xx family of devices.

**Accumulators A and B** store the output from the ALU or the multiplier/adder block and provide a second input to the ALU. Each accumulators is divided into three parts: guards bits (bits 39-32), high-order word (bits-31-16), and low-order word (bits 15-0), which can be stored and retrieved individually. Each accumulator is memory-mapped and partitioned. It can be configured as the destination registers. The guard bits are used as a head margin for computations.

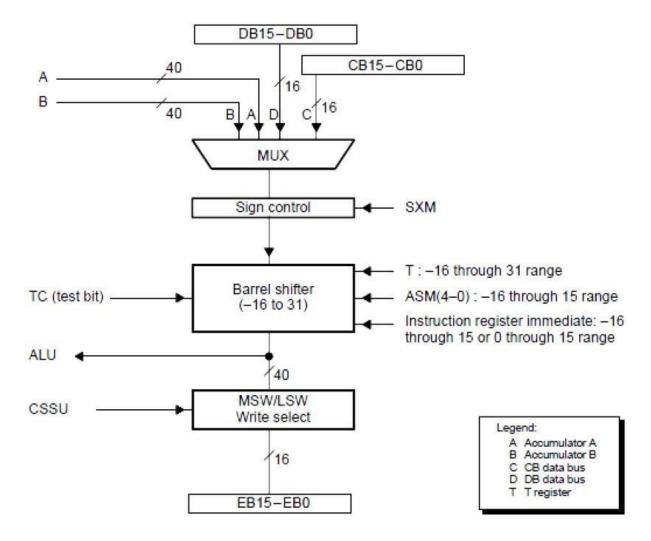

**Figure 3.2**. Functional diagram of the central processing unit of the TMS320C54xxprocessors. **Barrel shifter:** provides the capability to scale the data during an operand read or write.

No overhead is required to implement the shift needed for the scaling operations. The '54xx barrel shifter can produce a left shift of 0 to 31 bits or a right shift of 0 to 16 bits on the input data. The shift count field of status registers ST1, or in the temporary

register T. Figure 3.3 shows the functional diagram of the barrel shifter of TMS320C54xx processors. The barrel shifter and the exponent encoder normalize the values in an accumulator in a single cycle. The LSBs of the output are filled with0s, and the MSBs can be either zero filled or sign extended, depending on the state of the sign-extension mode bit in the status register ST1. An additional shift capability enables the processor to perform numerical scaling, bit extraction, extended arithmetic, and overflow prevention operations.

**Figure 3.3**. Functional diagram of the barrel shifter

**Multiplier/adder unit:** The kernel of the DSP device architecture is multiplier/adder unit. The multiplier/adder unit of TMS320C54xx devices performs 17 x 17 2's complement multiplication with a 40-bit addition effectively in a single instruction cycle.

In addition to the multiplier and adder, the unit consists of control logic for integer and fractional computations and a 16-bit temporary storage register, T. Figure 3.4 show the functional diagram of the multiplier/adder unit of TMS320C54xx processors. The compare, select, and store unit (CSSU) is a hardware unit specifically incorporated to accelerate the add/compare/select operation. This operation is essential to implement the *Viterbi* algorithm used in many signal-processing applications. The exponent encoder unit supports the EXP instructions, which stores in the T register the number of leading redundant bits of the accumulator content. This information is useful while shifting the accumulator content for the purpose of scaling.

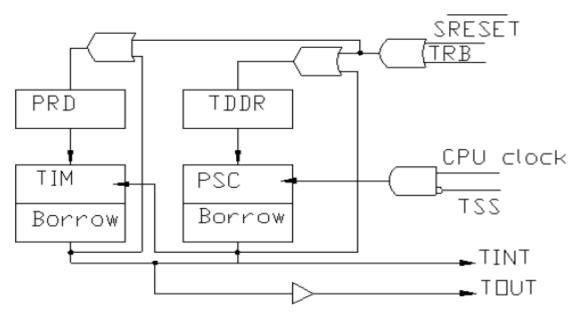

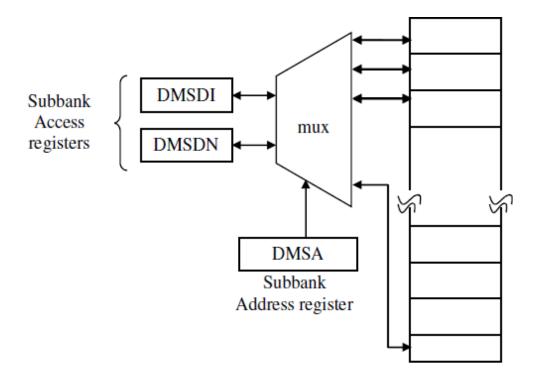

**Figure 3.4.** Functional diagram of the multiplier/adder unit of TMS320C54xx processors. **3.3.3** Internal Memory and Memory-Mapped Registers:

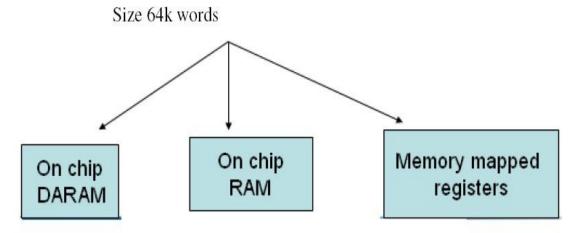

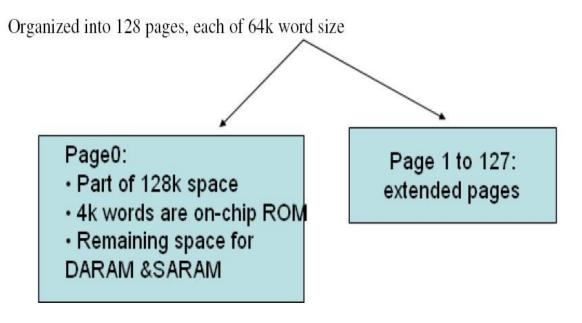

The amount and the types of memory of a processor have direct relevance to the efficiency and performance obtainable in implementations with the processors. The '54xx memory is organized into three individually selectable spaces: program, data, and I/O spaces. All '54xx devices contain both RAM and ROM. RAM can be either dual-access type (DARAM) or single-access type (SARAM). Theon-chip RAM for these processors is organized in pages having 128 word locations on each page.

The '54xx processors have a number of CPU registers to support operand addressing and computations. The CPU registers and peripherals registers are all located on page 0 of the data memory. Figure 3.5(a) and (b) shows the internal CPU registers and peripheral registers with their addresses. The processors mode status (PMST) registers

that is used to configure the processor. It is a memory-mapped register located at address 1Dh on page 0 of the RAM. A part of on-chip ROM may contain a boot loader and look-up tables for function such as sine, cosine,  $\mu$ - law, and A- law.

| NAME | DEC | HEX | DESCRIPTION                                |

|------|-----|-----|--------------------------------------------|

| IMR  | 0   | 0   | Interrupt mask register                    |

| IFR  | 1   | 1   | Interrupt flag register                    |

| _    | 2-5 | 2-5 | Reserved for testing                       |

| ST0  | 6   | 6   | Status register 0                          |

| ST1  | 7   | 7   | Status register 1                          |

| AL   | 8   | 8   | Accumulator A low word (15-0)              |

| AH   | 9   | 9   | Accumulator A high word (31-16)            |

| AG   | 10  | A   | Accumulator A guard bits (39-32)           |

| BL   | 11  | В   | Accumulator B low word (15-0)              |

| вн   | 12  | c   | Accumulator B high word (31-16)            |

| BG   | 13  | D   | Accumulator B guard bits (39-32)           |

| TREG | 14  | E   | Temporary register                         |

| TRN  | 15  | F   | Transition register                        |

| AR0  | 16  | 10  | Auxiliary register 0                       |

| AR1  | 17  | 11, | Auxiliary register 1                       |

| AR2  | 18  | 12  | Auxiliary register 2                       |

| AR3  | 19  | 13  | Auxiliary register 3                       |

| AR4  | 20  | 14  | Auxiliary register 4                       |

| AR5  | 21  | 15  | Auxiliary register 5                       |

| AR6  | 22  | 16  | Auxiliary register 6                       |

| AR/  | 23  | 17  | Auxiliary register 7                       |

| SP   | 24  | 18  | Stack pointer register                     |

| вк   | 25  | 19  | Circular buffer size register              |

| BRC  | 26  | 1A  | Block repeat counter                       |

| RSA  | 27  | 1B  | Block repeat start address                 |

| REA  | 28  | 10  | Block repeat end address                   |

| PMST | 29  | 1D  |                                            |

| XPC  | 30  | 1E  | Processor mode status (PMST) registe       |

|      | 31  | 1F  | Extended program page register<br>Reserved |

Figure 3.5(a) Internal memory-mapped registers of TMS320C54xx processors

| ADCRE  |             | RESS  |                                         |

|--------|-------------|-------|-----------------------------------------|

| NAME   | DEC         | HEX   | DESCRIPTION                             |

| DRR20  | 32          | 20    | McBSP 0 Data Receive Register 2         |

| DRR10  | 33          | 21    | McBSP 0 Data Receive Register 1         |

| DXR20  | 34          | 22    | McBSP 0 Data Transmit Register 2        |

| DXR10  | 35          | 23    | McBSP 0 Data Transmit Register 1        |

| TIM    | 36          | 24    | Timer Register                          |

| PRD    | 37          | 25    | Timer Period Register                   |

| TCR    | 38          | 26    | Timer Control Register                  |

|        | 39          | 27    | Reserved                                |

| SWWSR  | 40          | 28    | Software Watt-State Register            |

| BSCR   | 41          | 29    | Bank-Switching Control Register         |

| _      | 42          | 2A    | Reserved                                |

| SWCR   | 43          | 2B    | Software Watt-State Control Register    |

| HPIC   | 44          | 20    | HPI Control Register (HMODE = 0 only)   |

| _      | 45-47       | 2D-2F | Reserved                                |

| DRR22  | 48          | 30    | McBSP 2 Data Receive Register 2         |

| DRR12  | 49          | 31    | McBSP 2 Data Receive Register 1         |

| DXR22  | 50          | 32    | McBSP 2 Data Transmit Register 2        |

| DXR12  | 51          | 33    | McBSP 2 Data Transmit Register 1        |

| SPSA2  | 52          | 34    | McBSP 2 Subbank Address Register        |

| SPSD2  | 53          | 35    | McBSP 2 Subbank Data Register           |

| _      | 54-55       | 36-37 | Reserved                                |

| SPSAO  | 56          | 38    | McBSP 0 Subbank Address Register        |

| SPSDO  | 57          | 39    | McBSP 0 Subbank Data Register           |

|        | 58-59       | 3A-3B | Reserved                                |

| GPIOCR | 60          | 3C    | General-Purpose I/O Control Register    |

| GPIOSR | 61          | 3D    | General-Purpose I/O Status Register     |

| CSIDR  | 62          | 3E    | Device ID Register                      |

| CSIDIN | 63          | 3F    | Reserved                                |

| DRR21  | 64          | 40    | McBSP 1 Data Receive Register 2         |

| DRR11  | 65          | 41    | McBSP 1 Data Receive Register 1         |

| DXR21  | 66          | 42    | McBSP 1 Data Transmi: Register 2        |

| DXR11  | 67          | 43    | McBSP 1 Data Transmit Register 1        |

| DARTI  | 68-71       | 44-47 | Reserved                                |

| SPSA1  | 72          | 48    | McBSP 1 Subbank Address Register        |

| SPSD1  | 73          | 49    | McBSP 1 Subbank Data Register           |

| 3F3U1  | 74–83       | 4A-53 | Reserved                                |

| DMPREC | 74-63<br>84 | 54    | DMA Priority and Enable Control Registe |

|        | 85          | 55    | DMA Subbank Address Register            |

| DMSA   | 85          | 22    | DIVIA SUDDANK Address Register          |

**Figure 3.5(b).** peripheral registers for the TMS320C54xx processors

# Status registers (ST0,ST1):

**ST0:** Contains the status of flags (OVA, OVB, C, TC) produced by arithmetic operations & bit manipulations.

**ST1:** Contain the status of various conditions & modes. Bits of ST0&ST1registers can be set or clear with the SSBX & RSBX instructions.

PMST: Contains memory-setup status & control information.

## Status register0 diagram:

| ARP     | TC   | С    | OVA  | OVB | DP    |

|---------|------|------|------|-----|-------|

| (15-13) | (12) | (11) | (10) | (9) | (8-0) |

Figure 3.6(a). ST0 diagram

ARP: Auxiliary register pointer.

TC: Test/control flag.

C: Carry bit.

OVA: Overflow flag for accumulator A. OVB: Overflow flag for accumulator B.

DP: Data-memory page pointer.

# Status register1 diagram:

| BR | .AF(15) | CPL  | XF   | НМ   | INTM | 0    | OVM | SXM | C16 | FRCT(6) | CMPT(5) | ASM   |

|----|---------|------|------|------|------|------|-----|-----|-----|---------|---------|-------|

|    |         | (14) | (13) | (12) | (11) | (10) | (9) | (8) | (7) |         |         | (4-0) |

|    |         |      |      |      |      |      |     |     |     |         |         |       |

|    |         |      |      |      |      |      |     |     |     |         |         |       |

Figure 3.6(b). ST1 diagram

## BRAF: Block repeat active flag

BRAF=0, the block repeat is deactivated.

BRAF=1, the block repeat is activated.

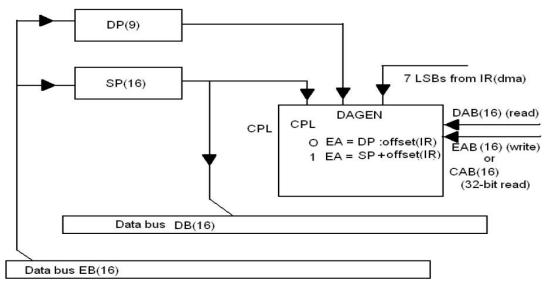

# CPL: Compiler mode

CPL=0, the relative direct addressing mode using data page pointer is selected.

CPL=1, the relative direct addressing mode using stack pointer is selected.

**HM:** Hold mode, indicates whether the processor continues internal execution or acknowledge for external interface.

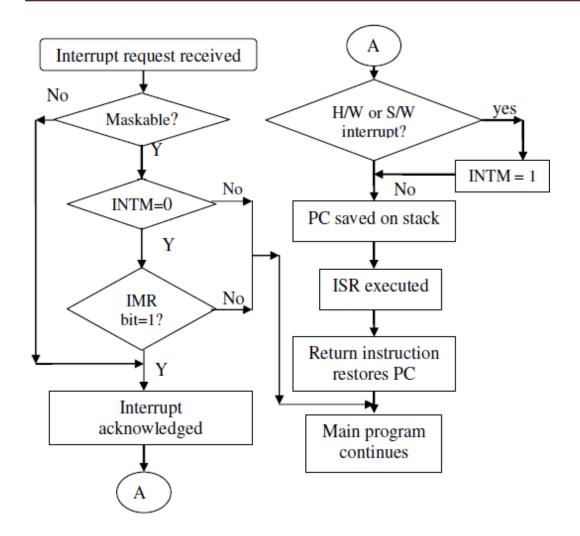

# INTM: Interrupt mode, it globally masks or enables all interrupts.

INTM=0\_all unmasked interrupts are enabled.

INTM=1\_all masked interrupts are disabled.

0: Always read as 0

#### OVM: Overflow mode.

OVM=1\_the destination accumulator is set either the most positive value or the most negative value. OVM=0\_the overflowed result is in destination accumulator.

## SXM: Sign extension mode.

SXM=0 \_Sign extension is suppressed.

SXM=1\_Data is sign extended

#### C16: Dual 16 bit/double-Precision arithmetic mode.

C16=0\_ALU operates in double-Precision arithmetic mode.

C16=1\_ALU operates in dual 16-bit arithmetic mode.

#### FRCT: Fractional mode.

FRCT=1\_the multiplier output is left-shifted by 1bit to compensate an extra sign bit.

## CMPT: Compatibility mode.

CMPT=0\_ ARP is not updated in the indirect addressing mode.

CMPT=1\_ARP is updated in the indirect addressing mode.

#### ASM: Accumulator Shift Mode.

5 bit field, & specifies the Shift value within -16 to 15 range.

## Processor Mode Status Register (PMST):

| IPTR(15-7) | MP/MC(6) | OVLY(5) | AVIS(4) | DROM(3) | CLKOFF(2) | SMUL(1) | SST(0) |

|------------|----------|---------|---------|---------|-----------|---------|--------|

|            |          |         |         |         |           |         |        |

Figure 3.6(c).PMST register diagram

**INTR: Interrupt vector pointer**, point to the 128-word program page where the interrupt vectors reside.

MP/MC: Microprocessor/Microcomputer mode,

MP/MC=0, the on chip ROM is enabled.

MP/MC=1, the on chip ROM is enabled.

**OVLY: RAM OVERLAY,** OVLY enables on chip dual access data RAM blocks to be mapped into program space.

**AVIS:** It enables/disables the internal program address to be visible at the address pins.

**DROM: Data ROM**, DROM enables on-chip ROM to be mapped into data space.

CLKOFF: CLOCKOUT off.

# SMUL: Saturation on Multiplication

#### SST: Saturation on Store.

## 3.4 Data Addressing Modes of TMS320C54X Processors:

Data addressing modes provide various ways to access operands to execute instructions and place results in the memory or the registers. The 54XX devices offer seven basic addressing modes

- 1. Immediate addressing.

- 2. Absolute addressing.

- 3. Accumulator addressing.

- 4. Direct addressing.

- 5. Indirect addressing.

- 6. Memory mapped addressing

- 7. Stack addressing.

## 3.4.1 Immediate addressing:

The instruction contains the specific value of the operand. The operand can be short (3,5,8 or 9 bit in length) or long (16 bits in length). The instruction syntax for short operands occupies one memory location,

Example: LD #20, DP.

RPT #0FFFFh.

#### 3.4.2 Absolute Addressing:

The instruction contains a specified address in the operand.

- 1. Dmad addressing. MVDK Smem, dmad, MVDM dmad, MMR

- 2. Pmad addressing. MVDP Smem,pmad, MVPD pmem,Smad

- 3. PA addressing. PORTR PA, Smem,

- 4.\*(lk) addressing.

#### 3.4.3 Accumulator Addressing:

Accumulator content is used as address to transfer data between Program and Data memory.

Ex: READA \*AR2

#### 3.4.4 Direct Addressing:

Base address + 7 bits of value contained in instruction = 16 bit address. A page of 128 locations can be accessed without change in DP or SP.Compiler mode bit (CPL) in ST1 register is used.

If CPL = 0 Selects DP

CPL = 1 selects SP,

It should be remembered that when SP is used instead of DP, the effective address is computed by adding the 7-bit offset to SP

Figure 3.7 Block diagram of the direct addressing mode for TMS320C54xx Processors.

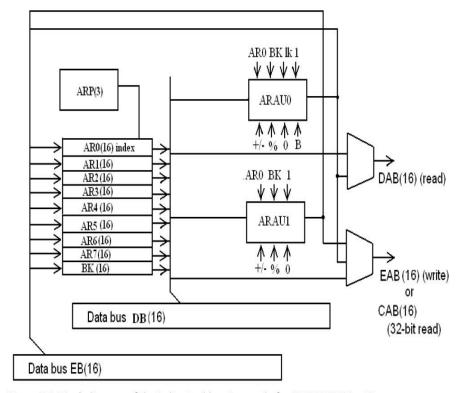

## 3.4.1 Indirect Addressing:

□ Data space is accessed by address present in an auxiliary register.

TMS320C54xx have 8, 16 bit auxiliary register (AR0 - AR 7). Two auxiliary register arithmetic units (ARAU0 & ARAU1)

Used to access memory location in fixed step size. AR0 register is used for indexed and bit reverse addressing modes.

□For single – operand addressing

MOD \_ type of indirect addressing

ARF \_ AR used for addressing

ARP depends on (CMPT) bit in ST1

CMPT = 0, Standard mode, ARP set to zero

CMPT = 1, Compatibility mode, Particularly AR selected by ARP

Figure 3.8 Block diagram of the indirect addressing mode for TMS320C54xx Processors.

| Operand syntax | Function                         |

|----------------|----------------------------------|

| *ARx           | Addr = ARx;                      |

| *ARx -         | Addr = ARx ; ARx = ARx -1        |

| *ARx +         | Addr = ARx;  ARx = ARx + 1       |

| *+ARx          | Addr = ARx+1; ARx = ARx +1       |

| *ARx - 0B      | Addr = ARx ; ARx = B(ARx - AR0)  |

| *ARx - 0       | Addr = Arx ; ARx = ARx - AR0     |

| *ARx + 0       | Addr = Arx ; ARx = ARx + AR0     |

| *ARx + 0B      | Addr = ARx ; ARx = B(ARx + AR0)  |

| *ARx - %       | Addr = ARx ; ARx = circ(ARx - 1) |

| *+AR – 0% | Addr = Arx; ARx = circ(ARx - AR0) |

|-----------|-----------------------------------|

| *ARx + %  | Addr = ARx ; ARx = circ (ARx + 1) |

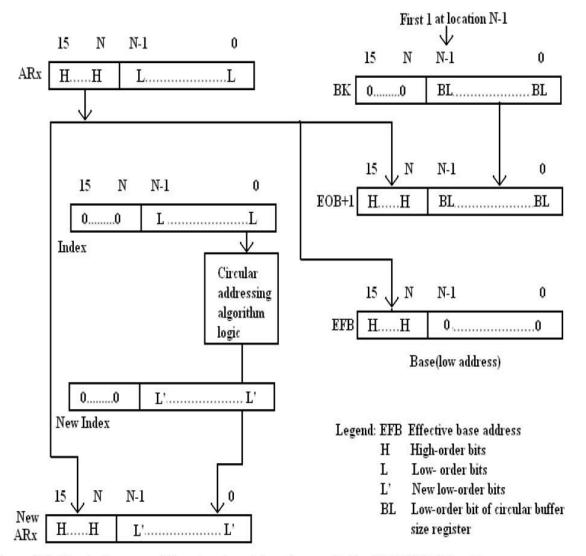

Table 3.2 Indirect addressing options with a single data –memory operand. Circular Addressing;

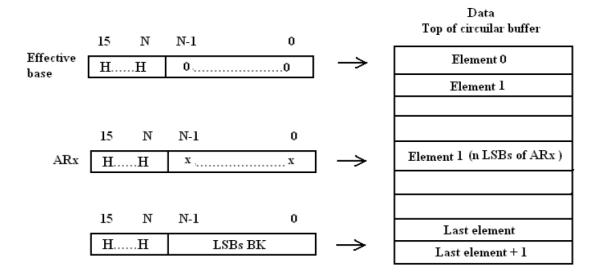

- Used in convolution, correlation and FIR filters.

- ➤ A circular buffer is a sliding window contains most recent data. Circular buffer of size R must start on a N-bit boundary, where 2N > R.

- ➤ □The circular buffer size register (BK): specifies the size of circular buffer.

- > Effective base address (EFB): By zeroing the N LSBs of a user selected AR (ARx).

- ➤ □End of buffer address (EOB): By repalcing the N LSBs of ARx with the N LSBs of BK.

If 0 \_ index + step < BK; index = index + step;</p>

else if index + step \_ BK; index = index + step BK;

else if index + step < 0; index + step + BK

Figure 3.9 Block diagram of the circular addressing mode for TMS320C54xx Processors.

Figure 3.10 circular addressing mode implementation for TMS320C54xx Processors.

## Bit-Reversed Addressing:

- Used for FFT algorithms.

- ARO specifies one half of the size of the FFT.

- The value of AR0 = 2N-1: N = integer FFT size = 2N

- ARO + AR (selected register) = bit reverse addressing.

- The carry bit propagating from left to right.

## Dual-Operand Addressing:

Dual data-memory operand addressing is used for instruction that simultaneously perform two reads (32-bit read) or a single read (16-bit read) and a parallel store (16-bit store) indicated by two vertical bars, II. These instructions access operands using indirect addressing mode.

If in an instruction with a parallel store the source operand the destination operand point to the same location, the source is read before writing to the destination. Only 2 bits are available in the instruction code for selecting each auxiliary register in this mode. Thus, just four of the auxiliary registers, AR2-AR5, can be used, The ARAUs together with these registers, provide capability to access two operands in a single cycle. Figure 3.11 shows how an address is generated using dual data- memory operand addressing.

| 15 - 8 | 7 - 6 | 5 - 4 | 3 - 2 | 1-0 |

|--------|-------|-------|-------|-----|

| Opcode | Xmod  | Xar   | Ymod  | Yar |

| Name   | Function                                                                         |

|--------|----------------------------------------------------------------------------------|

| Opcode | This field contains the operation code for the instruction                       |

| Xmod   | Defined the type of indirect addressing mode used for accessing the Xmem operand |

| XAR    | Xmem AR selection field defines the AR that contains the address of Xmem         |

| Ymod   | Defies the type of inderect addressing mode used for accessing the Ymem operand  |

| Yar    | Ymem AR selection field defines the AR that contains the address of Ymem         |

Table 3.3. Function of the different field in dual data memory operand addressing

Figure 3.11 Block diagram of the Indirect addressing options with a dual data –memory operand.

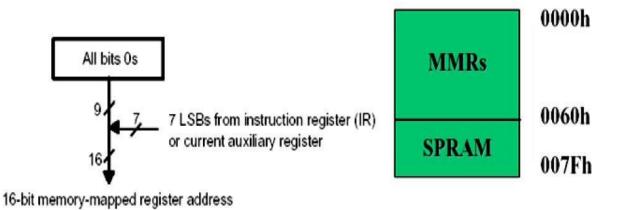

## **3.4.6.** Memory-Mapped Register Addressing:

- Used to modify the memory-mapped registers without affecting the current data page.

- pointer (DP) or stack-pointer (SP)

- Overhead for writing to a register is minimal

- Works for direct and indirect addressing

- Scratch –pad RAM located on data PAGEO can be modified

- ➤ STM #x, DIRECT

- > STM #tbl, AR1

Figure 3.12.16 bit memory mapped register address generation.

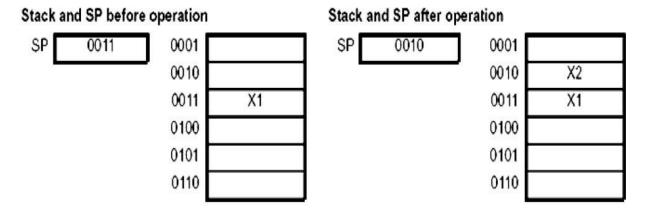

## 3.4.7 Stack Addressing:

- Used to automatically store the program counter during interrupts and subroutines.

- Can be used to store additional items of context or to pass data values.

- Uses a 16-bit memory-mapped register, the stack pointer (SP).

- PSHD X2

Figure 3.13. Values of stack &SP before and after operation.

## 3.5. Memory Space of TMS320C54xx Processors

- A total of 128k words extendable up to 8192k words.

- > Total memory includes RAM, ROM, EPROM, EEPROM or Memory mapped peripherals.

- ➤ □Data memory: To store data required to run programs & for external memory mapped registers.

Program memory: To store program instructions &tables used in the execution of programs.

OVLY

DROM

Table 3.4. Function of different pin PMST register

RAM in data space

RAM in program space

ROM not in data space ROM in data space

| PMS1 bit | Logic | On- | chip memory configuration |  |

|----------|-------|-----|---------------------------|--|

| MP/M0    | C     | 0   | ROM enabled               |  |

|          |       | 1   | ROM not available         |  |

|          |       |     |                           |  |

|          |       |     |                           |  |

0

0

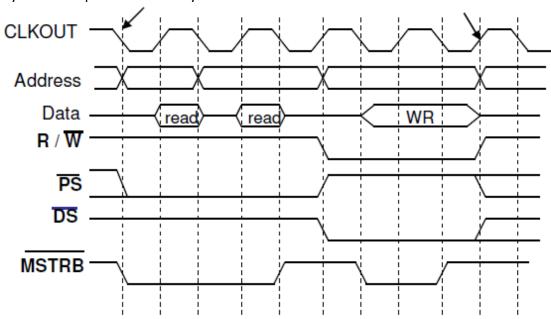

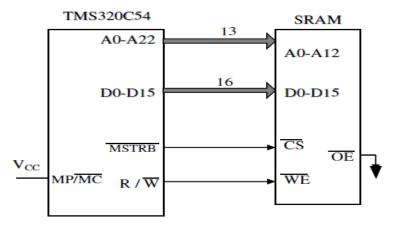

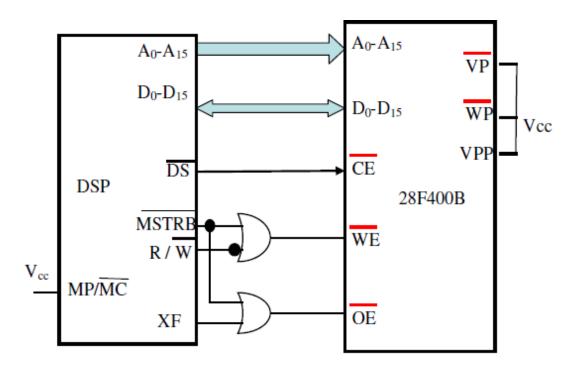

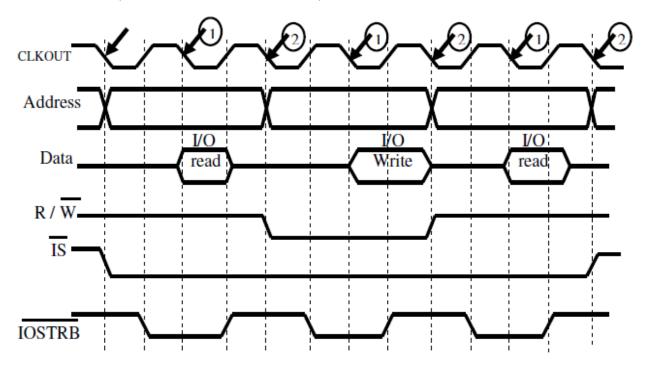

| Hex          | Page 0 Program                                   | Hex          | Page 0 Program                                | Hex          | Data                              |