## **LECTURE NOTES**

## ON

## **EMBEDDED SYSTEMS DESIGN**

### IV B. Tech I semester (R15)

**Faculty Members**

N.SURESH Asst.Professor ECE Dept

#### MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

#### IV Year B.Tech. ECE-I Sem

#### **CORE ELECTIVE – III**

#### EMBEDDED SYSTEMS DESIGN (R15A0424)

#### COURSE OBJECTIVES:

For embedded systems, the course will enable the students to:

- 1. Understand the basics of an embedded system.

- 2. Understand the typical components of an embedded system.

- 3. To understand different communication interfaces.

- 4. To learn the design process of embedded system applications.

- 5. To understands the RTOS and inter-process communication.

#### UNIT-I INTRODUCTION TO EMBEDDED SYSTEMS

History of embedded systems, Classification of embedded systems based on generation and complexity, Purpose of embedded systems, The embedded system design process-requirements, specification, architecture design, designing hardware and software, components, system integration, Applications of embedded systems, and characteristics of embedded systems.

#### UNIT-II TYPICAL EMBEDDED SYSTEM

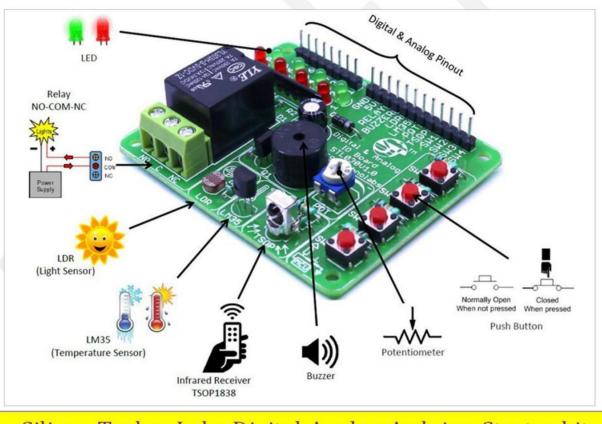

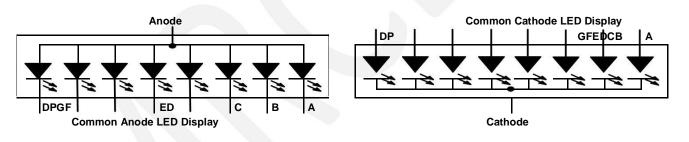

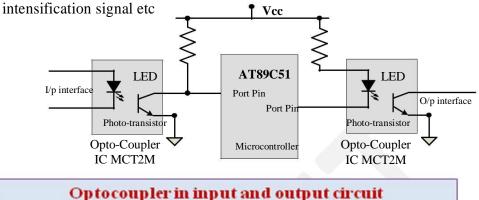

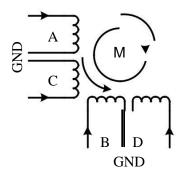

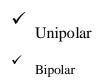

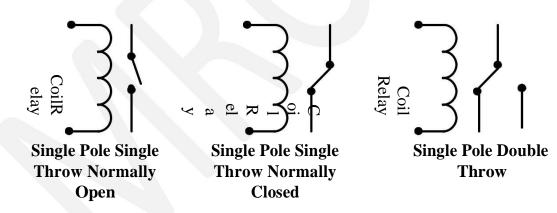

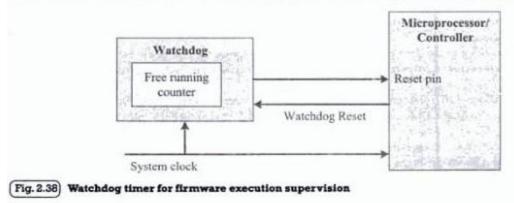

Core of the embedded system-general purpose and domain specific processors, ASICs, PLDs, COTs; Memory-ROM, RAM, memory according to the type of interface, memory shadowing, memory selection for embedded systems, Sensors, actuators, I/O components: seven segment LED, relay, piezo buzzer, push button switch, other sub-systems: reset circuit, brownout protection circuit, oscillator circuit real time clock, watch dog timer.

#### UNIT-III COMMUNICATION INTERFACE

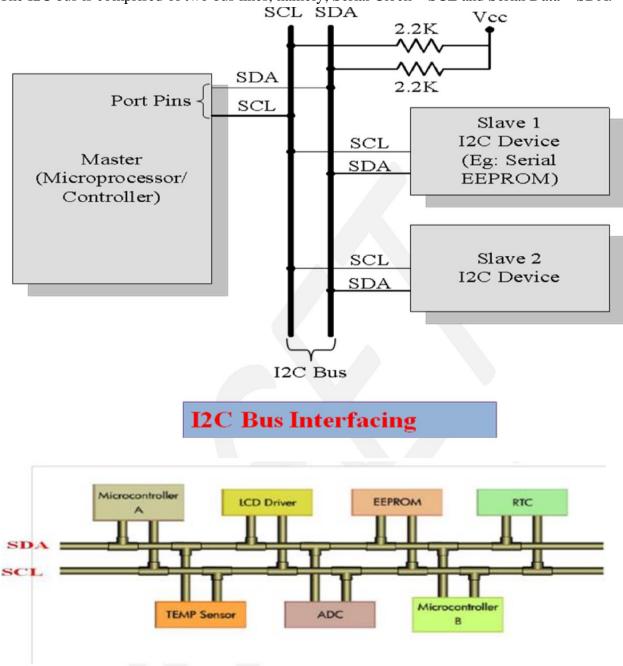

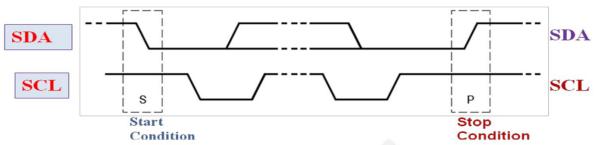

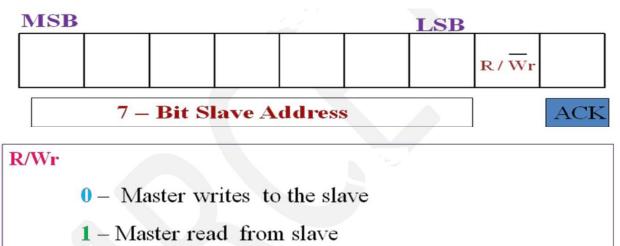

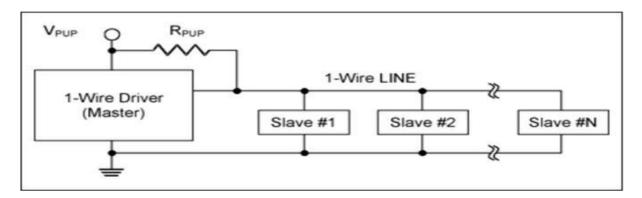

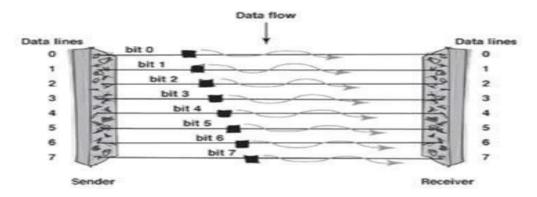

Onboard communication interfaces-I2C, SPI, CAN, parallel interface;

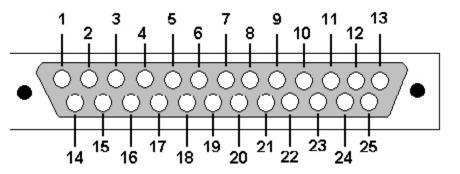

**External communication interfaces**-RS232 and RS485, USB, infrared, Bluetooth, Wi-Fi, ZigBee, GPRS, GSM.

#### UNIT-IV EMBEDDED FIRMWARE DESIGN AND DEVELOPMENT

Embedded firmware design approaches-super loop based approach, operating system based approach; embedded firmware development languages-assembly language based development, high level language based development.

#### UNIT-V RTOS BASED EMBEDDED SYSTEM DESIGN

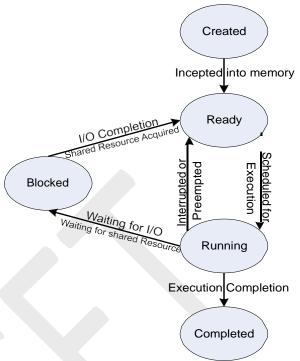

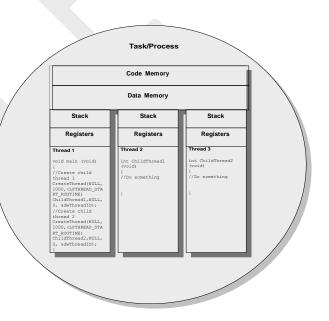

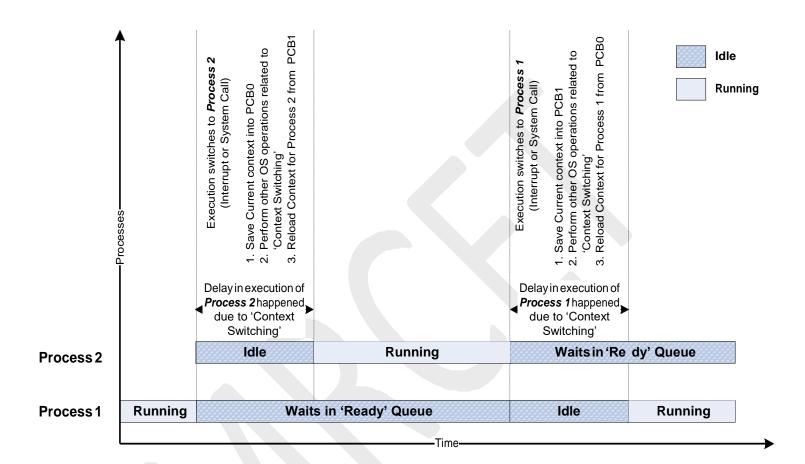

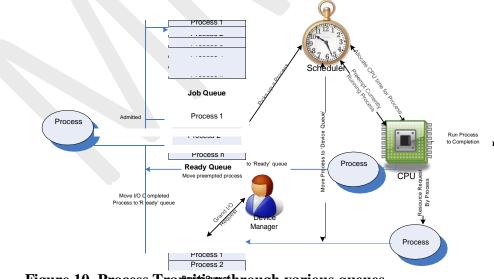

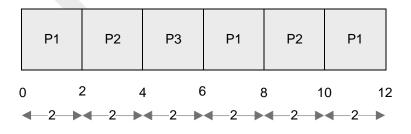

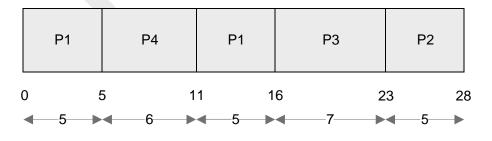

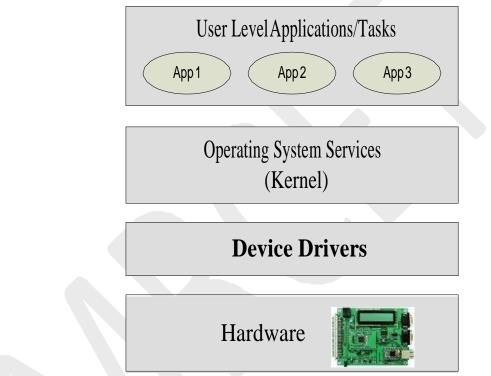

Operating system basics, types of operating systems, tasks, process and threads, multiprocessing and multitasking, task scheduling: non-pre-emptive and pre-emptive scheduling; task communication-shared memory, message passing, Remote Procedure Call and Sockets, Task Synchronization: Task Communication/ Synchronization Issues, Task Synchronization Techniques

#### **TEXT BOOKS:**

- 1. Introduction to Embedded Systems shibu k v, Mc Graw Hill Education.

- 2. Computers as Components Wayne Wolf, Morgan Kaufmann (second edition).

#### **REFERENCE BOOKS:**

- 1. Embedded System Design -frank vahid, tony grivargis, john Wiley.

- 2. Embedded Systems- An integrated approach Lyla b das, Pearson education 2012.

- 3. Embedded Systems Raj Kamal, TMH

#### **COURSE OUTCOMES:**

Upon completion of this course, the students will be able to:

- 1. Understand the design process of an embedded system

- 2. Understand typical embedded System & its components

- 3. Understand embedded firmware design approaches

- 4. Learn the basics of OS and RTOS

**ESD UNIT-1 NOTES**

# EMBEDDED SYSTEM DESIGN IV YEAR ECE

## UNIT-I INTRODUCTION TO EMBEDDED SYSTEMS

#### 1. Introduction to Embedded Systems

#### What is Embedded System?

#### (DEC2016, March-2017.)

An Electronic/Electro mechanical system which is designed to perform a specific function and is a combination of both hardware and firmware (Software)

E.g. Electronic Toys, Mobile Handsets, Washing Machines, Air Conditioners, Automotive Control Units, Set Top Box, DVD Player etc...

#### **Embedded Systems are:**

Unique in character and behavior

With specialized hardware and software

#### **Embedded Systems Vs General Computing Systems:**

(March-2017)

| General Purpose Computing System                                                                                                                                     | Embedded System                                                                                                                |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| A system which is a combination of generic<br>hardware and General Purpose Operating System<br>for executing a variety of applications                               | A system which is a combination of special<br>purpose hardware and embedded OS for<br>executing a specific set of applications |  |

| Contain a General Purpose Operating System<br>(GPOS)                                                                                                                 | May or may not contain an operating system<br>for functioning                                                                  |  |

| Applications are alterable (programmable) by<br>user (It is possible for the end user to re-install the<br>Operating System, and add or remove user<br>applications) | The firmware of the embedded system is<br>pre-programmed and it is non-alterable by<br>end-user                                |  |

| Performance is the key deciding factor on the selection of the system. Always "Faster is Better"                                                                     | Application specific requirements (like<br>performance, power requirements, memory<br>usage etc) are the key deciding factors  |  |

| Less/not at all tailored towards reduced operating<br>power requirements, options for different levels<br>of power management.                                       | Highly tailored to take advantage of the<br>power saving modes supported by hardware<br>and Operating System                   |  |

| Response requirements are not time critical                                                                                                                          | For certain category of embedded systems<br>like mission critical systems, the response<br>time requirement is highly critical |  |

| Need not be deterministic in execution behavior                                                                                                                      | Execution behavior is deterministic for<br>certain type of embedded systems like "Hard<br>Real Time" systems                   |  |

#### **History of Embedded Systems:**

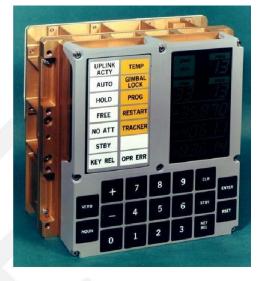

- First Recognized Modern Embedded System: Apollo Guidance Computer (AGC) developed by <u>Charles Stark Draper</u> at the MIT Instrumentation Laboratory.

- It has two modules

- 1.Command module(CM) 2.Lunar Excursion module(LEM)

- RAM size 256, 1K, 2K words

- ROM size 4K,10K,36K words

- Clock frequency is 1.024MHz

- 5000,3-input RTL NOR gates are used

- User interface is DSKY(display/Keyboard)

(March-2017)

First Mass Produced Embedded System: Autonetics D-17 Guidance computer for Minuteman-I missile

#### **Classification of Embedded Systems:**

#### **Based on Generation**

**Based on Complexity & Performance Requirements**

Based on deterministic behavior

Based on Triggering

#### 1. <u>Embedded Systems - Classification based on</u> <u>Generation</u>

•

**First Generation:** The early embedded systems built around 8-bit microprocessors like 8085 and Z80 and 4-bit microcontrollers

#### EX. stepper motor control units, Digital Telephone Keypads etc.

Second Generation: Embedded Systems built around 16-bit microprocessors and 8 or 16-bit microcontrollers, following the first generation embedded systems **EX.SCADA, Data Acquisition Systems etc.**

**Third Generation:** Embedded Systems built around high performance 16/32 bit Microprocessors/controllers, Application Specific Instruction set processors like Digital Signal Processors (DSPs), and Application Specific Integrated Circuits (ASICs). The instruction set is complex and powerful.

EX. Robotics, industrial process control, networking etc.

N SURESH, Dept of ECE

#### Page 3

**Fourth Generation:** Embedded Systems built around System on Chips (SoC's), Reconfigurable processors and multicore processors. It brings high performance, tight integration and miniaturization into the embedded device market

EX Smart phone devices, MIDs etc.

2. <u>Embedded Systems - Classification based on Complexity & Performance</u>

**Small Scale:** The embedded systems built around low performance and low cost 8 or 16 bit microprocessors/ microcontrollers. It is suitable for simple applications and where performance is not time critical. It may or may not contain OS.

**Medium Scale**: Embedded Systems built around medium performance, low cost 16 or 32 bit microprocessors / microcontrollers or DSPs. These are slightly complex in hardware and firmware. It may contain GPOS/RTOS.

**Large Scale/Complex:** Embedded Systems built around high performance 32 or 64 bit RISC processors/controllers, RSoC or multi-core processors and PLD. It requires complex hardware and software. These system may contain multiple processors/controllers and co-units/hardware accelerators for offloading the processing requirements from the main processor. It contains RTOS for scheduling, prioritization and management.

**3.** <u>Embedded Systems - Classification Based on deterministic behavior:</u> It is applicable for Real Time systems. The application/task execution behavior for an embedded system can be either deterministic or non-deterministic

#### These are classified in to two types

**1. Soft Real time Systems:** Missing a deadline may not be critical and can be tolerated to a certain degree

**2** Hard Real time systems: Missing a program/task execution time deadline can have catastrophic consequences (financial, human loss of life, etc.)

#### 4. Embedded Systems - Classification Based on Triggering:

#### These are classified into two types

- **1.** Event Triggered : Activities within the system (e.g., task run-times) are dynamic and depend upon occurrence of different events .

- 2 **Time triggered:** Activities within the system follow a statically computed schedule (i.e., they are allocated time slots during which they can take place) and thus by nature are predictable.

**ESD UNIT-1 NOTES**

#### Major Application Areas of Embedded Systems:

Consumer Electronics: Camcorders, Cameras etc.

Household Appliances: Television, DVD players, washing machine, Fridge, Microwave Oven etc.

Home Automation and Security Systems: Air conditioners, sprinklers, Intruder detection alarms, Closed Circuit Television Cameras, Fire alarms etc.

####

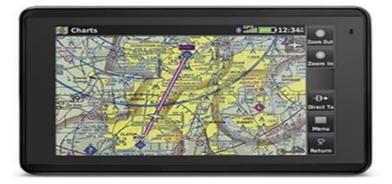

Automotive Industry: Anti-lock breaking systems (ABS), Engine Control, Ignition Systems, Automatic Navigation Systems etc.

Telecom: Cellular Telephones, Telephone switches, Handset Multimedia Applications etc.

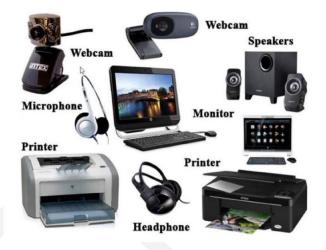

Computer Peripherals: Printers, Scanners, Fax machines etc.

Computer Networking Systems: Network Routers, Switches, Hubs, Firewalls etc.

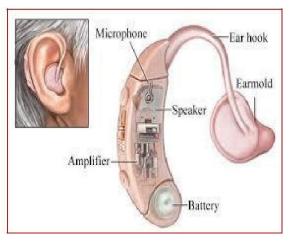

Health Care: Different Kinds of Scanners, EEG, ECG Machines etc.

Measurement & Instrumentation: Digital multi meters, Digital CROs, Logic Analyzers PLC systems etc.

Banking & Retail: Automatic Teller Machines (ATM) and Currency counters, Point of Sales (POS)

Card Readers: Barcode, Smart Card Readers, Hand held Devices etc.

#### **Purpose of Embedded Systems:**

#### (**DEC2016**)

Each Embedded Systems is designed to serve the purpose of any one or a combination of the following tasks.

- Data Collection/Storage/Representation

- Data Communication

- Data (Signal) Processing

- Monitoring

- o Control

- Application Specific User Interface

#### 1. Data Collection/Storage/Representation:-

- ÷ Performs acquisition of data from the external world.

- \* The collected data can be either analog or digital

- \* Data collection is usually done for storage, analysis, manipulation and transmission

- The collected data may be stored directly in the system or may be transmitted to some other systems or it may be processed by the system or it may be deleted instantly after giving a meaningful representation

#### **Data Communication:-**2.

- Embedded Data communication systems are deployed in applications ranging from complex satellite communication systems to simple home networking systems

- Embedded Data communication systems are dedicated for data communication

- The data communication can happen through a wired interface (like Ethernet, RS-232C/USB/IEEE1394 etc) or wireless interface (like Wi-Fi, GSM,/GPRS, Bluetooth, ZigBee etc)

- Network hubs, Routers, switches, Modems etc are typical examples for dedicated data transmission embedded systems

#### 3. Data (Signal) Processing:-

- Embedded systems with Signal processing functionalities are employed in applications demanding signal processing like Speech coding, synthesis, audio video codec, transmission applications etc

- Computational intensive systems

- Employs Digital Signal Processors (DSPs)

#### 4. Monitoring:-

- Embedded systems coming under this category are specifically designed for monitoring purpose

- They are used for determining the state of some variables using input sensors

- They cannot impose control over variables.

- Electro Cardiogram (ECG) machine for monitoring the heart beat of a patient is a typical example for this

- The sensors used in ECG are the different Electrodes connected to the patient's body

- Measuring instruments like Digital CRO, Digital Multi meter, Logic Analyzer etc used in Control & Instrumentation applications are also examples of embedded systems for monitoring purpose

#### 5. <u>Control:-</u>

- Embedded systems with control functionalities are used for imposing control over some variables according to the changes in input variables

- Embedded system with control functionality contains both sensors and actuators

- Sensors are connected to the input port for capturing the changes in environmental variable or measuring variable

- The actuators connected to the output port are controlled according to the changes in input variable to put an impact on the controlling variable to bring the controlled variable to the specified range

Air conditioner for controlling room temperature is a typical example for embedded system with "Control" functionality

Air conditioner contains a room temperature sensing element (sensor) which may be a thermistor and a handheld unit for setting up (feeding) the desired temperature

The air compressor unit acts as the actuator. The compressor is controlled according to the current room temperature and the desired temperature set by the end user.

#### 6. Application Specific User Interface:-

- Embedded systems which are designed for a specific

- application

Contains Application Specific User interface (rather than general standard UI) like key board, Display units etc

Aimed at a specific target group of users

Mobile handsets, Control units in industrial applications etc are examples

#### EMBEDDED SYSTEM DESIGN PROCESS:

This section provides an overview of the embedded system design process aimed at two objectives. First, it will give us an introduction to the various steps in embedded system design before we delve into them in more detail. Second, it will allow us to consider the design methodology itself. A design methodology is important for three reasons. First, it allows us to keep a scorecard on a design to ensure that we have done everything we need to do, such as optimizing performance or performing functional tests. Second, it allows us to develop computer-aided design tools. Developing a single program that takes in a concept for an embedded system and emits a completed design would be a daunting task, but by first breaking the process into manageable steps, we can work on automating (or at least semi automating) the steps one at a time. Third, a design methodology makes it much easier for members of a design team to communicate.

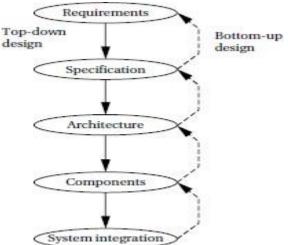

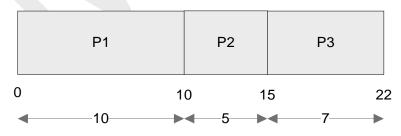

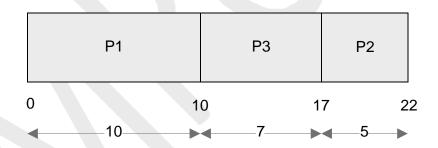

The below Figure summarizes the major steps in the embedded system design process. In this top-down view, we start with the system requirements.

Fig: Major levels of abstraction in the design process

#### **Requirements:**

Clearly, before we design a system, we must know what we are designing. The initial stages of the design process capture this information for use in creating the architecture and components. We generally proceed in two phases: First, we gather an informal description from the customers known as requirements, and we refine the requirements into a specification that contains enough information to begin designing the system architecture.

Requirements may be *functional* or *nonfunctional*. We must of course capture the basic functions of the embedded system, but functional description is often not sufficient. Typical nonfunctional requirements include:

• *Performance:* The speed of the system is often a major consideration both for the usability of the system and for its ultimate cost. As we have noted, performance may be a combination of soft performance metrics such as approximate time to perform a user-level function and hard deadlines by which a particular operation must be completed.

• *Cost:* The target cost or purchase price for the system is almost always a consideration. Cost typically has two major components: *manufacturing cost* includes the cost of components and assembly; *nonrecurring engineering* (NRE) costs include the personnel and other costs of designing the system.

■ *Physical size and weight:* The physical aspects of the final system can vary greatly depending upon the application. An industrial control system for an assembly line may be designed to fit into a standard-size rack with no strict limitations on weight. A handheld device typically has tight requirements on both size and weight that can ripple through the entire system design.

■ *Power consumption:* Power, of course, is important in battery-powered systems and is often important in other applications as well. Power can be specified in the requirements stage in terms of battery life—the customer is unlikely to be able to describe the allowable wattage.

A sample *requirements form* that can be filled out at the start of the project. We can use the form as a checklist in considering the basic characteristics of the system. Let's consider the entries in the form:

■ *Name:* This is simple but helpful. Giving a name to the project not only simplifies talking about it to other people but can also crystallize the purpose of the machine.

■ *Purpose:* This should be a brief one- or two-line description of what the system is supposed to do. If you can't describe the essence of your system in one or two lines, chances are that you don't understand it well enough.

■ *Inputs and outputs:* These two entries are more complex than they seem. The inputs and outputs to the system encompass a wealth of detail:

— *Types of data:* Analog electronic signals? Digital data? Mechanical inputs?

- Data characteristics: Periodically arriving data, such as digital audio

samples? Occasional user inputs? How many bits per data element?

— *Types of I/O devices:* Buttons? Analog/digital converters? Video displays?

• *Functions:* This is a more detailed description of what the system does. A good way to approach this is to work from the inputs to the outputs: When the system receives an input, what does it do? How do user interface inputs affect these functions? How do different functions interact?

*Performance:* Many embedded computing systems spend at least some time controlling physical devices or processing data coming from the physical world. In most of these cases, the computations must be performed within a certain time frame. It is essential that the performance requirements be identified early

since they must be carefully measured during implementation to ensure that the system works properly.

■ *Manufacturing cost:* This includes primarily the cost of the hardware components. Even if you don't know exactly how much you can afford to spend on system components, you should have some idea of the eventual cost range. Cost has a substantial influence on architecture: A machine that is meant to

sell at \$10 most likely has a very different internal structure than a \$100 system.

■ *Power:* Similarly, you may have only a rough idea of how much power the system can consume, but a little information can go a long way. Typically, the most important decision is

whether the machine will be battery powered or plugged into the wall. Battery-powered machines must be much more careful about how they spend energy.

■ *Physical size and weight:* You should give some indication of the physical size of the system to help guide certain architectural decisions. A desktop machine has much more flexibility in the components used than, for example, a lapel mounted voice recorder.

#### GPS MODULE:

#### **REQUIREMENTS FORM OF GPS MOVING MAP MODULE:**

Name : GPS moving map Purpose: Consumer-grade moving map for driving use Inputs : Power button, two control buttons Outputs : Back-lit LCD display 400 \_ 600 Functions : Uses 5-receiver GPS system; three user-selectable resolutions; always displays current latitude and longitude Performance: Updates screen within 0.25 seconds upon movement Manufacturing cost:\$30 Power: 100mW Physical size and weight: No more than 2" \_ 6, " 12 ounces

#### **Specification**

The specification is more precise—it serves as the contract between the customer and the architects. As such, the specification must be carefully written so that it accurately reflects the customer's requirements and does so in a way that can be clearly followed during design. The specification should be understandable enough so that someone can verify that it meets system requirements and overall expectations of the customer.

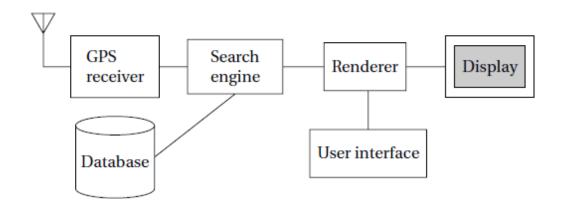

A specification of the GPS system would include several components:

- Data received from the GPS satellite constellation.

- Map data.

- User interface.

- Operations that must be performed to satisfy customer requests.

- Background actions required to keep the system running, such as operating the GPS receiver.

#### **Architecture Design**

The specification does not say how the system does things, only what the system does. Describing how the system implements those functions is the purpose of the architecture. The architecture is a plan for the overall structure of the system that will be used later to design the components that make up the architecture. The creation of the architecture is the first phase of what many designers think of as design.

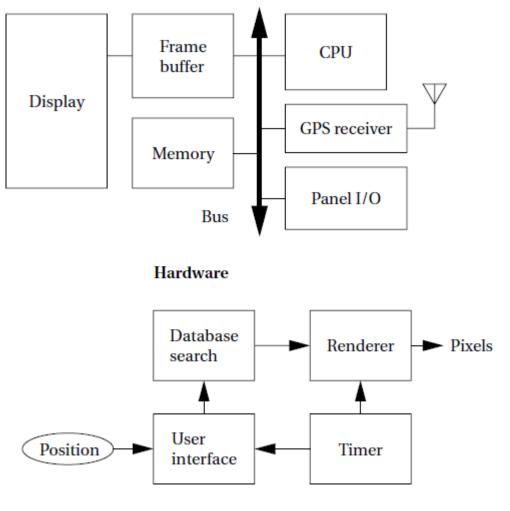

This block diagram is still quite abstract—we have not yet specified which operations will be performed by software running on a CPU, what will be done by special-purpose hardware, and so on. The diagram does, however, go a long way toward describing how to implement the functions described in the specification. We clearly see, for example, that we need to search the topographic database and to render (i.e., draw) the results for the display. We have chosen to separate those functions so that we can potentially do them in parallel—performing rendering separately from searching the database may help us update the screen more fluidly.

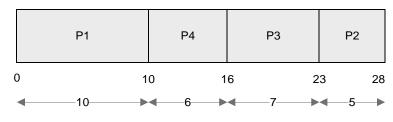

#### FIG: BLOCK DIAGRAM FOR THE MOVING MAP

The hardware block diagram clearly shows that we have one central CPU surrounded by memory and I/O devices. In particular, we have chosen to use two memories: a frame buffer for the pixels to be displayed and a separate program/data memory for general use by the CPU. The software block diagram fairly closely follows the system block diagram, but we have added a timer to control when we read the buttons on the user interface and render data onto the screen. To have a truly complete architectural description, we require more detail, such as where units in the software block diagram will be executed in the hardware block diagram and when operations will be performed in time.

Fig : Hardware and software architectures for the moving map.

The architectural description tells us what components we need. The component design effort builds those components in conformance to the architecture and specification. The components will in general include both hardware—FPGAs, boards, and so on—and software modules. Some of the components will be ready-made. The CPU, for example, will be a standard component in almost all cases, as will memory chips and many other components .In the moving map, the GPS receiver is a good example of a specialized component that will nonetheless be a predesigned, standard component. We can also make use of standard software modules.

#### System Integration:

Only after the components are built do we have the satisfaction of putting them together and seeing a working system. Of course, this phase usually consists of a lot more than just plugging everything together and standing back. Bugs are typically found during system integration, and good planning can help us find the bugs quickly. By building up the system in phases and running properly chosen tests, we can often find bugs more easily. If we debug only a few modules at a time, we are more likely to uncover the simple bugs and able to easily recognize them. Only by fixing the simple bugs early will we be able to uncover the more complex or obscure bugs that can be identified only by giving the system a hard workout

#### **Characteristics of Embedded systems:**

#### (DEC2016, March-2017)

Embedded systems possess certain specific characteristics and these are unique to each Embedded system.

- 1. Application and domain specific

- 2. Reactive and Real Time

- 3. Operates in harsh environments

- 4. Distributed

- 5. Small Size and weight

- 6. Power concerns

- 7. Single-functioned

- 8. Complex functionality

- 9. Tightly-constrained

- 10. Safety-critical

#### 1. Application and Domain Specific:-

- Each E.S has certain functions to perform and they are developed in such a manner to do the intended functions only.

- They cannot be used for any other purpose.

- Ex The embedded control units of the microwave oven cannot be replaced with AC"S embedded control unit because the embedded control units of microwave oven and AC are specifically designed to perform certain specific tasks.

#### T,VINAYSIMHA REDDY, Dept. of ECE, MRCET

#### 2. Reactive and Real Time:-

- E.S are in constant interaction with the real world through sensors and user-defined input devices which are connected to the input port of the system.

- Any changes in the real world are captured by the sensors or input devices in real time and the control algorithm running inside the unit reacts in a designed manner to bring the controlled output variables to the desired level.

- E.S produce changes in output in response to the changes in the input, so they are referred as reactive systems.

- Real Time system operation means the timing behavior of the system should be deterministic ie the system should respond to requests in a known amount of time.

- Example E.S which are mission critical like flight control systems, Antilock Brake Systems (ABS) etc are Real Time systems.

#### 3. Operates in Harsh Environment :-

- The design of E.S should take care of the operating conditions of the area where the system is going to implement.

- Ex If the system needs to be deployed in a high temperature zone, then all the components used in the system should be of high temperature grade.

- Also proper shock absorption techniques should be provided to systems which are going to be commissioned in places subject to high shock.

#### 4. Distributed: -

- It means that embedded systems may be a part of a larger system.

- Many numbers of such distributed embedded systems form a single large embedded control unit.

- Ex Automatic vending machine. It contains a card reader, a vending unit etc. Each of them are independent embedded units but they work together to perform the overall vending function.

#### 5. Small Size and Weight:-

- Product aesthetics (size, weight, shape, style, etc) is an important factor in choosing a product.

- It is convenient to handle a compact device than a bulky product.

#### 6. Power Concerns:-

- Power management is another important factor that needs to be considered in designing embedded systems.

- E.S should be designed in such a way as to minimize the heat dissipation by the system.

- 7. Single-functioned:- Dedicated to perform a single function

- **8.** Complex functionality: We have to run sophisticated algorithms or multiple algorithms in some applications.

- 9. Tightly-constrained:-

- Low cost, low power, small, fast, etc

#### 10. Safety-critical:-

• Must not endanger human life and the environment

<u>Ouality Attributes of Embedded System:</u> Quality attributes are the non-functional requirements that need to be documented properly in any system design.(DEC16,March-2017)

Quality attributes can be classified as

- I. Operational quality attributes

- **II. Non-operational quality attributes.**

**I. Operational Quality Attributes:** The operational quality attributes represent the relevant quality attributes related to the embedded system when it is in the operational mode or online mode.

#### **Operational Quality Attributes are:**

#### 1. Response :-

• It is the measure of quickness of the system.

It tells how fast the system is tracking the changes in input variables.

Most of the E.S demands fast response which should be almost real time.

**Ex** – Flight control application.

#### 2. Throughput :-

It deals with the efficiency of a system.

It can be defined as the rate of production or operation of a defined process over a stated period of time.

The rates can be expressed in terms of products, batches produced or any other meaningful measurements.

- Ex In case of card reader throughput means how many transactions the reader can perform in a minute or in an hour or in a day.

- Throughput is generally measured in terms of "Benchmark".

- A Benchmark is a reference point by which something can be measured

#### 3. Reliability :-

- It is a measure of how much we can rely upon the proper functioning of the system.

- Mean Time Between Failure (MTBF) and Mean Time To Repair (MTTR) are the terms used in determining system reliability.

- MTBF gives the frequency of failures in hours/weeks/months.

- MTTR specifies how long the system is allowed to be out of order following a failure.

- For embedded system with critical application need, it should be of the order of minutes.

#### 4. Maintainability:-

- It deals with support and maintenance to the end user or client in case of technical issues and product failure or on the basis of a routine system checkup.

- Reliability and maintainability are complementary to each other.

- A more reliable system means a system with less corrective maintainability requirements and vice versa.

- Maintainability can be broadly classified into two categories

- 1. Scheduled or Periodic maintenance (Preventive maintenance)

- 2. Corrective maintenance to unexpected failures

#### 5. Security:-

- Confidentiality, Integrity and availability are the three major measures of information security.

- Confidentiality deals with protection of data and application from unauthorized disclosure.

- Integrity deals with the protection of data and application from unauthorized modification.

- Availability deals with protection of data and application from unauthorized users.

#### 6. Safety :-

- Safety deals with the possible damages that can happen to the operator, public and the environment due to the breakdown of an Embedded System.

- The breakdown of an embedded system may occur due to a hardware failure or a firmware failure.

- Safety analysis is a must in product engineering to evaluate the anticipated damages and determine the best course of action to bring down the consequences of damage to an acceptable level.

**II.** Non-Operational Quality Attributes: The quality attributes that needs to be addressed for the product not on the basis of operational aspects are grouped under this category.

#### 1. Testability and Debug-ability:-

- Testability deals with how easily one can test the design, application and by which means it can be done.

- For an E.S testability is applicable to both the embedded hardware and firmware.

- Embedded hardware testing ensures that the peripherals and total hardware functions in the desired manner, whereas firmware testing ensures that the firmware is functioning in the expected way.

- Debug-ability is a means of debugging the product from unexpected behavior in the system

- Debug-ability is two level process

- 1.Hardware level 2.software level

- **1. Hardware level:** It is used for finding the issues created by hardware problems.

- 2. Software level: It is employed for finding the errors created by the flaws in the software.

#### 2. Evolvability :-

- It is a term which is closely related to Biology.

- It is referred as the non-heritable variation.

- For an embedded system evolvability refers to the ease with which the embedded product can be modified to take advantage of new firmware or hardware technologies.

#### 3. Portability:-

- It is the measure of system independence.

- An embedded product is said to be portable if the product is capable of functioning in various environments, target processors and embedded operating systems.

- "Porting" represents the migration of embedded firmware written for one target processor to a different target processor.

#### 4. Time-to-Prototype and Market:-

- It is the time elapsed between the conceptualization of a product and the time at which the product is ready for selling.

- The commercial embedded product market is highly competitive and time to market the product is critical factor in the success of commercial embedded product.

- There may be multiple players in embedded industry who develop products of the same category (like mobile phone).

#### 5. Per Unit Cost and Revenue:-

- Cost is a factor which is closely monitored by both end user and product manufacturer.

- Cost is highly sensitive factor for commercial products

- Any failure to position the cost of a commercial product at a nominal rate may lead to the failure of the product in the market.

- Proper market study and cost benefit analysis should be carried out before taking a decision on the per-unit cost of the embedded product.

- The ultimate aim of the product is to generate marginal profit so the budget and total cost should be properly balanced to provide a marginal profit.

#### **SUMMARY**

- 1. An embedded system is an electronic/electromechanical system designed to perform a specific function and is a combination of both hardware and firmware (software).

- 2. A general purpose computing system is a combination of generic hardware and general purpose operating system for executing a variety of applications, whereas an embedded

- 3. System is a combination of special purpose hardware and embedded OS/firmware for executing a specific set of applications.

- 4. Apollo Guidance Computer (AGC) is the first recognized modern embedded system and Autonetics D-17, the guidance computer for the Minuteman-I missile, was the first mass produced embedded system.

- 5. Based on the complexity and performance requirements, embedded systems are classified into small-scale, medium-scale and large-scale/complex.

- 6. The presences of embedded system vary from simple electronic system toys to complex flight and missile control systems.

- 7. Embedded systems are designed to serve the purpose of any one or combination of data collection/storage/representation, data processing, monitoring, control or application specific user interface.

- 8. Wearable devices refer to embedded systems which are incorporated into accessories and apparels. It envisions the bonding of embedded technology in our day to day lives.

#### **OBJECTIVE OUESTIONS**

- 1. Embedded systems are

- (a) General Purpose (b) Special Purpose

- 2. Embedded system is

- (a) An electronic system (b) A pure mechanical system

- (c)An electro-mechanical system (d) (a) or (c)

- 3. Which of the following is not true about embedded systems?

(a)Built around specialized hardware (b) Always contain an operating system

(c)Execution behavior may be deterministic (d) All of these (e) none of these

- 4. Which of the following is not an example of small scale embedded system?

- (a) Electronic Barbie doll (b) Simple calculator

- (c) Cell Phone (d) Electronic toy car

| 5. The first recognized modern embedded system is                                     |                                                   |  |

|---------------------------------------------------------------------------------------|---------------------------------------------------|--|

| (a) Apple computer                                                                    | (b) Apollo Guidance Computer                      |  |

| (c) Calculator                                                                        | (d) Radio navigation system                       |  |

| 6. The first mass produced embedded system is                                         |                                                   |  |

| (a) Minuteman-I                                                                       | Minuteman-I (b) Minuteman-II                      |  |

| (c) Autonetics D17                                                                    | (d) Apollo Guidance Computer                      |  |

| 7. Which of the following is (are) an intended purpose of embedded systems?           |                                                   |  |

| (a) Data collection                                                                   | (a) Data collection (b) Data processing           |  |

| (c) Data communication                                                                | (d) All of these (e) None of these                |  |

| 8. Which of the following is an example of an embedded system for data communication? |                                                   |  |

| (a) USB mass storage device (b) Network router (c) Digital camera                     |                                                   |  |

| (d)Music player                                                                       | (e) All of these (f) None of these                |  |

| 9. A digital multimeter is an example of embedded system for                          |                                                   |  |

| (a) Data communication                                                                | (b) Monitoring (c) Control                        |  |

| (d) All of these                                                                      | (e) None of these                                 |  |

| 10. Which of the following is an example of an embedded system for signal processing? |                                                   |  |

| (a) Apple iPOD                                                                        | a) Apple iPOD (b) Sandisk USB mass storage device |  |

| (c) both a and b                                                                      | (d) None of these                                 |  |

### **Reference Text Books:-**

#### 1. Introduction to Embedded Systems – Shibu K.V Mc Graw Hill

#### 2. Computers as Components –Wayne Wolf-morgan Kaufmann publications

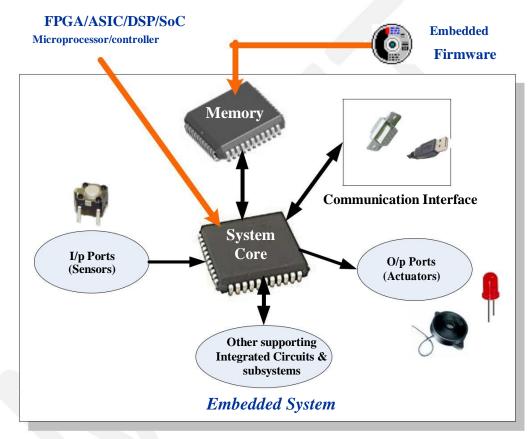

#### **ELEMENTS OF EMBEDDED SYSTEMS:**

An embedded system is a combination of 3 things, Hardware Software Mechanical Components and it is supposed to do one specific task only. A typical embedded system contains a single chip controller which acts as the master brain of the system. Diagrammatically an embedded system can be represented as follows:

#### **Real World**

Embedded systems are basically designed to regulate a physical variable (such Microwave Oven) or to manipulate the state of some devices by sending some signals to the actuators or devices connected to the output port system (such as temperature in Air Conditioner), in response to the input signal provided by the end users or sensors which are connected to the input ports. Hence the embedded systems can be viewed as a reactive system.

The control is achieved by processing the information coming from the sensors and user interfaces and controlling some actuators that regulate the physical variable.

Keyboards, push button, switches, etc. are Examples of common user interface input devices and LEDs, LCDs, Piezoelectric buzzers, etc examples for common user interface output devices for a typical embedded system. The requirement of type of user interface changes from application to application based on domain.

Some embedded systems do not require any manual intervention for their operation. They automatically sense the input parameters from real world through sensors which are connected at input port. The sensor information is passed to the processor after signal conditioning and digitization. The core of the system performs some predefined operations on input data with the help of embedded firmware in the system and sends some actuating signals to the actuator connect connected to the output port of the system.

The memory of the system is responsible for holding the code (control algorithm and other important configuration details). There are two types of memories are used in any embedded system. Fixed memory (ROM) is used for storing code or program. The user cannot change the firmware in this type of memory. The most common types of memories used in embedded systems for control algorithm storage are OTP,PROM,UVEPROM,EEPROM and FLASH

An embedded system without code (i.e. the control algorithm) implemented memory has all the peripherals but is not capable of making decisions depending on the situational as well as real world changes.

Memory for implementing the code may be present on the processor or may be implemented as a separate chip interfacing the processor

In a controller based embedded system, the controller may contain internal memory for storing code such controllers are called Micro-controllers with on-chip ROM, eg. Atmel AT89C51. **The Core of the Embedded Systems:** The core of the embedded system falls into any one of the following categories.

### General Purpose and Domain Specific Processors

- Microprocessors

- Microcontrollers

- Digital Signal Processors

### Programmable Logic Devices (PLDs)

- Application Specific Integrated Circuits (ASICs)

- Commercial off the shelf Components (COTS)

#### GENERAL PURPOSE AND DOMAIN SPECIFIC PROCESSOR:

- Almost 80% of the embedded systems are processor/ controller based.

- The processor may be microprocessor or a microcontroller or digital signal processor, depending on the domain and application.

#### Microprocessor:

- A silicon chip representing a Central Processing Unit (CPU), which is capable of performing arithmetic as well as logical operations according to a pre-defined set of Instructions, which is specific to the manufacturer

- In general the CPU contains the Arithmetic and Logic Unit (ALU), Control Unit and Working registers

- Microprocessor is a dependant unit and it requires the combination of other hardware like Memory, Timer Unit, and Interrupt Controller etc for proper functioning.

- Intel claims the credit for developing the first Microprocessor unit Intel 4004, a 4 bit processor which was released in Nov 1971

- Developers of microprocessors.

- Intel Intel 4004 November 1971(4-bit)

- Intel Intel 4040.

- Intel Intel 8008 April 1972.

- Intel Intel 8080 April 1974(8-bit).

- Motorola Motorola 6800.

- Intel Intel 8085 1976.

- Zilog Z80 July 1976

#### **Microcontroller:**

\*

\*

\*

A highly integrated silicon chip containing a CPU, scratch pad RAM, Special and General purpose Register Arrays, On Chip ROM/FLASH memory for program storage, Timer and Interrupt control units and dedicated I/O ports

Microcontrollers can be considered as a super set of Microprocessors

Microcontroller can be general purpose (like Intel 8051, designed for generic applications and domains) or application specific (Like Automotive AVR from Atmel Corporation. Designed specifically for automotive applications)

Since a microcontroller contains all the necessary functional blocks for independent working, they found greater place in the embedded domain in place of microprocessors

Microcontrollers are cheap, cost effective and are readily available in the market

\* Texas Instruments TMS 1000 is considered as the world"s first microcontroller

#### **Microprocessor Vs Microcontroller:**

| Microprocessor                                                                                                                                                                               | Microcontroller                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A silicon chip representing a Central Processing Unit<br>(CPU), which is capable of performing arithmetic as<br>well as logical operations according to a pre-defined set<br>of Instructions | A microcontroller is a highly integrated chip that<br>contains a CPU, scratch pad RAM, Special and<br>General purpose Register Arrays, On Chip<br>ROM/FLASH memory for program storage, Timer<br>and Interrupt control units and dedicated I/O ports |

| It is a dependent unit. It requires the combination of<br>other chips like Timers, Program and data memory<br>chips, Interrupt controllers etc for functioning                               | It is a self contained unit and it doesn't require<br>external Interrupt Controller, Timer, UART etc for<br>its functioning                                                                                                                          |

| Most of the time general purpose in design and operation                                                                                                                                     | Mostly application oriented or domain specific                                                                                                                                                                                                       |

| Doesn't contain a built in I/O port. The I/O Port<br>functionality needs to be implemented with the help of<br>external Programmable Peripheral Interface Chips like<br>8255                 | Most of the processors contain multiple built-in I/O<br>ports which can be operated as a single 8 or 16 or 32<br>bit Port or as individual port pins                                                                                                 |

| Targeted for high end market where performance is important                                                                                                                                  | Targeted for embedded market where performance is<br>not so critical (At present this demarcation is invalid)                                                                                                                                        |

| Limited power saving options compared to microcontrollers                                                                                                                                    | Includes lot of power saving features                                                                                                                                                                                                                |

#### General Purpose Processor (GPP) Vs Application Specific Instruction Set Processor (ASIP)

General Purpose Processor or GPP is a processor designed for general computational tasks

\*

\*

GPPs are produced in large volumes and targeting the general market. Due to the high volume production, the per unit cost for a chip is low compared to ASIC or other specific ICs

#### \*

A typical general purpose processor contains an Arithmetic and Logic Unit (ALU) and Control Unit (CU)

#### \*

Application Specific Instruction Set processors (ASIPs) are processors with architecture and instruction set optimized to specific domain/application requirements like Network processing, Automotive, Telecom, media applications, digital signal processing, control applications etc.

#### \*

ASIPs fill the architectural spectrum between General Purpose Processors and Application Specific Integrated Circuits (ASICs)

\*

The need for an ASIP arises when the traditional general purpose processor are unable to meet the increasing application needs

#### \*

Some Microcontrollers (like Automotive AVR, USB AVR from Atmel), System on Chips, Digital Signal Processors etc are examples of Application Specific Instruction Set Processors (ASIPs)

#### \*

ASIPs incorporate a processor and on-chip peripherals, demanded by the application requirement, program and data memory

#### **Digital Signal Processors (DSPs):**

- Powerful special purpose 8/16/32 bit microprocessors designed specifically to meet the computational demands and power constraints of today's embedded audio, video, and communications applications

- Digital Signal Processors are 2 to 3 times faster than the general purpose microprocessors in signal processing applications

- DSPs implement algorithms in hardware which speeds up the execution whereas general purpose processors implement the algorithm in firmware and the speed of execution depends primarily on the clock for the processors

- DSP can be viewed as a microchip designed for performing high speed computational operations for "addition", "subtraction", "multiplication" and "division"

- A typical Digital Signal Processor incorporates the following key units

- Program Memory

- Data Memory

- ✤ Computational Engine

- ✤ I/O Unit

- Audio video signal processing, telecommunication and multimedia applications are typical examples where DSP is employed

#### **RISC V/s CISC Processors/Controllers:**

| RISC                                                                                                              | CISC                                                                                                                                                                        |  |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Lesser no. of instructions                                                                                        | Greater no. of Instructions                                                                                                                                                 |  |

| Instruction Pipelining and increased execution speed                                                              | Generally no instruction pipelining feature                                                                                                                                 |  |

| Orthogonal Instruction Set (Allows each instruction<br>to operate on any register and use any addressing<br>mode) | Non Orthogonal Instruction Set (All instructions<br>are not allowed to operate on any register and<br>use any addressing mode. It is instruction<br>specific)               |  |

| Operations are performed on registers only, the only memory operations are load and store                         | Operations are performed on registers or<br>memory depending on the instruction                                                                                             |  |

| Large number of registers are available                                                                           | Limited no. of general purpose registers                                                                                                                                    |  |

| Programmer needs to write more code to execute a task since the instructions are simpler ones                     | . A programmer can achieve the desired<br>functionality with a single instruction which in<br>turn provides the effect of using more simpler<br>single instructions in RISC |  |

| Single, Fixed length Instructions                                                                                 | Variable length Instructions                                                                                                                                                |  |

| Less Silicon usage and pin count                                                                                  | More silicon usage since more additional decoder logic is required to implement the complex instruction decoding.                                                           |  |

| With Harvard Architecture                                                                                         | Can be Harvard or Von-Neumann Architecture                                                                                                                                  |  |

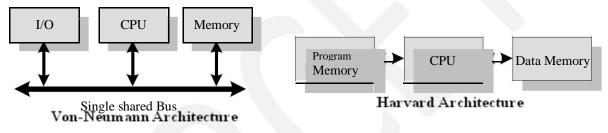

#### Harvard V/s Von-Neumann Processor/Controller Architecture

- The terms Harvard and Von-Neumann refers to the processor architecture design.

- Microprocessors/controllers based on the common bus for fetching both instructions stored in a common main memory

Von-Neumann architecture shares a single and data. Program instructions and data are

- Microprocessors/controllers based on the **Harvard** architecture will have separate data bus and instruction bus. This allows the data transfer and program fetching to occur simultaneously on both buses

- With Harvard architecture, the data memory can be read and written while the program memory is being accessed. These separated data memory and code memory buses allow one instruction to execute while the next instruction is fetched ("Pre-fetching")

#### Harvard V/s Von-Neumann Processor/Controller Architecture:

| Harvard Architecture                                                                                                                               | Von-Neumann Architecture                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Separate buses for Instruction and Data fetching                                                                                                   | Single shared bus for Instruction and Data fetching                                                                                   |  |

| Easier to Pipeline, so high performance can be achieved                                                                                            | Low performance Compared to Harvard<br>Architecture                                                                                   |  |

| Comparatively high cost                                                                                                                            | Cheaper                                                                                                                               |  |

| No memory alignment problems                                                                                                                       | Allows self modifying codes <sup>†</sup>                                                                                              |  |

| Since data memory and program memory are<br>stored physically in different locations, no<br>chances for accidental corruption of program<br>memory | Since data memory and program memory<br>are stored physically in same chip, chances<br>for accidental corruption of program<br>memory |  |

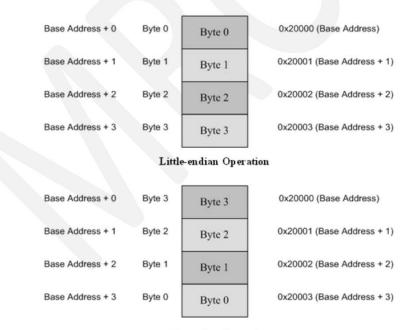

#### **Big-endian V/s Little-endian processors:**

Endianness specifies the order in which the data is stored in the memory by processor operations in a multi byte system (Processors whose word size is greater than one byte). Suppose the word length is two byte then data can be stored in memory in two different ways

- Higher order of data byte at the higher memory and lower order of data byte at location just below the higher memory

- Lower order of data byte at the higher memory and higher order of data byte at location just below the higher memory

*Little-endian* means the lower-order byte of the data is stored in memory at the lowest address, and the higher-order byte at the highest address. (The little end comes first)

*Big-endian* means the higher-order byte of the data is stored in memory at the lowest address, and the lower-order byte at the highest address. (The big end comes first.)

#### **Big-endian V/s Little-endian processors**

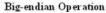

#### Load Store Operation & Instruction Pipelining:

The RISC processor instruction set is orthogonal and it operates on registers. The memory access related operations are performed by the special instructions *load* and *store*. If the operand is specified as memory location, the content of it is loaded to a register using the *load* instruction. The instruction *store* stores data from a specified register to a specified memory location

Load Store Operation

- The conventional instruction execution by the processor follows the fetch-decodeexecute sequence

- The "fetch" part fetches the instruction from program memory or code memory and the decode part decodes the instruction to generate the necessary control signals

|                      | Clock Pulses     | Clock Pulses    | Clock Pulses    |

|----------------------|------------------|-----------------|-----------------|

|                      |                  |                 |                 |

|                      | Machine Cycle 1  | Machine Cycle 2 | Machine Cycle 3 |

|                      | Fetch (PC)       |                 |                 |

|                      | Execute (PC - 1) | Fetch (PC+1)    |                 |

|                      |                  | Execute (PC)    | Fetch (PC+2)    |

| PC : Program Counter |                  | Execute (PC+1)  |                 |

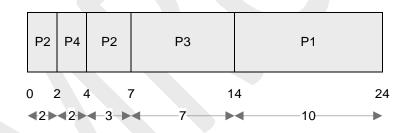

#### The Single stage pipelining concept

• The execute stage reads the operands, perform ALU operations and stores the result. In conventional program execution, the fetch and decode operations are performed in sequence

- During the decode operation the memory address bus is available and if it possible to effectively utilize it for an instruction fetch, the processing speed can be increased

- In its simplest form instruction pipelining refers to the overlapped execution of instructions

## **Application Specific Integrated Circuit (ASIC):**

- A microchip designed to perform a specific or unique application. It is used as replacement to conventional general purpose logic chips.

- ASIC integrates several functions into a single chip and thereby reduces the system development cost

- Most of the ASICs are proprietary products. As a single chip, ASIC consumes very small area in the total system and thereby helps in the design of smaller systems with high capabilities/functionalities.

- ASICs can be pre-fabricated for a special application or it can be custom fabricated by using the components from a re-usable *"building block*" library of components for a particular customer application

- Fabrication of ASICs requires a non-refundable initial investment (Non Recurring Engineering (NRE) charges) for the process technology and configuration expenses

- If the Non-Recurring Engineering Charges (NRE) is born by a third party and the Application Specific Integrated Circuit (ASIC) is made openly available in the market, the ASIC is referred as Application Specific Standard Product (ASSP)

- The ASSP is marketed to multiple customers just as a general-purpose product, but to a smaller number of customers since it is for a specific application.

• Some ASICs are proprietary products, the developers are not interested in revealing the internal details.

## **Programmable Logic Devices (PLDs):**

#### \*

Logic devices provide specific functions, including device-to-device interfacing, data communication, signal processing, data display, timing and control operations, and almost every other function a system must perform.

#### \*

Logic devices can be classified into two broad categories - Fixed and Programmable. The circuits in a fixed logic device are permanent, they perform one function or set of functions - once manufactured, they cannot be changed

#### \*

Programmable logic devices (PLDs) offer customers a wide range of logic capacity, features, speed, and voltage characteristics - and these devices can be re-configured to perform any number of functions at any time

#### \*

Designers can use inexpensive software tools to quickly develop, simulate, and test their logic designs in PLD based design. The design can be quickly programmed into a device, and immediately tested in a live circuit

\*\*

PLDs are based on re-writable memory technology and the device is reprogrammed to change the design

#### **Programmable Logic Devices (PLDs) – CPLDs and FPGA**

• Field Programmable Gate Arrays (FPGAs) and Complex Programmable Logic Devices (CPLDs) are the two major types of programmable logic devices

## **FPGA:**

- FPGA is an IC designed to be configured by a designer after manufacturing.

- FPGAs offer the highest amount of logic density, the most features, and the highest performance.

- Logic gate is Medium to high density ranging from **1K to 500K** system gates

• These advanced FPGA devices also offer features such as built-in hardwired processors (such as the IBM Power PC), substantial amounts of memory, clock management systems, and support for many of the latest, very fast device-to-device signaling technologies

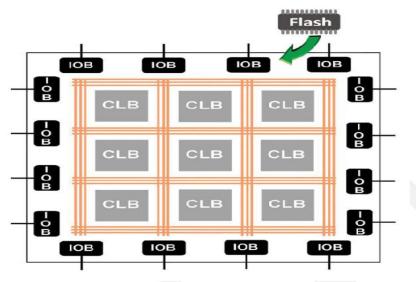

Figure: FPGA Architecture

- These advanced FPGA devices also offer features such as built-in hardwired processors, substantial amounts of memory, clock management systems, and support for many of the latest, very fast device-to-device signaling technologies.

- FPGAs are used in a wide variety of applications ranging from data processing and storage, to instrumentation, telecommunications, and digital signal processing

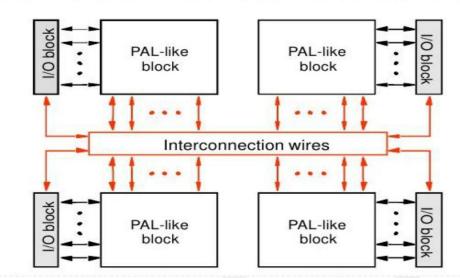

## **CPLD:**

- A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both.

- CPLDs, by contrast, offer much smaller amounts of logic up to about 10,000 gates.

- CPLDs offer very predictable timing characteristics and are therefore ideal for critical control applications.

## Structure of a C PLD

• CPLDs such as the Xilinx **CoolRunner** series also require extremely low amounts of power and are very inexpensive, making them ideal for cost-sensitive, battery-operated, portable applications such as mobile phones and digital handheld assistants.

#### **ADVANTAGES OF PLDs:**

- PLDs offer customer much more flexibility during design cycle

- PLDSs do not require long lead times for prototype or production-the PLDs are already on a distributor"s self and ready for shipment

- PLDs do not require customers to pay for large NRE costs and purchase expensive mask sets

- PLDs allow customers to order just the number of parts required when they need them. allowing them to control inventory.

- PLDs are reprogrammable even after a piece of equipment is shipped to a customer.

- The manufacturers able to add new features or upgrade the PLD based products that are in the field by uploading new programming file

## **Commercial off the Shelf Component (COTS):**

- A Commercial off-the-shelf (COTS) product is one which is used "as-is"

- COTS products are designed in such a way to provide easy integration and interoperability with existing system components

• Typical examples for the COTS hardware unit are Remote Controlled Toy Car control unit including the RF Circuitry part, High performance, high frequency microwave electronics (2 to 200 GHz), High bandwidth analog-to-digital converters, Devices and components for operation at very high temperatures, Electro-optic IR imaging arrays, UV/IR Detectors etc

A COTS component in turn contains a General Purpose Processor (GPP) or Application Specific Instruction Set Processor (ASIP) or Application Specific Integrated Chip (ASIC)/Application Specific Standard Product (ASSP) or Programmable Logic Device (PLD)

- The major advantage of using COTS is that they are readily available in the market, cheap and a developer can cut down his/her development time to a great extend.

- There is no need to design the module yourself and write the firmware .

- Everything will be readily supplied by the COTs manufacturer.

- The major problem faced by the end-user is that there are no operational and manufacturing standards.

- The major drawback of using COTs component in embedded design is that the manufacturer may withdraw the product or discontinue the production of the COTs at any time if rapid change in technology

- This problem adversely affect a commercial manufacturer of the embedded system which makes use of the specific COTs

### Memory:

- Memory is an important part of an embedded system. The memory used in embedded system can be either Program Storage Memory (ROM) or Data memory (RAM)

- Certain Embedded processors/controllers contain built in program memory and data memory and this memory is known as on-chip memory

- Certain Embedded processors/controllers do not contain sufficient memory inside the chip and requires external memory called **off-chip memory or external memory**.

#### Memory – Program Storage Memory:

Stores the program instructions

#### •;•

Retains its contents even after the power to it is turned off. It is generally known as Non volatile storage memory

#### \*

Depending on the fabrication, erasing and programming techniques they are classified into

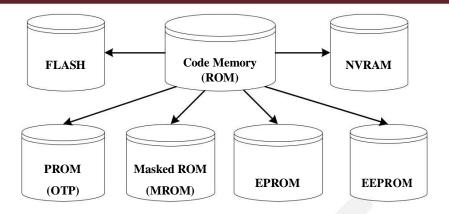

#### 1. Masked ROM (MROM):

- One-time programmable memory.

- Uses hardwired technology for storing data.

- The device is factory programmed by masking and metallization process according to the data provided by the end user.

- The primary advantage of MROM is low cost for high volume production.

- MROM is the least expensive type of solid state memory.

- Different mechanisms are used for the masking process of the ROM, like

Creation of an enhancement or depletion mode transistor through channel implant

- By creating the memory cell either using a standard transistor or a high threshold transistor.

- In the high threshold mode, the supply voltage required to turn ON the transistor is above the normal ROM IC operating voltage.

- This ensures that the transistor is always off and the memory cell stores always logic 0.

- The limitation with MROM based firmware storage is the inability to modify the device firmware against firmware upgrades.

- The MROM is permanent in bit storage, it is not possible to alter the bit information

#### 2. Programmable Read Only Memory (PROM) / (OTP) :

- It is not pre-programmed by the manufacturer

- The end user is responsible for Programming these devices.

- PROM/OTP has *nichrome* or *polysilicon* wires arranged in a matrix, these wires can be functionally viewed as fuses.

- It is programmed by a PROM programmer which selectively burns the fuses according to the bit pattern to be stored.

- Fuses which are not blown/burned represents a logic "1" where as fuses which are blown/burned represents a logic "0". The default state is logic "1".

- OTP is widely used for commercial production of embedded systems whose proto-typed versions are proven and the code is finalized.

- It is a low cost solution for commercial production.

- OTPs cannot be reprogrammed.

#### 3. Erasable Programmable Read Only Memory (EPROM):

- Erasable Programmable Read Only (EPROM) memory gives the flexibility to re-program the same chip.

- During development phase, code is subject to continuous changes and using an OTP is not economical.

- EPROM stores the bit information by charging the floating gate of an FET

- Bit information is stored by using an EPROM Programmer, which applies high voltage to charge the floating gate

- EPROM contains a quartz crystal window for erasing the stored information. If the window is exposed to Ultra violet rays for a fixed duration, the entire memory will be erased

- Even though the EPROM chip is flexible in terms of re-programmability, it needs to be taken out of the circuit board and needs to be put in a UV eraser device for 20 to 30 minutes

#### 4. Electrically Erasable Programmable Read Only Memory (EEPROM):

- Erasable Programmable Read Only (EPROM) memory gives the flexibility to re-program the same chip using electrical signals

- The information contained in the EEPROM memory can be altered by using electrical signals at the register/Byte level

- They can be erased and reprogrammed within the circuit

- These chips include a chip erase mode and in this mode they can be erased in a few milliseconds

- It provides greater flexibility for system design

- The only limitation is their capacity is limited when compared with the standard ROM (A few kilobytes).

#### 5. Program Storage Memory – FLASH

- FLASH memory is a variation of EEPROM technology.

- FALSH is the latest ROM technology and is the most popular ROM technology used in today"s embedded designs

- It combines the re-programmability of EEPROM and the high capacity of standard ROMs

- FLASH memory is organized as sectors (blocks) or pages

- FLASH memory stores information in an array of floating gate MOSFET transistors

- The erasing of memory can be done at sector level or page level without affecting the other sectors or pages

- Each sector/page should be erased before re-programming

- The typical erasable capacity of FLASH is of the order of a few 1000 cycles.

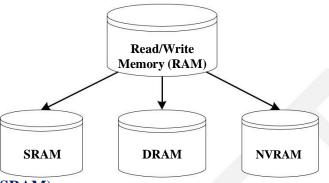

#### Read-Write Memory/Random Access Memory (RAM)

- RAM is the data memory or working memory of the controller/processor

- RAM is volatile, meaning when the power is turned off, all the contents are destroyed

#### \*

RAM is a direct access memory, meaning we can access the desired memory location directly without the need for traversing through the entire memory locations to reach the desired memory position (i.e. Random Access of memory location)

## 1. Static RAM (SRAM):

Static RAM stores data in the form of Voltage.

• They are made up of flip-flops

#### •;•

In typical implementation, an SRAM cell (bit) is realized using 6 transistors (or 6 MOSFETs).

#### \*

\*\*

Four of the transistors are used for building the latch (flip-flop) part of the memory cell and 2 for controlling the access.

Static RAM is the fastest form of RAM available.

SRAM is fast in operation due to its resistive networking and switching capabilities

#### 2. Dynamic RAM (DRAM)

#### \*

Dynamic RAM stores data in the form of charge. They are made up of MOS transistor gates

#### \*

The advantages of DRAM are its high density and low cost compared to SRAM

#### \*

The disadvantage is that since the information is stored as charge it gets leaked off with time and to prevent this they need to be refreshed periodically

DRAM cell implementation

Bit Line B

#### \*

Special circuits called DRAM controllers are used for the refreshing operation. The refresh operation is done periodically in milliseconds interval

SRAM cell implementation

#### SRAM Vs DRAM:

| SRAM Cell                                      | DRAM Cell                                                                                                                        |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Made up of 6 CMOS transistors (MOSFET)         | Made up of a MOSFET and a capacitor                                                                                              |

| Doesn"t Require refreshing                     | Requires refreshing                                                                                                              |

| Low capacity (Less dense)                      | High Capacity (Highly dense)                                                                                                     |

| More expensive                                 | Less Expensive                                                                                                                   |

| Fast in operation. Typical access time is 10ns | Slow in operation due to refresh<br>requirements. Typical access time is 60ns.<br>Write operation is faster than read operation. |

#### 3. Non Volatile RAM (NVRAM):

Random access memory with battery backup

\*

It contains Static RAM based memory and a minute battery for providing supply to the memory in the absence of external power supply

\*

\*

\*

The memory and battery are packed together in a single package

NVRAM is used for the non volatile storage of results of operations or for setting up of flags etc

The life span of NVRAM is expected to be around 10 years

★ DS1744 from Maxim/Dallas is an example for 32KB NVRAM

#### **Memory selection for Embedded Systems:**

- Selection of suitable memory is very much essential step in high performance applications, because the challenges and limitations of the system performance are often decided upon the type of memory architecture.

- Systems memory requirement depend primarily on the nature of the application that is planned to run on the system.

- Memory performance and capacity requirement for low cost systems are small, whereas memory throughput can be the most critical requirement in a complex, high performance system.

• Following are the factors that are to be considered while selecting the memory devices,

> Speed

- Data storage size and capacity

- Bus width

- Power consumption

- ≻ Cost

- Embedded system requirements:

- \*

- Program memory for holding control algorithm or embedded OS and the applications designed to run on top of OS.

- Data memory for holding variables and temporary data during task execution.

Memory for holding non-volatile data which are modifiable by the application.

- The memory requirement for an embedded system in terms of RAM (SRAM/DRAM) and ROM (EEPROM/FLASH/NVRAM) is solely dependent on the type of the embedded system and applications for which it is designed.

- There is no hard and fast rule for calculating the memory requirements.

- Lot of factors need to be considered for selecting the type and size of memory for embedded system.

- **Example:** Design of Embedded based electronic Toy.

- SOC or microcontroller can be selected based type(RAM &ROM) and size of on-chip memory for the design of embedded system.

- If on-chip memory is not sufficient then how much external memory need to be interfaced.

- If the ES design is RTOS based ,the RTOS requires certain amount of RAM for its execution and ROM for storing RTOS Image.

- The RTOS suppliers gives amount of run time RAM requirements and program memory requirements for the RTOS.

- Additional memory is required for executing user tasks and user applications.

- On a safer side, always add a buffer value to the total estimated RAM and ROM requirements.