# ANALOG & DIGITAL ELECTRONICS LECTURENOTES

B.TECH (IIYEAR- II SEM) (2024-25)

# Prepared by:

D. SANTHOSH KUMAR, Asst. Prof

**Department of Electronics & Communication Engineering**

# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(Autonomous Institution - UGC, Govt. of India)

Recognized under 2(f) and 12 (B) of UGC ACT 1956

(AffiliatedtoJNTUH, Hyderabad, Approved by AICTE - Accredited by NBA& NAAC - 'A' Grade - ISO 9001:2015Certified)

Maisammaguda, Dhulapally (PostVia. Kompally), Secunderabad - 500100, Telangana State, India

#### B. TECH: ELECTRICAL & ELECTRONICS ENGINEERING

#### **R22 - SYLLABUS**

# MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY II Year B.Tech EEE-II Sem L/T/P/C 3/0/0/3

### (R22A0461) ANALOG & DIGITAL ELECTRONICS

#### **OBJECTIVES** The main objectives of the course are:

- 1. Learn the concepts of load line analysis and biasing techniques

- 2. Learn the concepts of small signal analysis of BJT and FET

- 3. To understand basic number systems codes and logical gates.

- 4. To introduce the methods for simplifying Boolean expressions

- 5. To outline the formal procedures for the analysis and design of combinational circuits and sequential circuits

#### UNIT-I

#### **BJT Biasing:**

Transistor Biasing and Stabilization - Operating point, DC & AC load lines, Biasing - Fixed Bias, Self-Bias, Bias Stability, Bias Compensation using Diode and Transistor amplifying action.

**Signal Low Frequency BJT Amplifiers**: Transistor Hybrid model, Determination of h-parameters from transistor characteristics, Typical values of h- parameters in CE, CB and CC configurations

#### **UNIT-II**

#### Transistor at High Frequency:

Hybrid  $\pi$  model of Common Emitter transistor model and derivation of Hybrid  $\pi$  model elements.

FET Amplifiers: Analysis of Common Source and Common Drain JFET Amplifiers, Comparison of performance with BJT Amplifiers

#### **UNIT-III**

#### **Number System and Boolean Algebra:**

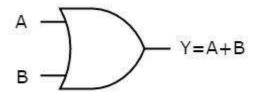

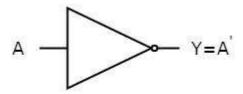

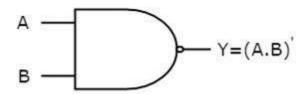

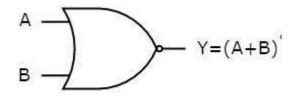

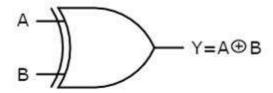

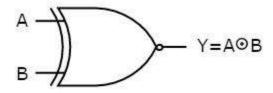

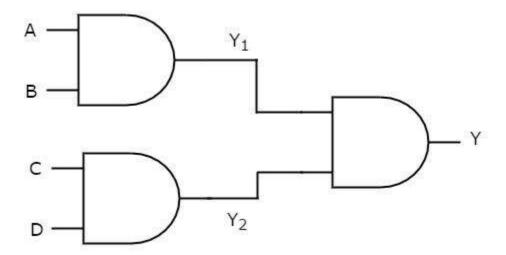

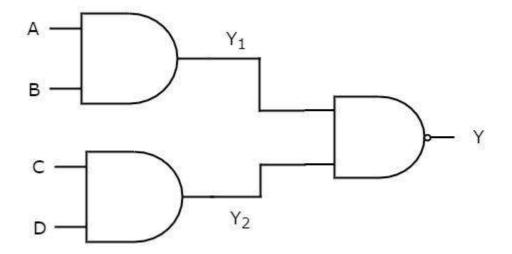

Number Systems, Base Conversion Methods, Complements of Numbers, Codes- Binary Codes, Binary Coded Decimal, Unit Distance Code, Digital Logic Gates (AND, NAND, OR, NOR, EX-OR, EX-NOR), Properties of XOR Gates, Universal Gates, Basic Theorems and Properties, Switching Functions, Canonical and Standard Form.

#### **UNIT-IV**

#### **Minimization Techniques:**

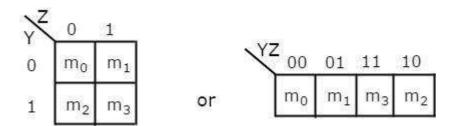

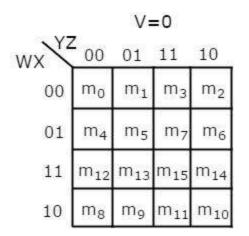

The Karnaugh Map Method, Three variables ,Prime and Essential Implications, Don't Care Map Entries, Using the Maps for Simplifying, Multilevel NAND/NOR realizations.

#### **UNIT-V**

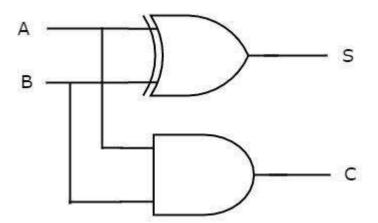

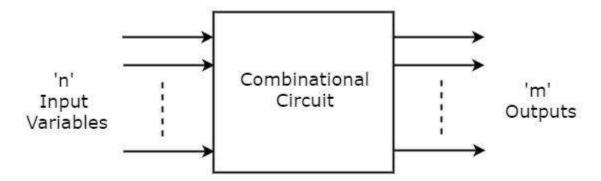

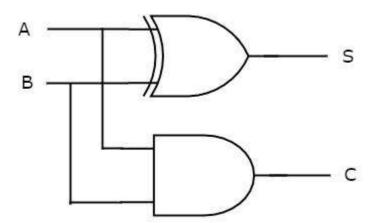

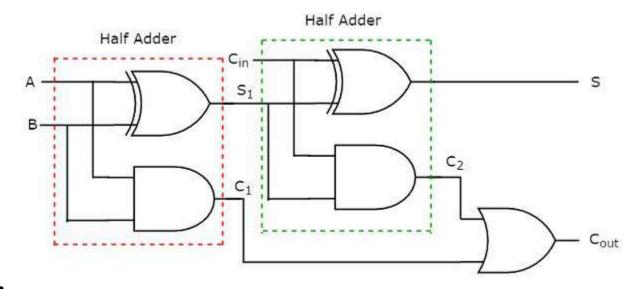

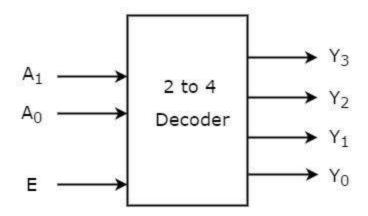

#### **Combinational Circuits:**

Design procedure – Half adder, Full Adder, Half sub-tractor, Full sub-tractor, Multiplexer/Demultiplexer Sequential circuits: Latches, Flip-Flops-SR, JK, D, T and master slave, characteristic tables and equation.

#### **TEXT BOOKS:**

- 1. "Electronic Devices & Circuits", Special Edition MRCET, McGraw Hill Publications, 2017.

- 2. Integrated Electronics Analog Digital Circuits, Jacob Millman and D. Halkias, McGraw Hill.

- 3. Electronic Devices and Circuits, S.Salivahanan, N.Suresh kumar, McGraw Hill.

- 4. M. Morris Mano, Digital Design, 3rd Edition, Prentice Hall of India Pvt. Ltd., 2003 /Pearson Education (Singapore) Pvt. Ltd., New Delhi, 2003.

- 5. Switching and Finite Automata Theory- Zvi Kohavi & Niraj K. Jha, 3rd Edition, Cambridge.

#### **REFERENCE BOOKS:**

- 1. Electronic Devices and Circuits, K.Lal Kishore B.S Publications

- 2. Electronic Devices and Circuits, G.S.N. Raju, I.K. International Publications, New Delhi, 2006.

- 3. John F. Wakerly, Digital Design, Fourth Edition, Pearson/PHI, 2006

- 4. John.M Yarbrough, Digital Logic Applications and Design, Thomson Learning, 2002.

- 5. Charles H.Roth. Fundamentals of Logic Design, Thomson Learning, 2003.

#### **OUTCOMES:**

After completion of the course, the student will be able to:

- 1. Design the amplifiers with various biasing techniques

- 2. Design single stage amplifiers using BJT and FET

- 3. Understand the basic postulates of Boolean algebra and shows the correlation between Boolean expressions

- 4. Learn the methods for simplifying Boolean expressions

- 5. Understand the formal procedures for the analysis and design of combinational circuits and sequential circuits

# **UNIT I:**Biasing and Stabilization:

**Biasing and Stabilization:** Operating point, the D.C Load line, Fixed bias, Collector to base bias, Selfbias techniques for stabilization, Stabilization factors, (s, s<sup>1</sup>), Bias Compensation using diode and transistor

### TRANSISTOR BIASING AND STABILIZATION

#### NEED FOR TRANSISTORBIASING

If the o/p signal must be a faithful reproduction of the i/p signal, the transistor must be operated in active region. That means an operating point has to be established in this region . To establish an operating point (proper values of collector current  $I_c$  and collector to emitter voltage  $V_{CE}$ ) appropriate supply voltages and resistances must be suitably chosen in the ckt. This process of selecting proper supply voltages and resistance for obtaining desired operating point or Q point is called as biasing and the ckt used for transistor biasing is called as biasingckt.

There are four conditions to be met by a transistor so that it acts as a faithful ampr:

- 1) Emitter base junction must be forward biased ( $V_{BE}$ =0.7Vfor Si, 0.2V for Ge) and collector base junction must be reverse biased for all levels of i/psignal.

- 2)  $V_{ce}$  voltage should not fall below  $V_{CE(sat)}$  (0.3V for Si, 0.1V for Ge) for any part of the i/p signal. For  $V_{CE}$  less than  $V_{CE(sat)}$  the collector base junction is not probably reverse biased.

- 3) The value of the signal I<sub>c</sub> when no signal is applied should be at least equal to the max. collector current t due to signal alone.

- 4) Max. rating of the transistor  $I_{c(max)}$ ,  $V_{CE(max)}$  and  $P_{D(max)}$  should not be exceeded at any value of i/p signal.

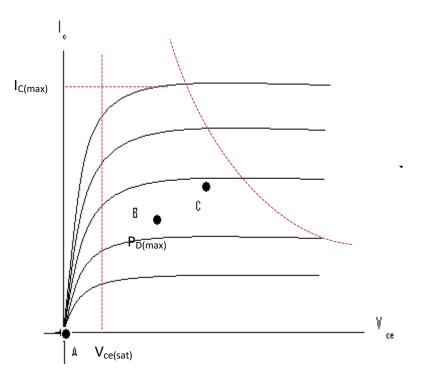

Consider the fig shown in fig 2.12. If operating point is selected at A, A represents a condition when no bias is applied to the transistor i.e,  $I_c=0$ ,  $V_{CE}=0$ . It does not satisfy the above said conditions necessary for faithful amplification.

Point C is too close to  $P_{D(max)}$  curve of the transistor. Therefore the o/p voltage swing in the positive direction is limited.

Point B is located in the middle of active region .It will allow both positive and negative half cycles in the o/p signal. It also provides linear gain and larger possible o/p voltages and currents

Hence operating point for a transistor amplifier is selected to be in the middle of active region.

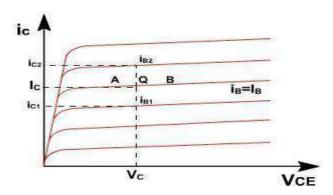

Fig 2.12 CE Output Characteristics

#### **DC LOADLINE**

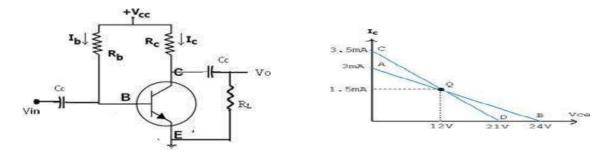

Referring to the biasing circuit of fig 2.13 a, the values of  $V_{CC}$  and  $R_C$  are fixed and  $I_C$  and  $V_{CE}$  are dependent on  $R_B$ .

Applying Kirchhoff's voltage law to the collector circuit in fig. 2.13, we get

Fig 2.13(a) CE Amplifier Circuit (b) Load line

$$Vcc = IcRc + Vce$$

The straight line represented by AB in fig2.13b is called the dc load line. The coordinates of the end point A are obtained by substituting  $V_{CE}=0$  in the above equation. Then  $Ic=\frac{Vcc}{Rc}$ . Therefore The coordinates of A are  $V_{CE}=0$  and  $Ic=\frac{Vcc}{Rc}$ .

The coordinates of B are obtained by substituting Ic=0 in the above equation. Then Vce = Vcc. Therefore the coordinates of B are  $V_{CE}$  =Vcc and Ic=0. Thus the dc load line AB can be drawn if the values of Rc and Vcc are known.

As shown in the fig2.13b, the optimum POINT IS LOCATED AT THE MID POINT OF THE MIDWAY BETWEEN a AND b. In order to get faithful amplification, the Q point must be well within the active region of the transistor.

Even though the Q point is fixed properly, it is very important to ensure that the operating point remains stable where it is originally fixed. If the Q point shifts nearer to either A or B, the output voltage and current get clipped, thereby o/p signal is distorted.

In practice, the Q-point tends to shift its position due to any or all of the following three main factors.

- 1) Reverse saturation current, Ico, which doubles for every 10°C raise intemperature

- 2) Base emitter Voltage ,VBE, which decreases by 2.5 mV per°C

- 3) Transistor current gain,  $h_{FE}$  or  $\beta$  which increases withtemperature.

If base current  $I_B$  is kept constant since  $I_B$  is approximately equal to Vcc/RB. If the transistor is replaced by another one of the same type, one cannot ensure that the new transistor will have identical parameters as that of the first one. Parameters such as  $\beta$  vary over a range. This results in the variation of collector current Ic for a given  $I_B$ . Hence , in the o/p characteristics, the spacing between the curves might increase or decrease which leads to the shifting of the Q-point to a location which might be completelyunsatisfactory.

#### **AC LOADLINE**

After drawing the dc load line, the operating point Q is properly located at the center of the dc load line. This operating point is chosen under zero input signal condition of the circuit. Hence the ac load line should also pas through the operating point Q. The effective ac load resistance  $R_{ac}$ , is a combination of  $R_C$  parallel to  $R_L$  i.e.  $R_{ac} = R_L \mid R_C$ . So the slope of the ac load line CQD will be  $\left(\frac{-1}{R_{ac}}\right)$ . To draw the ac load line, two end points, i.e.  $V_{CE(max)}$  and  $I_{C(max)}$  when the signal is applied are required.

$$V_{CE(\text{max})} = V_{CEO} + I_{CO}R_{ac}$$

, which locates point D on the Vce axis.

$$I_{c(\max)} = I_{CQ} + \frac{v_{CEQ}}{R_{gc}}$$

, which locates the point C on the I<sub>C</sub> axis.

By joining points c and D, ac load line CD is constructed. As  $R_C > R_{ac}$ , The dc load line is less steep than ac load line.

#### STABILITY FACTOR(S):

The rise of temperature results in increase in the value of transistor gain  $\beta$  and the leakage current Ico. So, I<sub>C</sub> also increases which results in a shift in operating point. Therefore, The biasing network should be provided with thermal stability. Maintenance of the operating point is specified by S, which indicates the degree of change in operating point due to change intemperature.

The extent to which I<sub>C</sub> is stabilized with varying I<sub>C</sub> is measured by a stability factor S

$$S = \frac{\partial \, I_{c}}{\partial \, I_{co}} \approx \, \frac{d \, I_{c}}{d \, I_{co}} \, \approx \, \frac{\Delta I_{c}}{\Delta \, I_{co}}, \, \beta \, \, and \, \, I_{B} \, \, constant$$

For CEconfiguration  $I_c = \beta I_B + (1 + \beta)I_{co}$

Differentiate the above equation w.r.t I<sub>C</sub>, We get

$$1 = \beta \frac{dI_B}{dI_C} + (1 + \beta) \frac{dI_{co}}{dI_c}$$

$$\therefore \left(1 - \beta \frac{dI_B}{dI_C}\right) = \frac{(\beta + 1)}{S}$$

$$\therefore S = \frac{1 + \beta}{1 - \beta \frac{dI_B}{dI_C}}$$

S should be small to have better thermal stability.

#### Stability factor S' and S":

S' is defined as the rate of change of I<sub>C</sub> with V<sub>BE</sub>, keeping I<sub>C</sub> and V<sub>BE</sub> constant.

$$\mathbf{S}' = \frac{\partial I_{c}}{\partial V_{BE}}$$

S" is defined as the rate of change of  $I_C$  with  $\beta$ , keeping  $I_{CO}$  and  $V_{BE}$  constant.

$$\boldsymbol{\mathcal{S}}^{\prime\prime} = \frac{\partial I_{c}}{\partial \boldsymbol{\beta}}$$

#### **METHODS OF TRANSISTORBIASING**

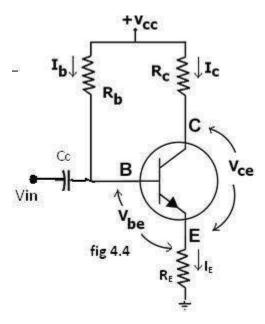

#### 1) Fixed bias (basebias)

Fig 2.14 Fixed Biasing Circuit

This form of biasing is also called *base bias*. In the fig 4.3 shown, the single power source (for example, battery) is used for both collector and base of a transistor, although separate batteries can also be used.

In the given circuit,

$$V_{cc} = I_B R_B + V_{be}$$

Therefore,  $I_B = (V_{cc} - V_{be})/R_B$

Since the equation is independent of current  $I_CR$ ,  $dI_B//dI_CR = 0$  and the stability factor is given by the equation.... reduces to

S=1+β

Since  $\beta$  is a large quantity, this is very poor biasing circuit. Therefore in practice the circuit is not used fo biasing.

For a given transistor,  $V_{be}$  does not vary significantly during use. As  $V_{cc}$  is of fixed value, on selection of R the base current  $I_B$  is fixed. Therefore this type is called *fixed bias* type of circuit.

Also for given circuit,  $V_{cc} = I_C R_C + V_{ce}$

Therefore,  $V_{ce} = V_{cc} - I_C R_C$

#### Merits:

- It is simple to shift the operating point anywhere in the active region by merely changing the base  $\operatorname{resistor}(R_B)$ .

- A very small number of components are required.

#### **Demerits:**

- The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

- Changes in  $V_{be}$  will change  $I_B$  and thus cause  $R_E$  to change. This in turn will alter the gain of the stage.

- When the transistor is replaced with another one, considerable change in the value ofβ can be expected. Due to this change the operating point willshift.

#### 2) EMITTER-FEEDBACKBIAS:

The emitter feedback bias circuit is shown in the fig 2.15. The fixed bias circuit is modified by attaching an external resistor to the emitter. This resistor introduces negative feedback that stabilizes the Q-point. From Kirchhoff's voltage law, the voltage across the base resistor is

$$V_{Rb} = V_{CC} - I_e R_e - V_{be}$$

.

Fig 2.15 Self Biasing Circuit

From Ohm's law, the base current is

$$I_b = V_{Rb} / R_b$$

.

The way feedback controls the bias point is as follows. If  $V_{be}$  is held constant and temperature increases, emitter current increases. However, a larger  $I_e$  increases the emitter voltage  $V_e = I_e R_e$ , which in turn reduces the voltage  $V_{Rb}$  across the base resistor. A lower base-resistor voltage drop reduces the base current, which results in less collector current because  $I_c = \beta I_B$ . Collector current and emitter current are related by  $I_c = \alpha I_e$  with  $\alpha \approx 1$ , so increase in emitter current with temperature is opposed, and operating point is kept stable.

Similarly, if the transistor is replaced by another, there may be a change in  $I_C$  (corresponding to change in  $\beta$ -value, for example). By similar process as above, the change is negated and operating point kept stable.

For the given circuit,

$$I_B = (V_{CC} - V_{be})/(R_B + (\beta+1)R_E).$$

#### Merits:

The circuit has the tendency to stabilize operating point against changes in temperature and  $\beta$ -value.

#### **Demerits:**

• In this circuit, to keep  $I_C$  independent of  $\beta$  the following condition must be met:

$$I_C = \beta I_B = \frac{\beta (V_{CC} - V_{be})}{R_B + (\beta + 1)R_E} \approx \frac{(V_{CC} - V_{be})}{R_E}$$

which is approximately the case if ( $\beta + 1$ )R<sub>E</sub>>> R<sub>B</sub>.

- As $\beta$ -valueisfixedforagiventransistor,thisrelationcanbesatisfiedeitherbykeeping R<sub>E</sub> very large, or making R<sub>B</sub> verylow.

- If  $R_E$  is of large value, high  $V_{CC}$  is necessary. This increases cost as well as precautions necessary whilehandling.

- If  $R_B$  is low, a separate low voltage supply should be used in the base circuit. Using two supplies of different voltages isimpractical.

- $\bullet$  In addition to the above,  $R_E$  causes ac feedback which reduces the voltage gain of theamplifier.

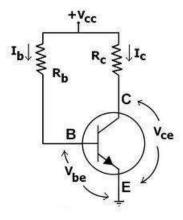

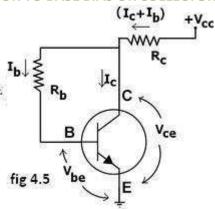

#### 3) COLLECTOR TO BASE BIAS OR COLLECTOR FEED-BACKBIAS:

Fig 2.16 Collector to Base Biasing Circuit

This configuration shown in fig 2.16 employs negative feedback to prevent thermal runaway and stabilize the operating point. In this form of biasing, the base resistor  $R_{\rm B}$  is connected to the collector instead of connecting it to the DC source  $V_{\rm cc}$ . So any thermal runaway will induce a voltage drop across the  $R_{\rm C}$  resistor that will throttle the transistor's base current.

From Kirchhoff's voltage law, the voltage  $V_{

m R_b}$ across the base resistor  $R_{

m b}$ is

$$V_{

m R_b} = V_{

m cc} - \overbrace{(I_{

m c} + I_{

m b})R_{

m c}}^{

m Voltage\ at\ base} - \overbrace{V_{

m be}}^{

m Voltage\ at\ base}.$$

By the Ebers–Moll model,  $I_c = \beta I_b$ , and so

$$V_{\rm R_b} = V_{\rm cc} - (\overbrace{\beta I_{\rm b}}^{I_{\rm c}} + I_{\rm b}) R_{\rm c} - V_{\rm be} = V_{\rm cc} - I_{\rm b} (\beta + 1) R_{\rm c} - V_{\rm be}.$$

From Ohm's law, the base current  $I_{

m b} = V_{

m R_b}/R_{

m b}$  , and so

$$\overbrace{I_{\rm b}R_{\rm b}}^{V_{\rm R_b}} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm be}.$$

Hence, the base current  $I_{\rm b}$ is

$$I_{\rm b} = \frac{V_{\rm cc} - V_{\rm be}}{R_{\rm b} + (\beta + 1)R_{\rm c}}$$

If  $V_{\text{be}}$  is held constant and temperature increases, then the collector current  $I_{\text{c}}$  increases. However, a larger  $I_{\text{c}}$  causes the voltage drop across resistor  $R_{\text{c}}$  to increase, which in turn reduces the voltage  $V_{\rm R_bacross}$  the base resistor  $R_{\rm b}$ . A lower base-resistor voltage drop reduces the base current  $I_{\rm b}$ , which results in less collector current  $I_{\rm c}$ . Because an increase in collector current with temperature is opposed, the operating point is keptstable.

#### Merits:

• Circuit stabilizes the operating point against variations in temperature and  $\beta$ (i.e. replacement oftransistor)

#### **Demerits:**

In this circuit, to keep  $I_c$  independent of  $\beta$ , the following condition must be met:

$$I_{\rm c} = \beta I_{\rm b} = \frac{\beta (V_{\rm cc} - V_{\rm be})}{R_{\rm b} + R_{\rm c} + \beta R_{\rm c}} \approx \frac{(V_{\rm cc} - V_{\rm be})}{R_{\rm c}}$$

which is the case when

$$\beta R_{\rm c} \gg R_{\rm b}$$

.

- As  $\beta$ -value is fixed (and generally unknown) for a given transistor, this relation can be satisfied either by keeping  $R_c$  fairly large or making  $R_b$ verylow.

- ullet If  $R_{

m c}$  is large, a high  $V_{

m cc}$  is necessary, which increases cost as well as precautions necessary whilehandling.

- If  $R_b$  is low, the reverse bias of the collector–base region is small, which limits the range of collector voltage swing that leaves the transistor in active mode.

- The resistor  $R_b$  causes an AC feedback, reducing the <u>voltage gain</u> of the amplifier. This undesirable effect is a trade-off for greater <u>Q-points</u> tability.

**Usage:** The feedback also decreases the input impedance of the amplifier as seen from the base, which can be advantageous. Due to the gain reduction from feedback, this biasing form is used only when the trade-off for stability iswarranted.

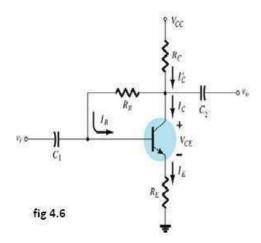

#### 4) COLLECTOR –EMITTER FEEDBACKBIAS:

Fig 2.17 Collector-Emitter Biasing Circuit

The above fig 2.17shows the collector –emitter feedback bias circuit that can be obtained by applying both the collector feedback and emitter feedback. Here the collector feedback is provided by connecting a resistance RB from the collector to the base and emitter feedback is provided by connecting an emitter Re from emitter to ground. Both feed backs are used to control collector current and base current IB in the opposite direction to increase the stability as compared to the previous biasing circuits.

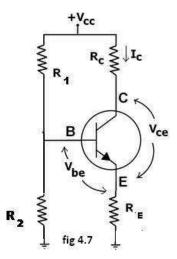

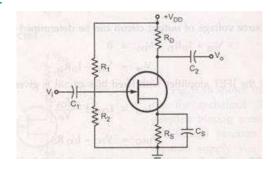

#### 5) VOLTAGE DIVIDER BIAS OR SELF BIAS OR EMITTERBIAS

The voltage divider as shown in the fig 2.18 is formed using external resistors  $R_1$  and  $R_2$ . The voltage across  $R_2$  forward biases the emitter junction. By proper selection of resistors  $R_1$  and  $R_2$ , the operating point of the transistor can be made independent of  $\beta$ . In this circuit, the voltage divider holds the base voltage fixed independent of base current provided the divider current is large compared to the base current. However, even with a fixed base voltage, collector current varies with temperature (for example) so an emitter resistor is added to stabilize the Q-point, similar to the above circuits with emitter resistor.

Fig 2.18 Voltage Divider Biasing Circuit

In this circuit the base voltage is given by:

$$\begin{split} V_B =_{\text{voltageacross}} R_2^{} = V_{cc} \frac{R_2}{(R_1 + R_2)} - I_B \frac{R_1 R_2}{(R_1 + R_2)} \\ \approx V_{cc} \frac{R_2}{(R_1 + R_2)}_{\text{provided}} I_B << I_2 = V_B/R_2. \end{split}$$

Also  $V_B = V_{be} + I_E R_E$

For the given circuit,

$$I_B = \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{(\beta + 1)R_E + R_1 \parallel R_2}.$$

Let the current in resistor R1 is I1 and this is divided into two parts – current through base and resistor R2. Since the base current is very small so for all practical purpose it is assumed that I1 also flows through R2, so we have

$$\begin{split} I_1 &= \frac{V_{CC}}{R_1 + R_2} \\ V_2 &= \frac{V_{CC}}{R_1 + R_2} \cdot R_2 \end{split}$$

Applying KVL in the circuit, we have

$$\begin{split} V_2 &= V_{BE} + V_E \\ V_2 &= V_{BE} + I_E R_E \end{split}$$

$$\begin{split} I_E &= \frac{V_2 - V_{BE}}{R_E} \\ I_C &= \frac{V_2 - V_{BE}}{R_E} \quad \because I_C \cong I_E \\ I_C &= \frac{\frac{V_C - V_{BE}}{R_E} \cdot R_2 - V_{BE}}{R_E} \end{split}$$

It is apparent from above expression that the collector current is independent of ? thus the stability is excellent. In all practical cases the value of VBE is quite small in comparison to the V2, so it can be ignored in the above expression so the collector current is almost independent of the transistor parameters thus this arrangement provides excellent stability.

Again applying KVL in collector circuit, we have

$$\begin{split} V_{CC} &= I_C R_C + V_{CE} + I_E R_E \\ &\because I_C \cong I_E \\ &\because V_{CC} = I_C R_C + V_{CE} + I_C R_E \\ V_{CE} &= V_{CC} - I_C (R_C + R_E) \end{split}$$

The resistor RE provides stability to the circuit. If the current through the collector rises, the voltage across the resistor RE also rises. This will cause VCE to increase as the voltage V2 is independent of collector current. This decreases the base current, thus collector current increases to its formervalue.

Stability factor for such circuit arrangement is given by

$$\begin{split} S &= \frac{(1+\beta)\left(R_{eq} + R_E\right)}{R_{eq} + R_E(1+\beta)} \\ R_{eq} &= R_1 || R_2 \\ S &= \frac{(1+\beta)\left(1 + \frac{R_{eq}}{R_E}\right)}{\frac{R_{eq}}{R_E} + 1 + \beta} \end{split}$$

If Req/RE is very small compared to 1, it can be ignored in the above expression thus we have

$$S = \frac{1+\beta}{1+\beta} = 1$$

Which is excellent since it is the smallest possible value for the stability. In actual practice the value of stability factor is around 8-10, since Req/RE cannot be ignored as compared to 1.

#### Merits:

- Unlike above circuits, only one dc supply isnecessary.

- Operating point is almost independent of βvariation.

- Operating point stabilized against shift intemperature.

#### **Demerits:**

• In this circuit, to keep  $I_C$  independent of  $\beta$  the following condition must be et:

$$I_C = \beta I_B = \beta \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{(\beta + 1)R_E + R_1 \parallel R_2} \approx \frac{\frac{V_{CC}}{1 + R_1/R_2} - V_{be}}{R_E},$$

which is approximately the caseif  $(eta+1)R_E >> R_1 \parallel R_2$

where  $R_1 \mid \mid R_2$  denotes the equivalent resistance of  $R_1$  and  $R_2$  connected in parallel.

- As  $\beta$ -value is fixed for a given transistor, this relation can be satisfied either by keeping  $R_E$  fairly large, or making  $R_1 \mid R_2$  verylow.

- If  $R_E$  is of large value, high  $V_{CC}$  is necessary. This increases cost as well as precautions necessary whilehandling.

- If  $R_1 \mid \mid R_2$  is low, either  $R_1$  is low, or  $R_2$  is low, or both are low. A low  $R_1$  raises  $V_B$  closer to  $V_C$ , reducing the available swing in collector voltage, and limiting how large  $R_C$ can be made without driving the transistor out of active mode. A low  $R_2$  lowers  $V_{be}$ , reducing the allowed collector current. Lowering both resistor values draws more current from the power supply and lowers the input resistance of the amplifier as seen from thebase.

- $\bullet$  AC as well as DC feedback is caused by  $R_E$ , which reduces the AC voltage gain of the amplifier. A method to avoid AC feedback while retaining DC feedback is discussed below.

**Usage:** The circuit's stability and merits as above make it widely used for linear circuits.

#### BIAS COMPENSATION USING DIODE ANDTRANSISTOR

The various biasing circuits considered use some type of negative feedback to stabilize the operation point. Also, diodes, thermistors and sensistors can be used to compensate for variations in current.

#### **DIODE COMPENSATION:**

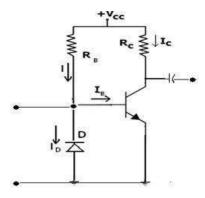

Fig 2.19Diode Compensation Circuit

The following fig 2.19 shows a transistor amplifier with a diode D connected across the base-emitter junction for compensation of change in collector saturation current  $I_{CO}$ . The diode is of the same material as the transistor and it is reverse biased by e the emitter-base junction voltage  $V_{BE}$ , allowing the diode reverse saturation current  $I_O$  to flow through diode D. The base current $I_B=I-I_O$ .

As long as temperature is constant, diode D operates as a resistor. As the temperature increases,  $I_{CO}$  of the transistor increases. Hence, to compensate for this, the base current  $I_B$  should be decreased.

The increase in temperature will also cause the leakage current  $I_0$  through D to increase and thereby decrease the base current  $I_B$ . This is the required action to keep Ic constant.

This type of bias compensation does not need a change in Ic to effect the change in  $I_C$ , as both  $I_C$  and  $I_C$  can track almost equally according to the change intemperature.

#### **THERMISTOR COMPENSATION:**

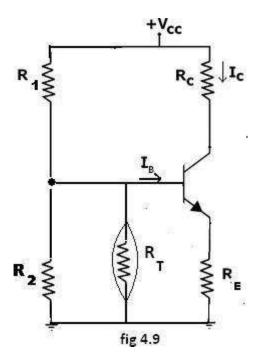

The following fig2.20 a thermistor  $R_T$ , having a negative temperature coefficient is connected in parallel with  $R_2$ . The resistance of thermistor decreases exponentially with increase of temperature. An increase of temperature will decrease the base voltage  $V_{BE}$ , reducing  $I_B$  and  $I_C$ .

Fig 2.20 Thermistor Compensation

#### **SENSISTOR COMPENSATION:**

In the following fig2.21 shown a sensistor Rs having a positive temperature coefficient is connected across  $R_1$  or  $R_E$ . Rs increases with temperature. As the temperature increases, the equivalent resistance of the parallel combination of R1 and Rs also increases and hence  $V_{BE}$  decreases, reducing  $I_B$  and  $I_C$ . This reduced  $I_C$  compensates for increased  $I_C$  caused by the increase in  $V_{BE}$ ,  $I_{CO}$  and  $I_C$  due totemperature.

Fig 2.21 Sensistor Compensation

#### **UNIT I-II**

# **Signal Low Frequency BJT Amplifiers:**

Transistor Hybrid model, Determination of h parameters from transistor characteristics, Typical values of h- parameters in CE, CB and CC configurations, Analysis of CE, CC, CB Amplifiers and CE Amplifier with emitter resistance, low frequency response of BJT Amplifiers

#### BJT HYBRID MODEL

#### Small signal low frequency transistor Models:

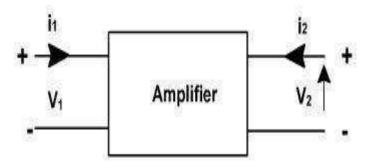

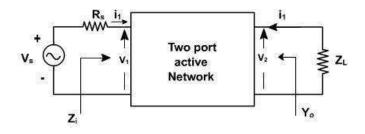

All the transistor amplifiers are two port networks having two voltages and two currents. The positive directions of voltages and currents are shown in **fig. 1**.

Fig. 3.1: Transistor as a two port Network

A two-port network is represented by four external variables: voltage  $V_1$  and current  $I_1$  at the input port, and voltage  $V_2$  and current  $I_2$  at the output port, so that the two-port network can be treated as a black box modeled by the relationships between the four variables,  $V_1$ ,  $V_2$ ,  $I_1$ ,  $I_2$ . Out of four variables two can be selected as are independent variables and two are dependent variables. The dependent variables can be expressed interns of independent variables. This leads to various two port parameters out of which the following three are important:

- 1. Impedance parameters(z-parameters)

- 2. Admittance parameters(y-parameters)

- 3. Hybrid parameters(h-parameters)

#### z-parameters

A two-port network can be described by z-parameters as

$$\begin{array}{l} V_1 = Z_{11}I_1 + Z_{12}I_2 \\ V_2 = Z_{21}I_1 + Z_{22}I_2 \end{array}$$

In matrix form, the above equation can be rewritten as

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} z_{11} & z_{12} \\ z_{21} & z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

Where

$$z_{11} = \left. \frac{V_1}{I_1} \right|_{I_2 = 0}$$

Input impedance with output port open circuited

$$z_{12} = \left. \frac{V_1}{I_2} \right|_{I_1=0}$$

Reverse transfer impedance with input port open circuited

$$z_{21} = \frac{V_2}{I_1} \Big|_{I_2=0}$$

Forward transfer impedance with output port open circuited

$$z_{22} = \left. \frac{V_2}{I_2} \right|_{I_1=0}$$

Output impedance with input port open circuited

#### Y-parameters

A two-port network can be described by Y-parameters as

$$\begin{split} I_1 &= Y_{11}V_1 + Y_{12}V_2 \\ I_2 &= Y_{21}V_1 + Y_{22}V_2 \end{split}$$

In matrix form, the above equation can be rewritten as

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

$$y_{11} = \left. \frac{I_1}{V_1} \right|_{V_2 = 0}$$

Input admittance with output port short circuited

$$y_{12} = \left. \frac{I_1}{V_2} \right|_{V_1 = 0}$$

Reverse transfer admittance with input port short circuited

$$y_{21} = \left. \frac{I_2}{V_1} \right|_{V_2 = 0}$$

Forward transfer admittance with output port short circuited

$$y_{22} = \left. \frac{I_2}{V_2} \right|_{V_1 = 0}$$

Output admittance with input port short circuited

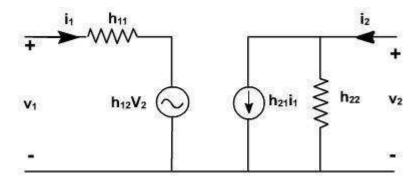

#### Hybrid parameters (h-parameters)

If the input current I1 and output voltage V2 are taken as independent variables, the dependent variables V1 and I2 can be written as

$$\begin{bmatrix} V_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ V_2 \end{bmatrix}$$

Where  $h_{11}$ ,  $h_{12}$ ,  $h_{21}$ ,  $h_{22}$  are called as hybrid parameters.

$$h_{11} = \frac{V_1}{I_1} \bigg|_{V_2 = 0}$$

Input impedence with o/p port short circuited

$$h_{12} = \left. \frac{V_1}{V_2} \right|_{I_1 = 0}$$

Reverse voltage transfer ratio with i/p port open circuited

$$h_{21} = \left. \frac{I_2}{I_1} \right|_{V_2 = 0}$$

Forward voltage transfer ratio with o/p port short circuited

$$h_{22} = \left. \frac{I_2}{V_2} \right|_{I_1 = 0}$$

output impedence with i/p port open circuited

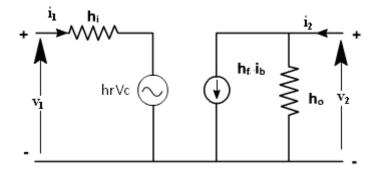

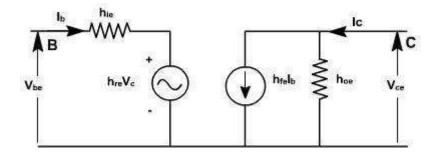

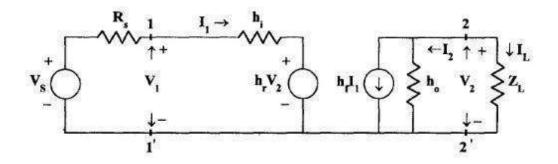

#### THE HYBRID MODEL FOR TWO PORT NETWORK:

Based on the definition of hybrid parameters the mathematical model for two pert networks known as h-parameter model can be developed. The hybrid equations can be written as:

$$V_1 = h_i I_1 + h_r V_2$$

$$I_2 = h_f I_1 + h_o V_2$$

(The following convenient alternative subscript notation is recommended by the **IEEE Standards**:

f = 21 =forward transfer r = 12 =reverse transfer)

We may now use the four h parameters to construct a mathematical model of the device of Fig.(1). The hybrid circuit for any device indicated in Fig.(2). We can verify that the model of Fig.(2) satisfies above equations by writing Kirchhoff'svoltage and current laws for input and output ports.

If these parameters are specified for a particular configuration, then suffixes e,b or c are also included, e.g.  $h_{fe}$ ,  $h_{ib}$  are h parameters of common emitter and common collector amplifiers

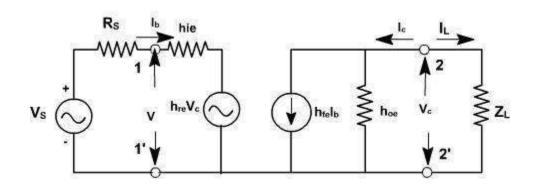

Using two equations the generalized model of the amplifier can be drawn as shown in fig. 3.2.

Fig.3.2:-h-parameter equivalent of Transistor

#### TRANSISTOR HYBRID MODEL:

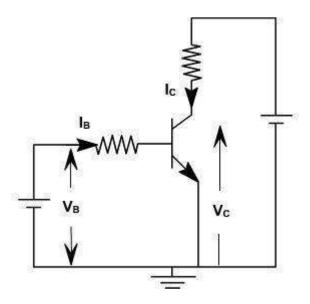

The hybrid model for a transistor amplifier can be derived as follow:

Let us consider CE configuration as show in <u>fig. 3.3</u>. The variables,  $i_B$ ,  $i_C$ ,  $v_C$ , and  $v_B$  represent total instantaneous currents and voltages  $i_B$  and  $v_C$  can be taken as independent variables and  $v_B$ ,  $I_C$  as dependent variables.

Fig. 3.3 CE Transistor Amplifier

$$V_B = f1 (i_B, v_C)$$

$$I_C = f2 (i_B, v_C).$$

Using Taylor's series expression, and neglecting higher order terms we obtain.

$$\Delta v_{B} = \frac{\partial f_{1}}{\partial i_{B}} \bigg|_{V_{C}} \Delta i_{B} + \frac{\partial f_{1}}{\partial v_{C}} \bigg|_{i_{B}} \Delta v_{C}$$

$$\Delta i_{_{\textstyle C}} = \frac{\partial \, f_{_{\textstyle 2}}}{\partial i_{_{\textstyle B}}}\bigg|_{_{\textstyle V_{_{\textstyle C}}}} \, \Delta i_{_{\textstyle B}} \ + \ \frac{\partial f_{_{\textstyle 2}}}{\partial v_{_{_{\textstyle C}}}}\bigg|_{i_{_{\textstyle B}}} \, \Delta v_{_{_{\textstyle C}}}$$

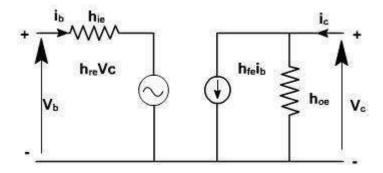

The partial derivatives are taken keeping the collector voltage or base current constant. The  $\Delta$   $v_B$ ,  $\Delta$   $v_C$ ,  $\Delta$   $i_B$ ,  $\Delta$   $i_C$  represent the small signal (incremental) base and collector current and voltage and can be represented as  $v_B$ ,  $i_C$ ,  $i_B$ ,  $v_C$

$$\therefore v_b = h_{ie} i_B + h_{re} v_C$$

$$i_C = h_{fe} i_B + h_{oe} v_b$$

where

$$\begin{split} h_{ie} &= \frac{\partial f_1}{\partial i_B}\bigg|_{v_C} &= \left. \frac{\partial v_B}{\partial i_B}\right|_{v_C}; \qquad h_{re} &= \left. \frac{\partial f_1}{\partial v_C}\right|_{i_B} &= \left. \frac{\partial v_B}{\partial v_C}\right|_{i_B} \\ h_{fe} &= \left. \frac{\partial f_2}{\partial i_B}\right|_{v_C} &= \left. \frac{\partial i_C}{\partial i_B}\right|_{v_C}; \qquad h_{oe} &= \left. \frac{\partial f_2}{\partial v_C}\right|_{i_B} &= \left. \frac{\partial v_B}{\partial v_C}\right|_{i_B} \end{split}$$

Fig. 3.4:h-parameter model of CE Configuration

To determine the four h-parameters of transistor amplifier, input and output characteristic are used. Input characteristic depicts the relationship between input voltage and input current with output voltage as parameter. The output characteristic depicts the relationship between output voltage and output current with input current as parameter. <u>Fig. 5</u>, shows the output characteristics of CE amplifier.

$$h_{\text{fe}} = \frac{\partial i_{\text{C}}}{\partial i_{\text{B}}} \bigg|_{\text{V}_{\text{C}}} = \frac{i_{\text{C2}} - i_{\text{C1}}}{i_{\text{b2}} - i_{\text{b1}}}$$

Fig. 3.5Transistor CE Configuration output characteristics

The current increments are taken around the quiescent point Q which corresponds to  $i_B = I_B$  and to the collector voltage  $V_{CE} = V_C$

$$h_{oe} = \frac{\partial i_C}{\partial V_C} \bigg|_{i_B}$$

The value of  $h_{oe}$  at the quiescent operating point is given by the slope of the output characteristic at the operating point (i.e. slope of tangent AB).

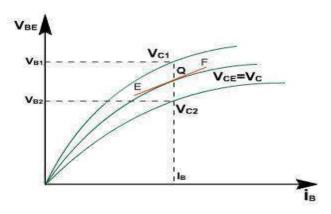

$$h_{ie} = \left. \frac{\partial V_B}{\partial i_B} \right| \approx \left. \frac{\Delta V_B}{\Delta i_B} \right|_{V_C}$$

h<sub>ie</sub> is the slope of the appropriate input on fig. 3.6, at the operating point (slope of tangent EF at Q).

$$h_{\text{re}} = \left. \frac{\partial V_{\text{B}}}{\partial V_{\text{C}}} = \left. \frac{\Delta V_{\text{B}}}{\Delta V_{\text{C}}} \right|_{I_{\text{B}}} = \frac{V_{\text{B2}} - V_{\text{B1}}}{V_{\text{C2}} - V_{\text{C1}}}$$

Fig. 3.6 Calculation of h-parameters from output characteristics

A vertical line on the input characteristic represents constant base current. The parameter hre can be obtained from the ratio ( $V_{B2}$ –  $V_{B1}$ ) and ( $V_{C2}$ –  $V_{C1}$ ) for at Q.

Typical CE h-parametersof transistor 2N1573 are given below:

$h_{ie} = 1000 \text{ ohm}.$

$h_{re} = 2.5 * 10 - 4$

$h_{fe} = 50$

$h_{oe} = 25 \mathbb{Z} \Lambda / V$

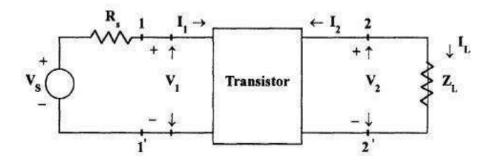

#### **ANALYSIS OF A TRANSISTOR AMPLIFIER USING H-PARAMETERS:**

To form a transistor amplifier it is only necessary to connect an external load and signal source as indicated in <u>fig. 3.7</u> and to bias the transistor properly.

#### Fig. 3.7 Transistor two port Network

Consider the two-port network of CE amplifier.  $R_S$  is the source resistance and  $Z_L$  is the load impedence h-parameters are assumed to be constant over the operating range. The ac equivalent circuit is shown in <u>fig. 2</u>. (Phasor notations are used assuming sinusoidal voltage input). The quantities of interest are the current gain, input impedence, voltage gain, and output impedence.

Fig 3.8:h parameter equivalent of Transistor in CE configuration

#### **Current gain:**

For the transistor amplifier stage, Ai is defined as the ratio of output to input currents.

$$A_{I} = \frac{I_{L}}{I_{1}} = \frac{-I_{2}}{I_{1}}$$

#### Input impedence:

The impedence looking into the amplifier input terminals (1,1') is the input impedance  $Z_i$

$$\begin{split} Z_i &= \frac{V_b}{I_b} \\ V_b &= h_{ie} I_b + h_{re} V_c \\ \frac{V_b}{I_b} &= h_{ie} + h_{re} \frac{V_c}{I_b} \\ &= h_{ie} - \frac{h_{re} I_c Z_L}{I_b} \\ \therefore Z_i &= h_{ie} + h_{re} A_1 Z_L \\ &= h_{ie} - \frac{h_{re} h_{fe} Z_L}{1 + h_{oe} Z_L} \\ \therefore Z_i &= h_{ie} - \frac{h_{re} h_{fe}}{Y_L + h_{oe}} \end{split} \quad \text{(since } Y_L = \frac{1}{Z_L} )$$

#### Voltage gain:

The ratio of output voltage to input voltage gives the gain of the transistors.

$$A_{v} = \frac{V_{C}}{V_{b}} = -\frac{I_{C}Z_{L}}{V_{b}}$$

$$\therefore A_{v} = \frac{I_{B}A_{i}Z_{L}}{V_{b}} = \frac{A_{i}Z_{L}}{Z_{i}}$$

#### **Output Admittance:**

$$Y_{0} = \frac{I_{c}}{V_{c}} \Big|_{V_{s}} = 0$$

$$I_{c} = |h_{fe}|_{b} + h_{oe}|_{V_{c}}$$

$$\frac{I_{c}}{V_{c}} = |h_{fe}|_{\frac{I_{b}}{V_{c}}} + h_{oe}$$

$$when |V_{s}| = 0, \quad R_{s}, I_{b}|_{b} + h_{fe}, I_{b}|_{b} + h_{re}|_{V_{c}} = 0.$$

$$\frac{I_{b}}{V_{c}} = -\frac{h_{re}}{R_{s} + h_{fe}}$$

$$\therefore |Y_{0}| = |h_{oe}|_{c} - \frac{h_{re}|_{h_{fe}}}{R_{s} + h_{fe}}$$

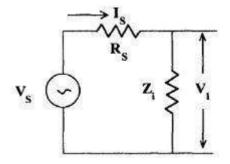

Voltage amplification taking into account source impedance ( $R_{\rm S}$ ) is given by

$$\begin{split} A_{VS} &= \frac{\bigvee_{c}}{\bigvee_{s}} = \frac{\bigvee_{c}}{\bigvee_{b}} \ \star \frac{\bigvee_{b}}{\bigvee_{s}} \\ &= A_{V} \cdot \frac{Z_{i}}{Z_{i} + R_{s}} \\ &= \frac{A_{i}}{Z_{i} + R_{s}} \end{split}$$

It is defined as

$A_v$  is the voltage gain for an ideal voltage source ( $R_v = 0$ ).

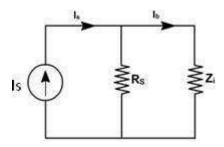

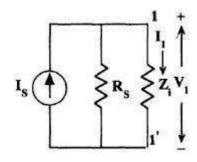

Consider input source to be a current source Is in parallel with a resistance Rs as shown in fig. 3.

In this case, overall current gain A<sub>IS</sub> is defined as

$$\begin{split} A_{I_{S}} &= \frac{I_{L}}{I_{S}} \\ &= -\frac{I_{c}}{I_{b}} \\ &= -\frac{I_{c}}{I_{b}} * \frac{I_{b}}{I_{s}} \qquad \left(I_{b} = \frac{I_{S} * R_{S}}{R_{S} + Z_{i}}\right) \\ &= A_{I} * \frac{R_{S}}{R_{S} + Z_{i}} \end{split}$$

$$If R_{S} \to \infty, \qquad A_{IS} \to A_{I}$$

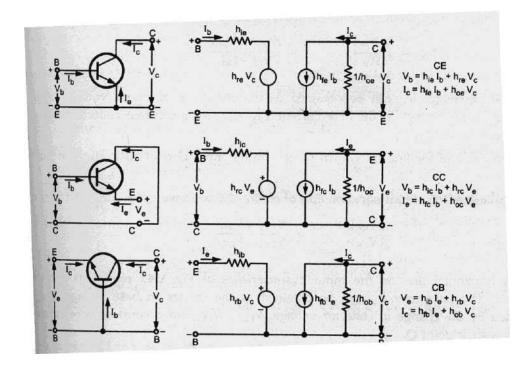

#### h-parameters

To analyze multistage amplifier the h-parameters of the transistor used are obtained from manufacture data sheet. The manufacture data sheet usually provides h-parameter in CE configuration. These parameters may be converted into CC and CB values. For example <u>fig. 4</u>hrc in terms of CE parameter can be obtained as follows.

Fig. 3.9 CE h-parameter model

For CE transistor configuaration

Vbe = hie Ib + hre Vce

Ic = h fe Ib + hoe Vce

The circuit can be redrawn like CC transistor configuration as shown in fig. 5.

Vbc = hie Ib + hrc Vec

Ic = hfe Ib + hoe Vec

Fig 3.10 hybrid model for transistor in three different configurations

# Typical h-parameter values for a transistor

| Parameter      | CE                     | CC      | СВ                   |

|----------------|------------------------|---------|----------------------|

| h <sub>i</sub> | 1100 Ω                 | 1100 Ω  | 22 Ω                 |

| h <sub>r</sub> | 2.5 × 10 <sup>-4</sup> | 1       | 3 × 10 <sup>-4</sup> |

| h <sub>f</sub> | 50                     | -51     | -0.98                |

| h <sub>o</sub> | 25 μΑ/V                | 25 μΑ/V | 0.49 μΑ/V            |

# Analysis of a Transistor amplifier circuit using h-parameters

A transistor amplifier can be constructed by connecting an external load and signal source and biasing the transistor properly.

Fig.3.11 Basic Amplifier Circuit

The two port network of Fig. 3.11 represents a transistor in any one of its configuration. It is assumed that h-parameters remain constant over the operating range. The input is sinusoidal and  $I_1$ ,  $V_1$ ,  $I_2$  and  $V_2$  are phase quantities

Fig. 3.12 Transistor replaced by its Hybrid Model

### Current Gain or Current Amplification (Ai)

For transistor amplifier the current gain  $A_i$  is defined as the ratio of output current to input current,i.e,

$$A_i = I_L / I_1 = -I_2 / I_1$$

From the circuit of Fig

$$I_2 = h_f I_1 + h_o V_2$$

Substituting  $V_2 = I_L Z_L = -I_2 Z_L$

$$I_2 = h_f I_1 - I_2 Z_L h_o$$

$$I_2 + I_2 Z_L h_0 = h_f I_1$$

$$I_2(1+ Z_L h_o) = h_f I_1$$

$$A_i = -I_2 / I_1 = -h_f / (1 + Z_L h_o)$$

Therefore,

$$A_i = -h_f / (1 + Z_L h_o)$$

#### Input Impedence (Z<sub>i</sub>)

In the circuitof Fig  $\,$ , R<sub>S</sub>isthesignalsourceresistance. The impedence seen when looking into the amplifier terminals (1,1') is the amplifier input impedence Z<sub>i</sub>,

$$Z_i = V_1 / I_1$$

From the input circuit of Fig  $V_1 = h_i I_1 + h_r V_2$

$$Z_i = (h_i I_1 + h_r V_2) / I_1$$

$$= h_i + h_r V_2 / I_1$$

Substituting

$$V_2 = -I_2 Z_L = A_1 I_1 Z_L$$

$$Z_i = h_i + h_r A_1 I_1 Z_L / I_1$$

$$= h_i + h_r A_1 Z_L$$

Substituting for  $A_{i}$

$$Z_i = h_i - h_f h_r Z_L / (1 + h_o Z_L)$$

=

$$h_i$$

-  $h_f$   $h_r$   $Z_L$  /  $Z_L$ (1/ $Z_L$ +  $h_o$ )

Taking the Load admittance as  $Y_L = 1/Z_L$

$$Z_i = h_i - h_f h_r / (Y_L + h_o)$$

#### Voltage Gain or Voltage Gain Amplification Factor(A<sub>v</sub>)

The ratio of output voltage V<sub>2</sub> to input voltage V<sub>1</sub> give the voltage gain of the transistor i.e,

$$A_v = V_2 / V_1$$

Substituting

$$V_2 = -I_2 Z_L = A_1 I_1 Z_L$$

$$A_{V} = A_{1}I_{1}Z_{L} / V_{1} = A_{i}Z_{L} / Z_{i}$$

#### **Output Admittance (Yo)**

$Y_0$  is obtained by setting  $V_S$  to zero,  $Z_L$  to infinity and by driving the output terminals from a generator  $V_2$ . If the current  $V_2$  is  $I_2$  then  $Y_0 = I_2/V_2$  with  $V_S = 0$  and  $R_L = \infty$ .

From the circuit of fig

$$I_2 = h_f I_1 + h_o V_2$$

Dividing by V<sub>2</sub>,

$$I_2 / V_2 = h_f I_1 / V_2 + h_o$$

With  $V_2$ = 0, by KVL in input circuit,

$$R_SI_1 + h_i I_1 + h_rV_2 = 0$$

$$(R_S + h_i) I_1 + h_r V_2 = 0$$

Hence,

$$I_2 / V_2 = -h_r / (R_S + h_i)$$

=

$$h_f (-h_r/(R_S + h_i)+h_o$$

$$Y_o = h_o - h_f h_r / (R_S + h_i)$$

The output admittance is a function of source resistance. If the source impedence is resistive then  $Y_0$  is real.

Voltage Amplification Factor(A<sub>vs</sub>) taking into account the resistance (R<sub>s</sub>) of the source

Fig. 3.13 Thevenin's Equivalent Input

Circuit This overall voltage gain  $A_{\nu s}$  is given by

$$A_{vs} = V_2 / V_S = V_2 V_1 / V_1 V_S = A_v V_1 / V_S$$

From the equivalent input circuit using Thevenin's equivalent for the source shown in Fig. 5.6

$$V_1 = V_S Z_i / (Z_{i+} R_S)$$

$$V_1 / V_S = Z_i / (Z_i + R_S)$$

Then,

$$A_{vs} = A_v Z_i / (Z_i + R_S)$$

Substituting  $A_v = A_i Z_L / Z_i$

$$A_{vs} = A_i Z_L / (Z_i + R_S)$$

$$A_{vs} = A_i Z_L R_S / (Z_i + R_S) R_S$$

$$A_{vs} = A_{is}Z_L/R_S$$

Current Amplification (Ais) taking into account the source Resistance(Rs)

Fig. 3.14 Norton's Equivalent Input Circuit

The modified input circuit using Norton's equivalent circuit for the calculation of Ais is shown in Fig. 1.7

Overall Current Gain,  $A_{is} = -I_2 / I_S = -I_2I_1 / I_1 I_S = A_i I_1 / I_S$

From Fig. 1.7

$$I_1 = I_S R_S / (R_S + Z_i)$$

$$I_1 / I_S = R_S / (R_S + Z_i)$$

andhence,

$$A_{is} = A_i R_S / (R_S + Z_i)$$

### Operating Power Gain (A<sub>P</sub>)

The operating power gain A<sub>P</sub> of the transistor is defined as

$$A_P = P_2 / P_1 = -V_2 I_2 / V_1 I_1 = A_v A_i = A_i A_i Z_L / Z_i$$

$A_P = A_i^2 (Z_L / Z_i)$

## Small Signal analysis of a transistor amplifier

| $A_i = -h_f / (1 + Z_L h_o)$                            | $A_v = A_i Z_L / Z_i$                                                            |

|---------------------------------------------------------|----------------------------------------------------------------------------------|

| $Z_i = h_i + h_r A_1 Z_L = h_i - h_f h_r / (Y_L + h_o)$ | $A_{vs} = A_v Z_i / (Z_i + R_S) = A_i Z_L / (Z_i + R_S)$<br>= $A_{is} Z_L / R_S$ |

| $Y_o = h_o - h_f h_r / (R_S + h_i) = 1 / Z_o$           | $A_{is} = A_i R_S / (R_S + Z_i) = A_{vs} = A_{is} R_S / Z_L$                     |

# UNIT-II Transistor at high Frequency Response

#### **FREQUENCY RESPONSE OF AMPLIFIERS**

For any electronic circuit, the behavior of amplifiers is affected by the frequency of the signal on their input terminal. This characteristic is known as the **frequency response**.

Frequency response is one of the most important property of amplifiers. In the frequency range that amplifiers have been designed for, they must deliver a constant and acceptable level of gain. The frequency response depends directly on the components and the architecture chosen for the design of the amplifier.

Before defining in details the frequency response, we need to present the unit of decibel (dB) and the logarithmic scale related to it. When studying the frequency response, it is indeed more suitable to convert either the power or voltage gain into dB and to represent the frequency scale in a logarithmic (log) scale.

If we consider an amplifier with power gain  $A_P$  and voltage gain  $A_V$ , the power and voltage gain in dB are defined by:

$$A_P(dB) = 10 \log(A_P)$$

$$A_V(dB) = 20 \log(A_V)$$

While the gains in linear scale are always positive  $(A_P,A_V\geq 0)$ , their equivalent in dB can either be positive if an amplification is being realized  $(A_P,A_V>1)$  or negative if the input signal is attenuated  $(A_P,A_V<1)$ .

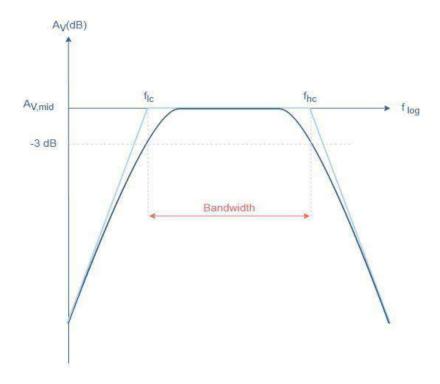

Often, it is not the gain  $A_V(dB)$  that is investigated but rather a normalized ratio  $A_V/A_{V,mid}(dB)=20log(A_V/A_{V,mid})$ . Where  $A_{V,mid}$  is called the **midrange gain** and represents the maximum gain of the amplifier in its frequency working range, for example 20 Hz - 20 kHz for an audio amplifier.

Therefore, when  $A_V = A_{V,mid}$ , the normalized gain (written indifferently  $A_V$ ) is  $A_V(dB) = 0$ . This sets a 0 dB reference when the gain is maximum. It is important to note that when the power is divided by two, we observe that  $A_P(dB) = 10 \log(0.5) = -3 dB$ .

The frequency at which the power drops to 50 % of its midrange value is known as the **cutoff frequency** and noted  $\mathbf{f}_c$ . Each time that the power is halved, a reduction of 3 dB of the normalized gain is observed. Therefore  $\mathbf{A}_P$ =-3 dB corresponds to  $\mathbf{A}_{V,mid}/\mathbf{2}$ ,  $\mathbf{A}_P$ =-6 dB corresponds to  $\mathbf{A}_{V,mid}/\mathbf{4}$  and so on ...

For this same frequency, the voltage (or current) is multiplied by a factor V2=0.7. Halving the voltage signal corresponds to a reduction of 6 dB and follows the same pattern as presented for the power gain.

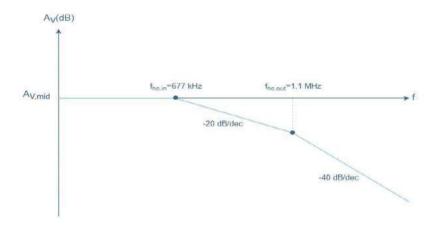

The most common tool used to represent the frequency response of any system is the **Bode plot**. It consists of the normalized gain  $A_V(dB)$  as a function of the frequency in log scale. A simplified Bode graph of an amplifier is shown in the **Figure 1** below:

Fig 1: Typical Bode graph of an amplifier

The light blue curve is called the asymptotic representation while the dark blue curve is the real frequency response of the circuit. In **Figure 1**, two different cutoff frequencies can be distinguished:  $\mathbf{f}_{lc}$  for "low cutoff" and  $\mathbf{f}_{hc}$  for "high cutoff". The quantity  $\mathbf{f}_{hc}$ - $\mathbf{f}_{lc}$  is called the **bandwidth** and represents the frequency range where the gain is above the -3 dB.

### **EFFECT OF THE CAPACITORS:**

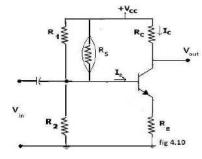

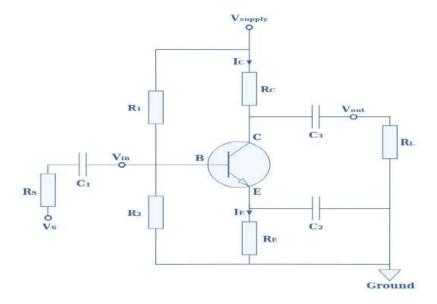

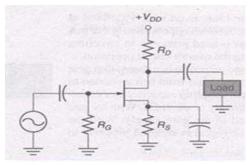

Let us consider a Common Emitter Amplifier (CEA) which configuration is shown in **Figure 2.** The structure around the BJT transistor consists of a voltage divider network ( $R_1$  and  $R_2$ ), a load ( $R_L$ ), coupling capacitors ( $C_1$  and  $C_3$ ) and a bypass capacitor  $C_2$ .

As capacitors have a property called **reactance** that is an equivalent of the resistance. The reactance  $(X_C)$  of capacitors depends on the frequency and the value of the capacitor, as in the below equation

$$X_C = \frac{1}{2\pi f C}$$

Fig 2: Common Emitter Amplifier

When the frequency is low,  $X_C$  tends to be high. Near DC signals, capacitors behave therefore as open circuits. On the other hand, when the frequency increases  $X_C$  tends to zero and capacitors act as short circuits.

At low input frequencies, the coupling capacitors will more likely block the signal, since  $X_{C1}$  and  $X_{C3}$  are higher, more voltage drop will be observed across  $C_1$  and  $C_3$ . This results in a lower voltage gain.

At high input frequencies the bypass capacitor  $C_2$  shortens the emitter branch to the ground and the voltage gain of the amplifier is  $A_V = (R_C//R_L)/r_e$  with  $r_e$  being the small diode emitter resistance. When the frequencies are lower, the resistance between the emitter and the ground is no longer only  $r_e$  but  $R_E + r_e$  and therefore the voltage gain decreases to  $A_V = (R_C//R_L)/(R_E + r_e)$ .

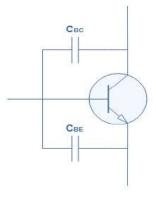

There is another type of capacitors that affect the frequency response of the amplifier and is not represented in **Figure 2**. They are known as **internal transistor capacitors** and represented in **Figure 3** below:

Fig 3: Internal transistor capacitors

Whereas the coupling and bypass capacitors act as **high-pass filter** (they block low frequencies), these internal capacitors behave differently. Indeed, if the frequency is low,  $C_{BC}$  and  $C_{BE}$  act as an open circuit and the transistor is not affected at all. However, if the frequency increases, more signal passes through them instead of going in the base branch of the transistor, therefore decreasing the voltage gain. The cutoff frequency of a RC filter:

$$f_c = \frac{1}{2\pi RC}$$

# **ANALYSIS AT LOW FREQUENCY**

First of all we consider the input high-pass filter  $R_{in}C_1$ . Where  $R_{in}$  is the total input impedance of the amplifier which can be expressed as:

$$R_{in}=R_S+(R_1//R_2//\beta R_E)$$

The low cutoff frequency of the input will therefore be:

$$f_{cl,in}=1/(2\pi R_{in}C_1)$$

The same procedure can be done for the output where the output resistance is

$$R_{out}=R_C//R_L$$

The low cutoff frequency of the output filter is:

$$f_{cl,out}=1/(2\pi R_{out}C_3)$$

Finally, for the bypass capacitor, the resistance formula is more complex and given by

$$R_{bypass}=R_E//((r_e+(R_S//\beta R_E)/\beta))$$

The low cutoff frequency of the bypass structure is thus:

$$f_{cl,bypass} = 1/(2\pi R_{bypass} C_2)$$

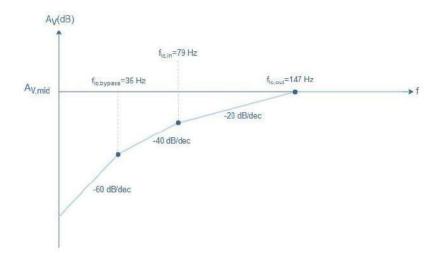

One last thing we need to understand before plotting the Bode graph is about the slope out of the midrange values. The decrease of  $A_{V,mid}$  with the frequency is called **roll-off** and its value for each simple RC filter is -20 dB/decade (dB/dec). This value means for high-pass filters (resp. low-pass filters) that each time the frequency is divided by 10 (resp. multiplied by 10), a decrease of -20 dB is observed for the gain of the amplifier.

When multiple filters are blocking the same range of frequencies, the roll-off is enhanced. In our example three filters are simultaneously blocking the frequencies below 35 Hz, the roll-off is therefore 3\*(-20 dB/dec)=-60 dB/dec.

Fig 4: Low frequency response of the CEA

## **ANALYSIS AT HIGH FREQUENCY**

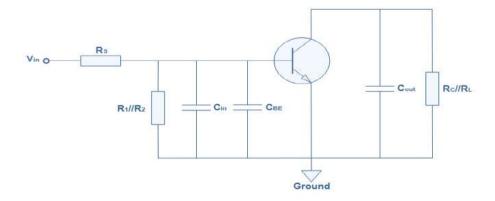

As stated previously, it is the internal transistor capacitors that will limit the gain at high frequencies acting as low-pass filters. It can be shown that the equivalent circuit of **Figure 2** at high frequency can be drawn such as presented in **Figure 5**:

Fig 5: Equivalent CEA at high frequency

We can note that the coupling capacitors are not represented since they behave as short circuits at high frequencies. Moreover, the emitter branch is shorten to the ground for the same reason applying to the bypass capacitor.

The internal capacitor  $C_{BC}$  is converted via **Miller's theorem** into the equivalent  $C_{in}$  and  $C_{out}$  capacitors. Moreover, this theorem states that

$$C_{in}=C_{BC}(A_{V,mid}+1)$$

and  $C_{out}=C_{BC}(A_{V,mid}+1)/A_{V,mid}$ .

The total input capacitance of this circuit is

$$C_{IN}=C_{BE}+C_{in}$$

;

The total input resistance is

$$R_{IN}=R_S//R_1//R_2//\beta r_e$$

.

The numerical application to our example gives

$$A_{V,mid}=(R_C//R_L)/r_e=108$$

,  $C_{IN}=575$  pF and  $R_{IN}=409$   $\Omega$ .

The high cutoff frequency of the input is therefore

$$f_{hc,in}=1/(2\pi R_{IN}C_{IN})=677 \text{ kHz}.$$

From the output point of view, the high cutoff frequency is simply given by the filter  $(R_C//R_L)C_{out}$  with  $C_{out}=5.3$  pF:  $f_{hc,out}=1/(2\pi(R_C//R_L)C_{out})=1.1$  MHz.

The information given here is summarized in a Bode plot representing the high frequency response of the CEA in asymptotic representation:

Fig 6: High frequency response of the CEA

By merging the two Bode graphs obtained for the low and high frequency responses in **Figure 4 and 6**, we can now plot the overall frequency response of the CEA configuration

Fig 7: Total frequency response of the CEA

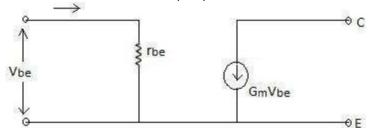

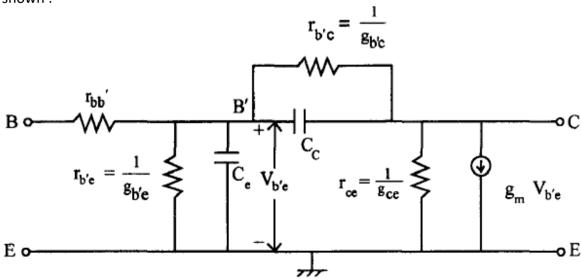

# Hybrid-pi (π) common emitter transistor model

For amplifier circuits Common Emitter configuration is preferred Because for Common Collector (hrc < 1). For Common Collector Configuration, voltage gain Av < 1. So even by cascading you can't increase voltage gain. For Common Base, current gain hib < 1. So overall voltage gain is < 1. But for Common Emitter, hre» 1. Therefore Voltage gain can be increased by cascading Common Emitter stage. So Common Emitter configuration is widely used.

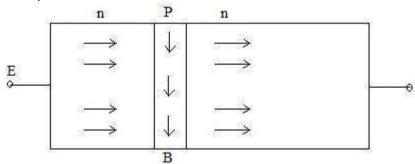

Under reverse bias condition the capacitance at the junction is called transition or space charge capacitance. Under forward bias condition the capacitance is called diffusion or storage capacitance. At high frequencies, BJT cannot be analysed by h-parameters.

### Giacolleto model - hybrid $\pi$ equivalent circuit

Desirable features of hybrid  $\pi$  equivalent circuit are:

- (1) The value of components in the equivalent circuit are independent of frequencies.

- (2) The values of all the resistive components in the equivalent circuit can be determined from the known or Specified values of h-parameters at low frequencies.

- (3) The results obtained by using this equivalent circuit agrees with the experimental result.

The components of the equivalent circuit exist in the form of  $\pi$  hence the name.

For small signal behaviour the transistor at its input port behaves as a resistor.

The output port is a dependent current source.

Because the base (B) is lightly doped all the depletion region lies entirely in the Base region. So, when the collector voltage is increased the depletion region in the base increases.

rce --> This resistance is added to compensate for the change in IC due to change in VCE.

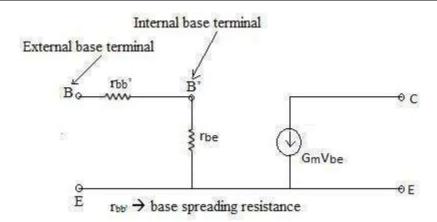

The Hybrid- $\pi$  or  $Giacoletto\ Model$  for the Common Emitter amplifier circuit (single stage) is as shown:

Fig 8 : Hybrid- $\pi$  CE BJT Model

Analysis of this circuit gives satisfactory results at *all* frequencies not only at *high* frequencies but also at *low frequencies*. All the parameters are assumed to be independent of frequency.

# **Circuit Components**

B' is the internal node of the base of the Transconductance amplifier. It is not physically accessible.

The base spreading resistance rb'b is represented as a *lumped* parameter between base B and internal node B'.  $(g_m V_{b'e})$  is a current generator. Vb'e is the input voltage across the emitter junction. If  $V_{b'e}$  increases, more carriers are injected into the base of the transistor. So the increase in the number of carriers is  $\alpha V_{b'e}$ ). This results in small signal current (since we are taking into account changes in  $V_{b'e}$ ). This effect is represented by the current generator  $g_m V_{b'e}$ . This represents the current that results because of changes in  $V_{b'e}$  when C is shorted to E.

When the number of carriers injected into the base increase, base recombination also increases. So this effect is taken care of by  $g_{\rm b'e}$ . As recombination increases, base current increases. Minority carrier storage in the base is represented by  $c_e$  the diffusion capacitance.

According to Early Effect, the change in voltage between Collector and Emitter changes the base width. So base width will be modulated according to the voltage between Collector and Emitter. When base width changes, the minority carrier concentration in base changes. Hence the current which is proportional to carrier concentration also changes. So  $I_E$  changes and hence  $I_C$  changes. This feedback effect [ $I_E$  on input side,  $I_C$  on output side] is taken into account by connecting  $g_{bF_C}$  between B', and C. The conductance between Collector and Base is  $g_{ce}$ .  $C_C$  represents the collector junction barrier capacitance.

The High frequency model parameters of a BJT in terms of low frequency hybrid parameters is given below

- Tran conductance  $g_m = I_C/V_T$

- Internal Base node to emitter resistance  $r_{bFe} = h_{fe}/g_m = (h_{fe}*V_T)/I_C$

- Internal Base node to collector resistance  $r_{bF_c} = (h_{re} r_{bF_e}) / (1 h_{re})$  assuming hre << 1 it reduces to  $r_{bF_c} = (h_{re} r_{bF_e})$

- Base spreading resistance  $r_{bbF} = h_{ie} r_{bFe} = h_{ie} (h_{fe} * Vt) / Ic$

- Collector to emitter resistance  $r_{ce} = 1 / (h_{oe} (1 + h_{fe}) / r_{bF_c})$

## Variation of Hybrid Parameters with $|I_C|$ , $|V_{CE}|$ and T

1) Transconductance Amplifier or Mutual Conductance (gm):

$$g_m = I_C/V_T$$

$g_m$  is  $\alpha I_C$

$V_T = T/||.600$

Therefore  $g_m \propto 1/T$

$g_m$  is independent of  $V_{\it CE}$ Since in the active region of the transconductance, Ic is independent of  $V_{\it CE}$

#### **UNIT II-II**

FET Amplifiers: Analysis of Common Source and Common Drain JFET Amplifiers, Comparison of performance with BJT Amplifiers.

#### **BIASING FET:-**

For the proper functioning of a linear FET amplifier, it is necessary to maintain the operating point Q stable in the central portion of the pinch off region The Q point should be independent of device parameter variations and ambient temperature variations

This can be achieved by suitably selecting the gate to source voltage VGS and drain current ID which is referred to as biasing

JFET biasing circuits are very similar to BJT biasing circuits The main difference between JFET circuits and BJT circuits is the operation of the active components themselves

There are mainly two types of Biasing circuits

- 1) Self bias

- 2) Voltage divider-bias.

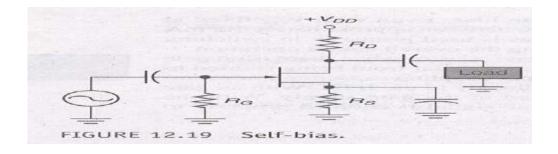

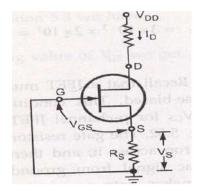

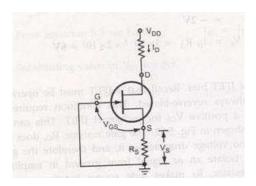

#### **SELFBIAS**

Self bias is a JFET biasing circuit that uses a source resistor to help reverse bias the JFET gate. A self bias circuit is shown in the fig. Self bias is the most common type of JFET bias. This JFET must be operated such that gate source junction is always reverse biased. This condition requires a negative VGS for an N channel JFET and a positive VGS for P channel JFET. This can be achieved using the self bias arrangement as shown in Fig. The gate resistor RG doesn't affect the bias because it has essentially no voltage drop across it, and: the gate remains at 0V .RG is necessary only to isolate an ac signal from ground in amplifier applications. The voltage drop across resistor RS makes gate source junction reverse biased.

For the dc analysis coupling capacitors are open circuits.

For the N channel FET in Fig (a)

IS produces a voltage drop across RS and makes the source positive w.r.t ground. In any JFET circuit all the source current passes through the device to the drain circuit . This is due to the fact that there is no significant gate current.

We can define source current as IS = ID

(VG =0 because there is no gate current flowing in RG So VG across RG is zero)

### DC analysis of self Bias:-

In the following DC analysis, the N channel J FET shown in the fig. is used for illustration.

For DC analysis we can replace coupling capacitors by open circuits and we can also replace the resistor RG by a short circuit equivalent... IG = 0.The relation between ID and VGS is given by

Id=Idss

$$[1-\frac{Vgs}{Vp}]^2$$

VGS for N channel JFET is =-idRs

Substuting this value in the above equation

$$Id=Idss[1-\frac{(-IdRs)}{Vp}]^2$$

$$Id=Idss[1+\frac{(IdRs)}{Vp}]^2$$

For the N-chanel FET in the above figure

Is produces a voltage drop across Rs and makes the source positive w.r.t ground in any JFET circuit all the source current passes through the device to drain circuit this is due to the fact that there is no significant gate current. Therefore we can define source current as Is=Id and Vg=0 then

Vs= Is Rs =IdRs

Vgs=Vg-Vs=0-IdRs=-IdRs

# Drawing the self bias line:-

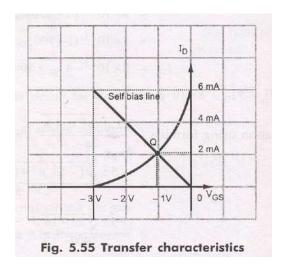

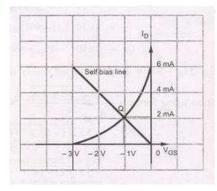

Typical transfer characteristics for a self biased JFET are shown in the fig.

The maximum drain current is 5mA and the gate source cut off voltage is -3V. This means the gate voltage has to be between 0 and -3V.

Now using the equation VGS = -IDRS and assuming RS of any suitable value we can draw the self bias line.

Let us assume RS =  $500\Omega$

With this Rs , we can plot two points corresponding to ID = 0 and Id = IDSS

for ID =0

VGS = -IDRS

$VGS = 0X (500.\Omega) = 0V$

So the first point is (0,0)

(I<sub>d</sub>, VGS)

For ID= IDSS=5mA

VGS = (-5mA) (500 Ω) = -3V

So the 2<sup>nd</sup> Point will be (5mA,-3V)

By plotting these two points, we can draw the straight line through the points. This line will intersect the transconductance curve and it is known as self bias line. The intersection point gives the operating point of the self bias JFET for the circuit.

At Q point, the ID is slightly > than 2mA and VGS is slightly > -1V. The Q point for the self bias JFET depends on the value of Rs.If Rs is large, Q point far down on the transconductance curve, ID is small, when Rs is small Q point is far up on the curve, ID is large.

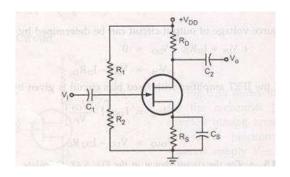

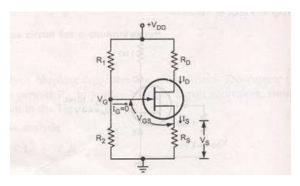

#### **VOLTAGE DIVIDERBIAS:-**

The fig. shows N channel JFET with voltage divider bias. The voltage at the source of JFET must be more positive than the voltage at the gate in order to keep the gate to source junction reverse biased. The source voltage is

The gate voltage is set by resistors R1 and R2 as expressed by the following equation using the voltage divider formula.

$$Vg = \left(\frac{R2}{(R1+R2)}\right)Vdd$$

For dc analysis

# Applying KVL to the input circuit

:: VGS = VG-Vs=VG-ISRS

VGS=VG-IDRS :: IS =ID

Applying KVL to the input circuit we get

VDS+IDRD+VS-VDD =0

::VDS = VDD-IDRD-IDRS

VDS = VDD-ID (RD +RS)

The Q point of a JFET amplifier, using the voltage divider bias is

IDQ = IDSS[1-VGS/VP]2

VDSQ = VDD-ID (RD+RS)

### **COMPARISON OF MOSFET WITH JFET**

- a. In enhancement and depletion types of MOSFET, the transverse electric field induced across an insulating layer deposited on the semiconductor material controls the conductivity of thechannel.

- b. In the JFET the transverse electric field across the reverse biased PN junction controls the conductivity of thechannel.

- c. The gate leakage current in a MOSFET is of the order of  $10^{-12}$ A. Hence the input resistance of a MOSFET is very high in the order of  $10^{10}$  to  $10^{15}$   $\Omega$ . The gate leakage current of a JFET is of the order of  $10^{-9}$ A., and its input resistance is of the order of  $10^{8}$  $\Omega$ .

- d. TheoutputcharacteristicsoftheJFETareflatterthanthoseoftheMOSFET, and hence the drain resistance of a JFET (0.1 to  $1M\Omega$ ) is much higher than that of a MOSFET (1 to  $50k\Omega$ ).

- e. JFETs are operated only in the depletion mode. The depletion type MOSFET may be operated in both depletion and enhancementmode.

- f. Comparing to JFET, MOSFETs are easier tofabricate.

- g. Special digital CMOS circuits are available which involve near zero power dissipation and very low voltage and current requirements. This makes them suitable for portable systems.

### **FET AMPLIFIERS**

#### INTRODUCTION

Field Effect Transistor (FET) amplifiers provide an excellent voltage gain and high input impedence. Because of high input impedence and other characteristics of JFETs they are preferred over BJTs for certain types of applications.

There are 3 basic FET circuit configurations:

- i) Common Source

- ii)Common Drain

- iii)Common Gain

Similar to BJT CE,CC and CB circuits, only difference is in BJT large output collector current is controlled by small input basecurrent whereas FET controls output current by means of small input voltage. In both the cases output current is controlled variable.

FET amplifier circuits use voltage controlled nature of the JFET. In Pinch off region,  $I_D$  depends only on  $V_{GS}$ .

# Common Source (CS)Amplifier

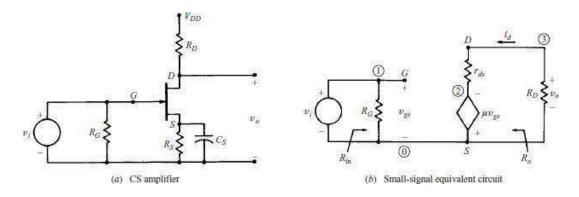

Fig. 5.1 (a) CS Amplifier (b) Small-signal equivalent circuit

A simple Common Source amplifier is shown in Fig. 5.1(a) and associated small signal equivalent circuit using voltage-source model of FET is shown in Fig. 5.1(b)

### **Voltage Gain**

Source resistance (R<sub>S</sub>) is used to set the Q-Point but is bypassed by C<sub>S</sub> for mid-frequency operation.

From the small signal equivalent circuit, the output voltage

$$V_O = -R_D \mu V_{gs} (R_D + r_d)$$

Where  $V_{gs} = V_i$ , the input voltage,

Hence, the voltage gain,

$$A_V = V_O / V_i = -R_D \mu (R_D + r_d)$$

# **Input Impedence**

From Fig. 5.1(b) Input Impedence is

$$Z_{i} = R_{G}$$

For voltage divider bias as in CE Amplifiers of BJT

$$R_G = R_1 \parallel R_2$$

### **Output Impedance**

Output impedance is the impedance measured at the output terminals with the input voltage  $V_1 = 0$ From the Fig. 5.1(b) when the input voltage  $V_i = 0$ ,  $V_{gs} = 0$  and hence

$$\mu V_{gs} = 0$$

The equivalent circuit for calculating output impedence is given in Fig. 5.2.

Output impedence  $Z_0 = r_d \| R_D$

Normally  $r_d$  will be far greater than  $R_D$ . Hence  $Z_o \approx R_D$

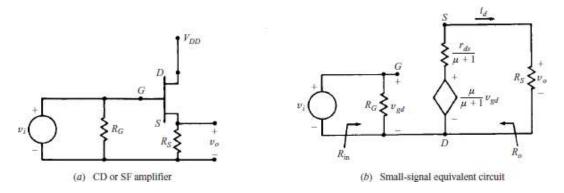

# Common DrainAmplifier

A simple common drain amplifier is shown in Fig. 5.2(a) and associated small signal equivalent circuit using the voltage source model of FET is shown in Fig. 5.2(b). Since voltage  $V_{gd}$  is more easily determined than  $V_{gs}$ , the voltage source in the output circuit is expressed in terms of  $V_{gs}$  and Thevenin's theorem.

Fig. 5.2 (a)CD Amplifier (b)Small-signal equivalent circuit

The output voltage,

$$V_0 = R_S \mu V_{gd} / (\mu + 1) R_S + r_d$$

Where  $V_{gd} = V_i$  the input voltage.

Hence, the voltage gain,

$$A_v = V_O / V_i = R_S \mu / (\mu + 1) R_S + r_d$$

# **Input Impedence**

From Fig. 5.2(b), Input Impedence  $Z_i = R_G$

### **Output Impedence**

From Fig. 5.2(b), Output impedence measured at the output terminals with input voltage  $V_i = 0$  can be calculated from the following equivalent circuit.

As

$$V_i = 0$$

:  $V_{gd} = 0$ :  $\mu V_{gd} / (\mu + 1) = 0$

**Output Impedence**

$$Z_0 = r_d / (\mu + 1) \| R_S$$

When  $\mu \gg 1$

$$Z_{O} = (r_{d} / \mu) \| R_{S} = (1/g_{m}) \| R_{S}$$

### **BIASING FET**

For the proper functioning of a linear FET amplifier, it is necessary to maintain the operating point Q stable in the central portion of the pinch off region The Q point should be independent of device parameter variations and ambient temperature variations

This can be achieved by suitably selecting the gate to source voltage VGS and drain current ID which is referred to as biasing

JFET biasing circuits are very similar to BJT biasing circuitsThe main difference between JFET circuits and BJT circuits is the operation of the active components themselves

There are mainly two types of Biasing circuits

- 1. Selfbias

- 2. Voltage dividerbias.

#### 5.13.1. SELF BIAS:-

Self bias is a JFET biasing circuit that uses a source resistor to help reverse bias the JFET gate.

# A self bias circuit is shown in the fig 5.3

Self bias is the most common type of JFET bias.

This JFET must be operated such that gate source junction is always reverse biased.

This condition requires a negative VGS for an N channel JFET and a positive VGS for P channel JFET.

This can be achieved using the self bias arrangement as shown in Fig 5.3.

The gate resistor RG doesn't affect the bias because it has essentially no voltage drop across it, and :

the gate remains at OV .RG is necessary only to isolate an ac signal from ground in amplifier applications.

The voltage drop across resistor RS makes gate source junction reverse biased.

## DC analysis of self Bias:-

In the following DC analysis, the N channel J FET shown in the fig5.4. is used for illustration.

ForDCanalysiswecanreplacecouplingcapacitors by open circuits and resistor RG by a short circuit equivalent.

we canalsoreplace

the

resistor no by a short circuitequivalent

The relation between ID and VGS is given by

$$Id=Idss[1-\frac{Vgs}{Vp}]^2$$

VGS for N channel JFET is =-id Rs

Substuting this value in the above equation

$$Id=Idss[1-\frac{(-IdRs)}{Vp}]^2$$

$$Id=Idss[1+\frac{(IdRs)}{V_{m}}]^{2}$$

For the N-chanel FET in the above figure

Is produces a voltage drop across Rs and makes the source positive w.r.t ground

in any JFET circuit all the source current passes through the device to drain circuit this is due to the fact that there is no significant gate current

therefore we can define source current as Is=Id and Vg=0 then

Vs= Is Rs =IdRs

Vgs=Vg-Vs=0-IdRs=-IdRs

# Drawing the self bias line:-

Typical transfer characteristics for a self biased JFET are shown in the figure 5.5 below:

The maximum drain current is 6mA and the gate source cut off voltage is -3V. This means the gate voltage has to be between 0 and -3V.

Now using the equation VGS = -IDRS and assuming RS of any suitable value we can draw the self bias line.

Let us assume RS =  $500\Omega$

With this Rs, we can plot two points corresponding to ID = 0 and Id = IDSS

for

$$ID = 0$$

$$VGS = 0X (500.\Omega) = 0V$$

So the first point is (0,0)

(I<sub>d</sub>, VGS)

For ID= IDSS=6mA

VGS = (-6mA) (500 Ω) = -3V

So the 2<sup>nd</sup> Point will be (6mA,-3V)

By plotting these two points, we can draw the straight line through the points. This line will intersect the transconductance curve and it is known as self bias line. The intersection point gives the operating point of the self bias JFET for the circuit.

At Q point, the ID is slightly > than 2mA and VGS is slightly > -1V. The Q point for the self bias JFET depends on the value of Rs.If Rs is large, Q point far down on the transconductance curve, ID is small, when Rs is small Q point is far up on the curve, ID is large.

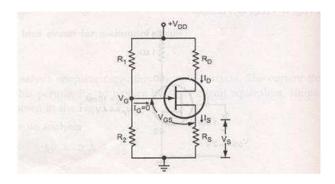

#### **5.13.2 VOLTAGE DIVIDER BIAS:-**

The fig5.6 shows N channel JFET with voltage divider bias. The voltage at the source of JFET must be more positive than the voltage at the gate in order to keep the gate to source junction reverse biased. The source voltage is

VS = IDRS

The gate voltage is set by resistors R1 and R2 as expressed by the following equation using the voltage divider formula.

$$Vg = V_{(R1+R2)}^{R2}$$

# For dc analysis fig 5.5

# Applying KVL to the input circuit

VG-VGS-VS =0

:: VGS = VG-Vs=VG-ISRS

VGS=VG-IDRS :: IS =ID

Applying KVL to the input circuit we get

VDS+IDRD+VS-VDD =0

::VDS = VDD-IDRD-IDRS

VDS = VDD-ID (RD +RS)

The Q point of a JFET amplifier , using the voltage divider bias is

IDQ = IDSS[1-VGS/VP]2

VDSQ = VDD-ID (RD+RS)

# UNIT III

# **Number System and Boolean Algebra**

If base or radix of a number system is 'r', then the numbers present in that number system are ranging from zero to r-1. The total numbers present in that number system is 'r'. So, we will get various number systems, by choosing the values of radix as greater than or equal to two.

In this chapter, let us discuss about the **popular number systems** and how to represent a number in the respective number system. The following number systems are the most commonly used.

- Decimal Number system

- Binary Number system

- Octal Number system

- Hexadecimal Number system

# Decimal Number System

The **base** or radix of Decimal number system is **10**. So, the numbers ranging from 0 to 9 are used in this number system. The part of the number that lies to the left of the **decimal point** known as integer part. Similarly, the part of the number that lies to the right of the decimal point is known as fractional part.

In this number system, the successive positions to the left of the decimal point having weights of  $10^{0}$ ,  $10^{1}$ ,  $10^{2}$ ,  $10^{3}$  and so on. Similarly, the successive positions to the right of the decimal point having weights of  $10^{-1}$ ,  $10^{-2}$ ,  $10^{-3}$  and so on. That means, each position has specific weight, which is **power of base 10**

### Example

Consider the **decimal number 1358.246**. Integer part of this number is 1358 and fractional part of this number is 0.246. The digits 8, 5, 3 and 1 have weights of 100, 101,  $10^2$  and  $10^3$  respectively. Similarly, the digits 2, 4 and 6 have weights of  $10^{-1}$ ,  $10^{-2}$  and  $10^{-3}$  respectively.

### Mathematically, we can write it as

$$1358.246 = (1 \times 10^{3}) + (3 \times 10^{2}) + (5 \times 10^{1}) + (8 \times 10^{0}) + (2 \times 10^{-1}) + (4 \times 10^{-2}) + (6 \times 10^{-3})$$

After simplifying the right hand side terms, we will get the decimal number, which is on left hand side.

### **Binary Number System**

All digital circuits and systems use this binary number system. The **base** or radix of this number system is **2**. So, the numbers 0 and 1 are used in this number system.

The part of the number, which lies to the left of the **binary point** is known as integer part. Similarly, the part of the number, which lies to the right of the binary point is known as fractional part.

In this number system, the successive positions to the left of the binary point having weights of  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$  and so on. Similarly, the successive positions to the right of the binary point having weights of  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$  and so on. That means, each position has specific weight, which is **power of base 2**.

# Example

Consider the **binary number 1101.011**. Integer part of this number is 1101 and fractional part of this number is 0.011. The digits 1, 0, 1 and 1 of integer part have weights of  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$  respectively. Similarly, the digits 0, 1 and 1 of fractional part have weights of  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$  respectively.

# Mathematically, we can write it as

$$1101.011 = (1 \times 2^{3}) + (1 \times 2^{2}) + (0 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3})$$

After simplifying the right hand side terms, we will get a decimal number, which is an equivalent of binary number on left hand side.

### Octal Number System

The **base** or radix of octal number system is **8**. So, the numbers ranging from 0 to 7 are used in this number system. The part of the number that lies to the left of the **octal point** is known as integer part. Similarly, the part of the number that lies to the right of the octal point is known as fractional part.

In this number system, the successive positions to the left of the octal point having weights of  $8^0$ ,  $8^1$ ,  $8^2$ ,  $8^3$  and so on. Similarly, the successive positions to the right of the octal point having weights of  $8^{-1}$ ,  $8^{-2}$ ,  $8^{-3}$  and so on. That means, each position has specific weight, which is **power of base 8**.

### Example

Consider the **octal number 1457.236**. Integer part of this number is 1457 and fractional part of this number is 0.236. The digits 7, 5, 4 and 1 have weights of  $8^0$ ,  $8^1$ ,  $8^2$  and  $8^3$  respectively. Similarly, the digits 2, 3 and 6 have weights of  $8^{-1}$ ,  $8^{-2}$ ,  $8^{-3}$  respectively.

### Mathematically, we can write it as

$$1457.236 = (1 \times 8^3) + (4 \times 8^2) + (5 \times 8^1) + (7 \times 8^0) + (2 \times 8^{-1}) + (3 \times 8^{-2}) + (6 \times 8^{-3})$$

After simplifying the right hand side terms, we will get a decimal number, which is an equivalent of octal number on left hand side.

#### Hexadecimal Number System

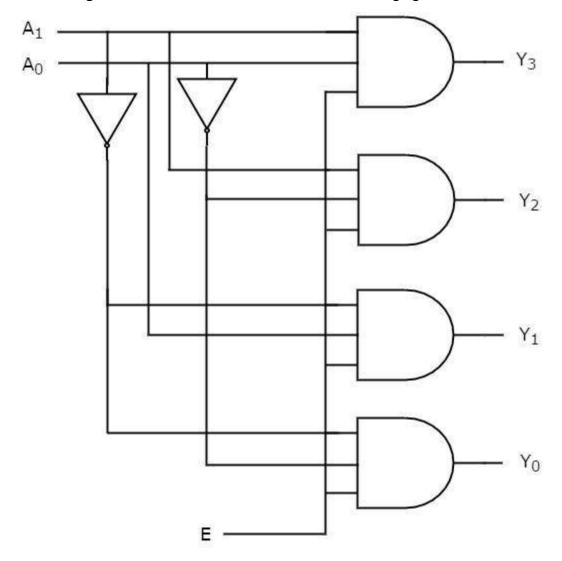

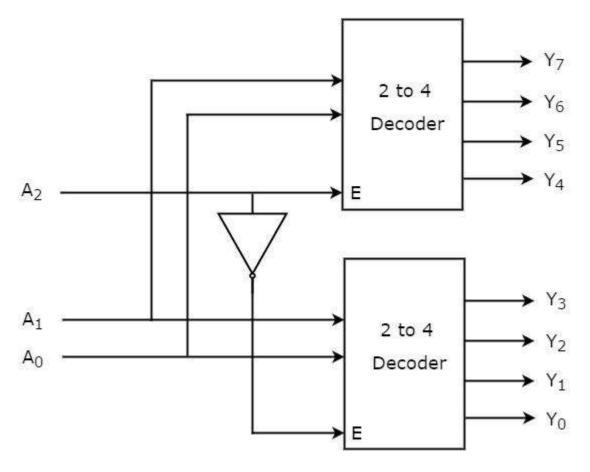

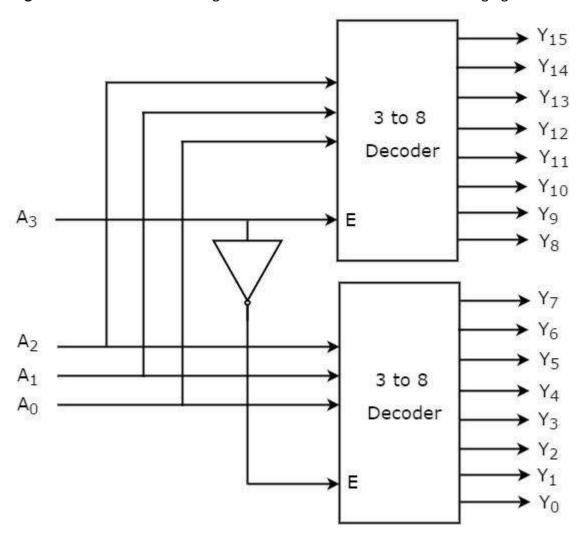

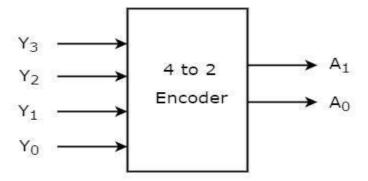

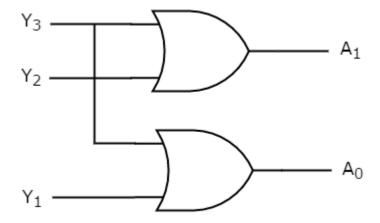

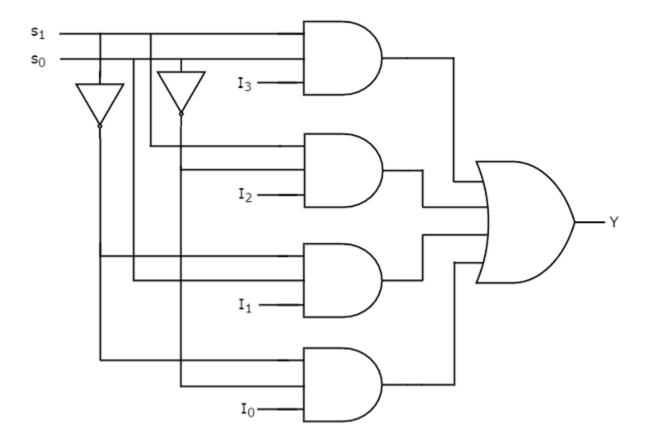

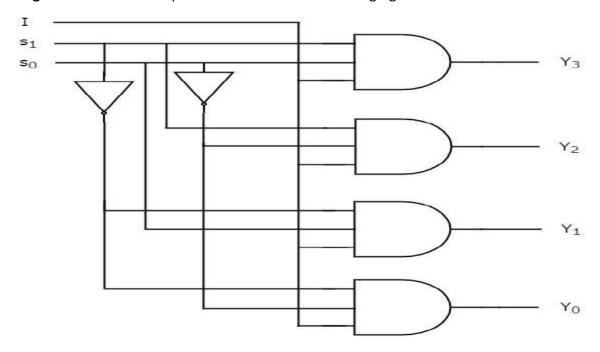

The **base** or radix of Hexa-decimal number system is **16**. So, the numbers ranging from 0 to 9 and the letters from A to F are used in this number system. The decimal equivalent of Hexa-decimal digits from A to F are 10 to 15.