# MALLA REDDY COLLEGE OF ENGINEERING & TECHNOLOGY

(AUTONOMOUS INSTITUTION - UGC, GOVT.OF INDIA)

Affiliated to JNTUH; Approved by AICTE, NBA-Tier 1 & NAAC with A-GRADE I ISO 9001:2015 Maisammaguda, Dhulapally, Komaplly, Secunderabad - 500100, Telangana State, India

## LECTURE NOTES

# ANALOG & DIGITAL ELECTRONICS

2021-22 (R20)

B.TECH I YEAR R-20

## MALLA REDDY COLLEGE OF ENGINEERING AND TECHNOLOGY

I Year B. TECH L/T/P/C

3/-/-/3

## (R20A0401) ANALOG & DIGITAL ELECTRONICS

#### **COURSE OBJECTIVES:**

The main objectives of the course are:

- 1. To familiarize with the principal of operation, analysis and design of pn junction diode.

- 2. To study the construction of BJT and its characteristics in different configurations.

- 3. To study the construction and characteristics of JFET and MOSFET.

- 4. To study basic number systems codes and logical gates.

- 5. To introduce the methods for simplifying Boolean expressions and design of combinational circuits.

#### UNIT-I

**P-N Junction diode:** Qualitative Theory of P-N Junction, P-N Junction as a diode, diode equation, volt-ampere characteristics, temperature dependence of V-I characteristics, ideal versus practical, diode equivalent circuits, Zener diode characteristics.

#### **UNIT-II**

**Bipolar Junction Transistor:** The Junction transistor, Transistor construction, Transistor current components, Transistor as an amplifier, Input and Output characteristics of transistor in Common Base, Common Emitter, and Common collector configurations.  $\alpha$  and  $\beta$  Parameters and the relation between them, BJT Specifications.

## **UNIT-III**

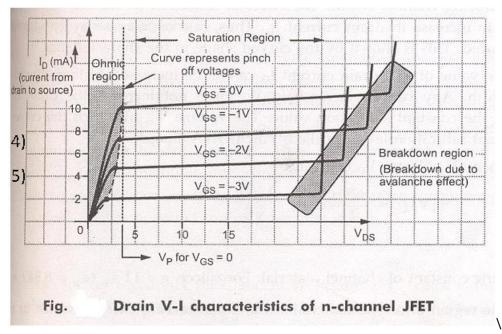

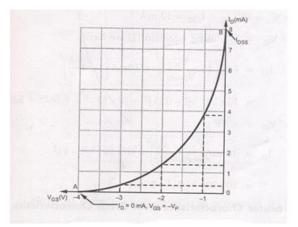

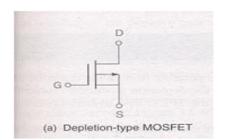

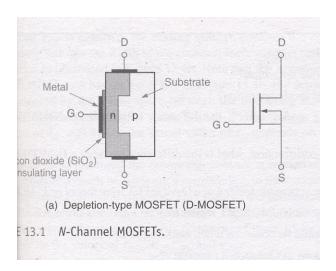

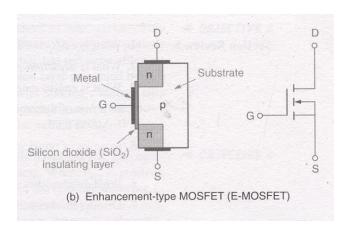

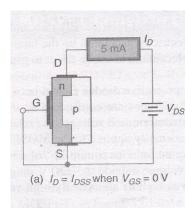

**FIELD EFFECT TRANSISTOR:** JFET-Construction, principle of Operation, Volt—Ampere characteristics, Pinch- off voltage. Small signal model of JFET. FET as Voltage Variable Resistor, Comparison of BJT and FET. MOSFET- Construction, Principle of Operation and symbol, MOSFET characteristics in Enhancement and Depletion modes.

#### **UNIT IV:**

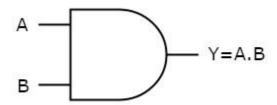

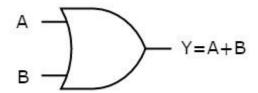

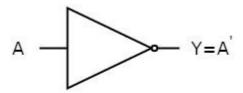

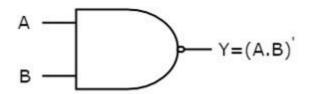

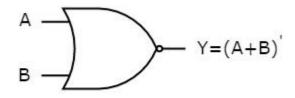

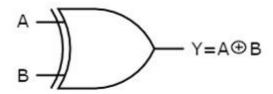

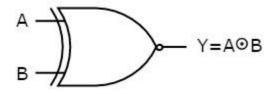

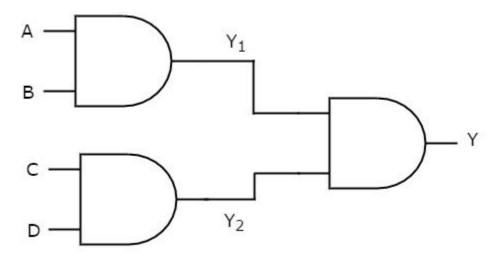

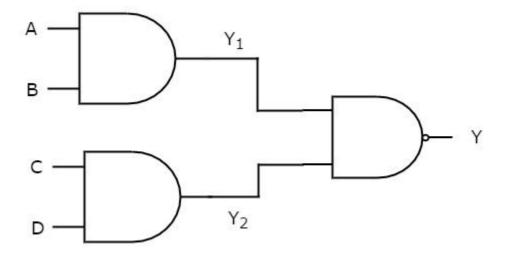

**Number System and Boolean Algebra:** Number Systems, Base Conversion Methods, Complements of Numbers, Codes- Binary Codes, Binary Coded Decimal, Unit Distance Code, Digital Logic Gates (AND, NAND, OR, NOR, EX-OR, EX-NOR), Properties of XOR Gates, Universal Gates, Basic Theorems and Properties, Switching Functions, Canonical and Standard Form.

#### **UNIT-V**

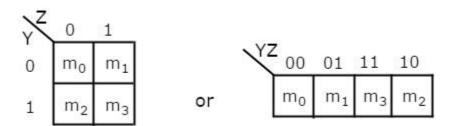

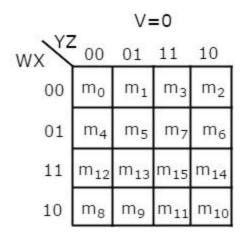

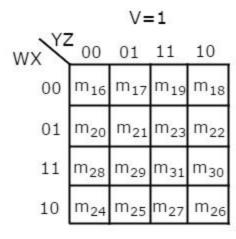

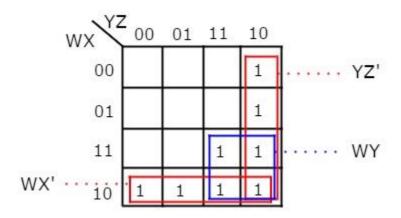

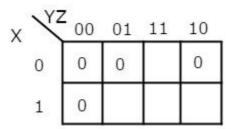

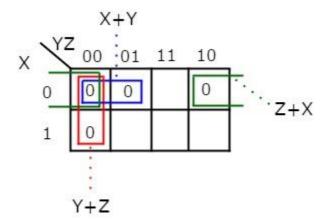

**Minimization Techniques:** The Karnaugh Map Method, Three, Four and Five Variable Maps, Prime and Essential Implications, Don't Care Map Entries, Using the Maps for Simplifying, Multilevel NAND/NOR realizations.

B.TECH I YEAR R-20

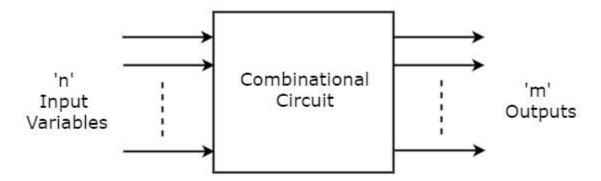

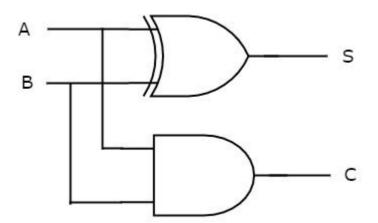

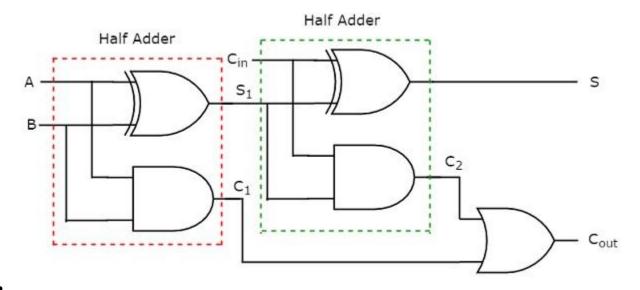

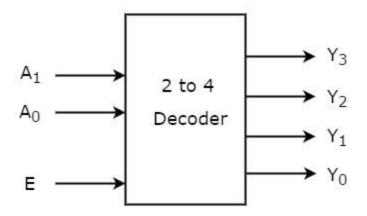

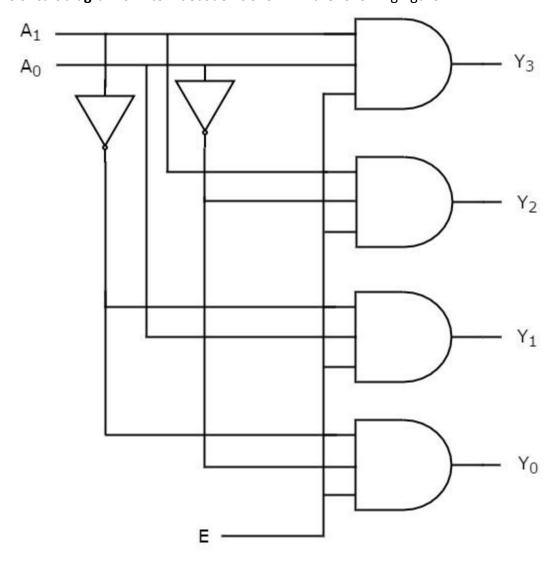

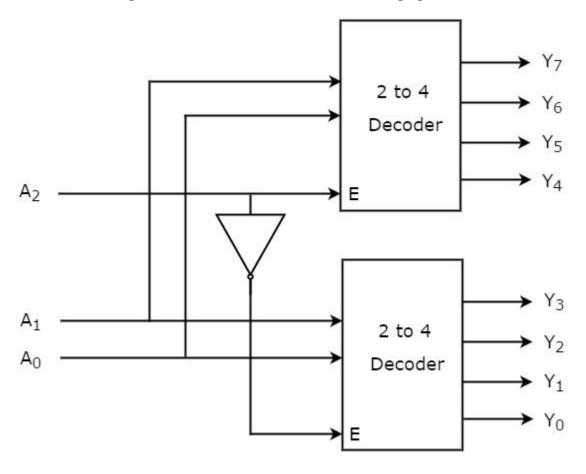

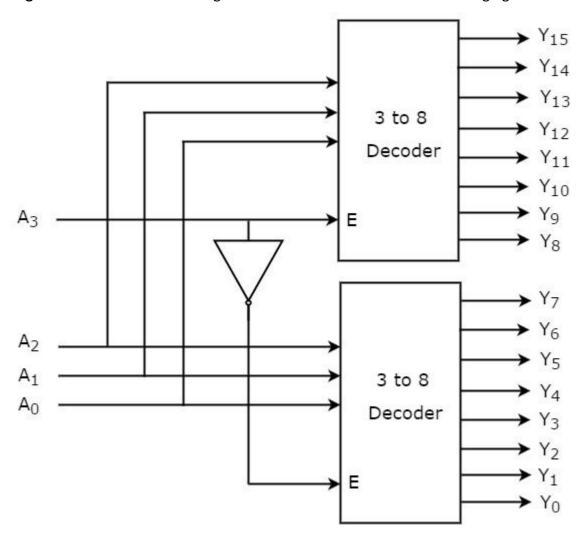

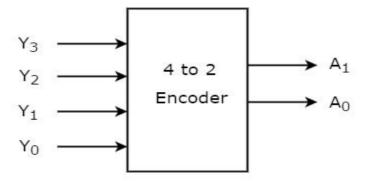

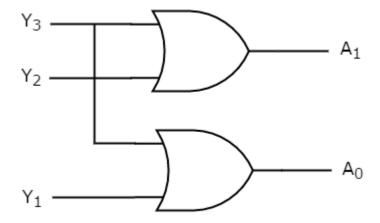

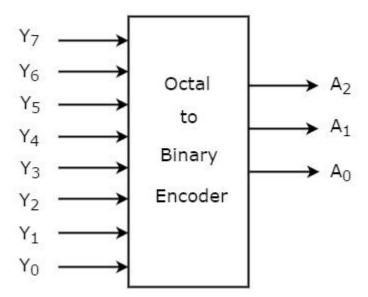

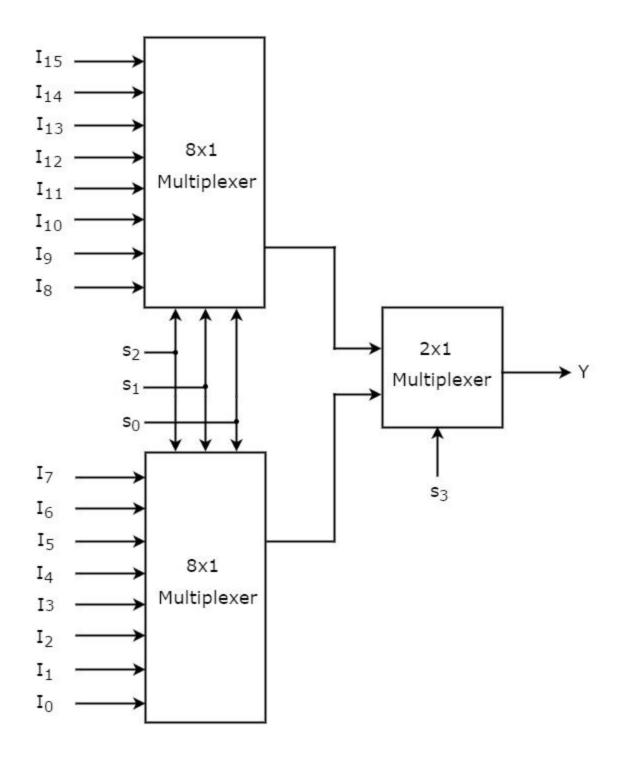

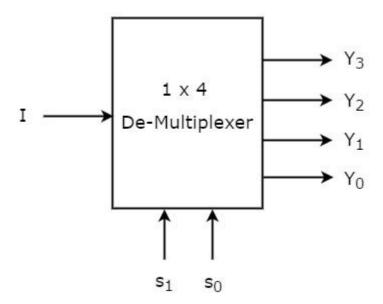

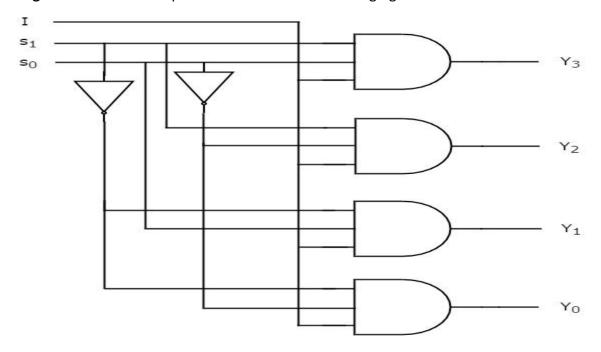

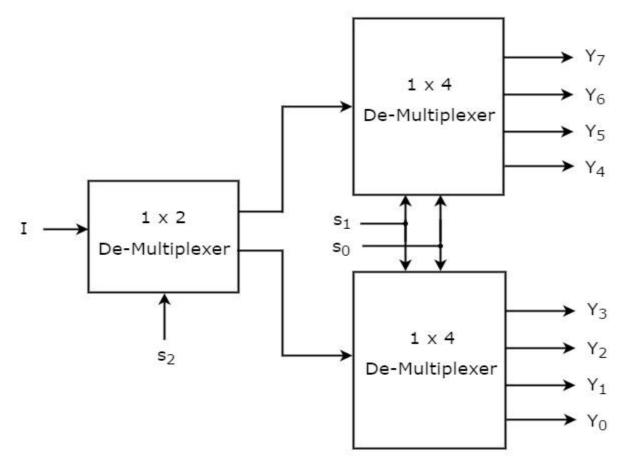

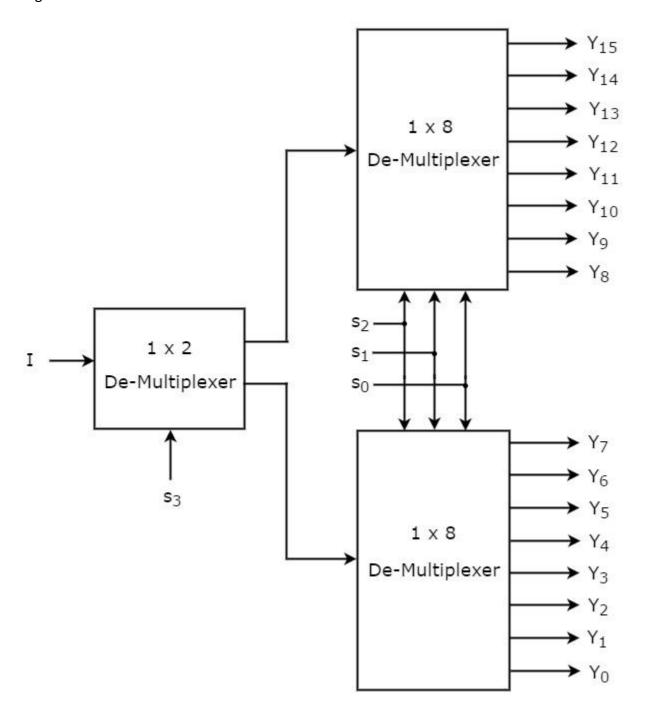

**Combinational Circuits:** Design procedure – Half adder, Full Adder, Half subtractor, Full subtractor, Multiplexer/Demultiplexer, decoder, encoder, Code converters, Magnitude Comparator.

#### **TEXT BOOKS:**

- 1. Integrated Electronics Analog Digital Circuits, Jacob Millman and D. Halkias, McGrawHill.

- 2. Electronic Devices and Circuits, S.Salivahanan, N.Sureshkumar, McGrawHill.

- 3. M. Morris Mano, Digital Design, 3rd Edition, Prentice Hall of India Pvt. Ltd., 2003

## **REFERENCE BOOKS:**

- 1. Electronic Devices and Circuits, K. Lal Kishore B. SPublications

- 2. Electronic Devices and Circuits, G.S.N. Raju, I.K. International Publications, New Delhi, 2006.

- 3. John F. Wakerly, Digital Design, Fourth Edition, Pearson/PHI, 2006

- 4. John.M Yarbrough, Digital Logic Applications and Design, Thomson Learning, 2002.

- 5. Charles H.Roth. Fundamentals of Logic Design, Thomson Learning, 2003.

## **COURSE OUTCOMES:**

After completion of the course, the student will be able to:

- 1. Understand the principal of operation, analysis and design of pn junction diode.

- 2. Understand the construction of BJT and its characteristics in different configurations.

- 3. Understand the construction and characteristics of JFET and MOSFET.

- 4. Understand basic number systems codes and logical gates.

- 5. Understand the methods for simplifying Boolean expressions and design of combinational circuits

B.TECH I YEAR R-20

## **PROGRAM OUTCOMES (POs)**

## **Engineering Graduates will be able to:**

1. **Engineering knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- 2. **Problem analysis**: Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

- 3. **Design / development of solutions**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

- 4. **Conduct investigations of complex problems**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- 5. **Modern tool usage**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

- 6. **The engineer and society**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- 7. **Environment and sustainability**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- 8. **Ethics**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- 9. **Individual and team work**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- 10. Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

- 11. **Project management and finance**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multi disciplinary environments.

- 12. Life- long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

## UNIT-I

## PN JUNCTION DIODE

#### 1.0 INTRODUCTON

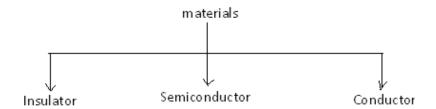

Based on the electrical conductivity all the materials in nature are classified as insulators, semiconductors, and conductors.

**Insulator**: An insulator is a material that offers a very low level (or negligible) of conductivity when voltage is applied. Eg: Paper, Mica, glass, quartz. Typical resistivity level of an insulator is of the order of  $10^{10}$  to  $10^{12}$   $\Omega$ -cm. The energy band structure of an insulator is shown in the fig.1.1. Band structure of a material defines the band of energy levels that an electron can occupy. Valance band is the range of electron energy where the electron remain bended too the atom and do not contribute to the electric current. Conduction bend is the range of electron energies higher than valance band where electrons are free to accelerate under the influence of external voltage source resulting in the flow of charge.

The energy band between the valance band and conduction band is called as forbidden band gap. It is the energy required by an electron to move from balance band to conduction band i.e. the energy required for a valance electron to become a free electron.

$$1 \text{ eV} = 1.6 \times 10^{-19} \text{ J}$$

For an insulator, as shown in the fig.1.1 there is a large forbidden band gap of greater than 5Ev. Because of this large gap there a very few electrons in the CB and hence the conductivity of insulator is poor. Even an increase in temperature or applied electric field is insufficient to transfer electrons from VB to CB.

**Conductors:** A conductor is a material which supports a generous flow of charge when a voltage is applied across its terminals. i.e. it has very high conductivity. Eg: Copper, Aluminum, Silver, Gold. The resistivity of a conductor is in the order of  $10^{-4}$  and  $10^{-6}$   $\Omega$ -cm. The Valance and conduction bands overlap (fig1.1) and there is no energy gap for the electrons to move from valance band to conduction band. This implies that there are free electrons in CB even at absolute zero temperature (0K). Therefore at room temperature when electric field is applied large current flows through the conductor.

**Semiconductor**: A semiconductor is a material that has its conductivity somewhere between the insulator and conductor. The resistivity level is in the range of 10 and  $10^4~\Omega$ -cm. Two of the most commonly used are Silicon (Si=14 atomic no.) and germanium (Ge=32 atomic no.). Both have 4 valance electrons. The forbidden band gap is in the order of 1eV. For eg., the band gap energy for Si, Ge and GaAs is 1.21, 0.785 and 1.42 eV, respectively at absolute zero temperature (OK). At OK and at low temperatures, the valance band electrons do not have sufficient energy to move from V to CB. Thus semiconductors act a insulators at OK. as the temperature increases, a large number of valance electrons acquire sufficient energy to leave the VB, cross the forbidden band gap and reach CB. These are now free electrons as they can move freely under the influence of electric field. At room temperature there are sufficient electrons in the CB and hence the semiconductor is capable of conducting some current at room temperature.

Inversely related to the conductivity of a material is its resistance to the flow of charge or current. Typical resistivity values for various materials' are given as follows.

| Insulator                  | Semiconductor                | Conductor                       |

|----------------------------|------------------------------|---------------------------------|

| 10 <sup>-6</sup> Ω-cm (Cu) | 50Ω-cm (Ge)                  | 10 <sup>12</sup> Ω-cm<br>(mica) |

|                            | 50x10 <sup>3</sup> Ω-cm (Si) |                                 |

Typical resistivity values

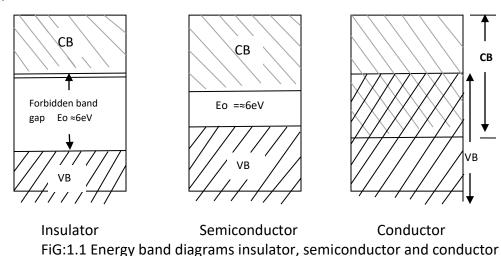

## 1.0.1 Semiconductor Types

A pure form of semiconductors is called as intrinsic semiconductor. Conduction in intrinsic sc is either due to thermal excitation or crystal defects. Si and Ge are the two most important semiconductors used. Other examples include Gallium arsenide GaAs, Indium Antimonide (InSb) etc.

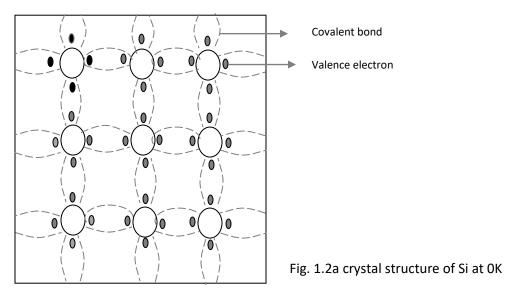

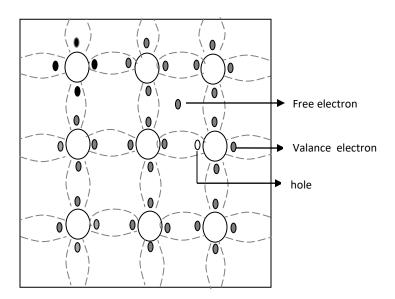

Let us consider the structure of Si. A Si atomic no. is 14 and it has 4 valance electrons. These 4 electrons are shared by four neighboring atoms in the crystal structure by means of covalent bond. Fig. 1.2a shows the crystal structure of Si at absolute zero temperature (OK). Hence a pure SC acts has poor conductivity (due to lack of free electrons) at low or absolute zero temperature.

At room temperature some of the covalent bonds break up to thermal energy as shown in fig 1.2b. The valance electrons that jump into conduction band are called as free electrons that are available for conduction.

Fig. 1.2b crystal structure of Si at room temperatureOK

The absence of electrons in covalent bond is represented by a small circle usually referred to as hole which is of positive charge. Even a hole serves as carrier of electricity in a manner similar to that of free electron.

The mechanism by which a hole contributes to conductivity is explained as follows:

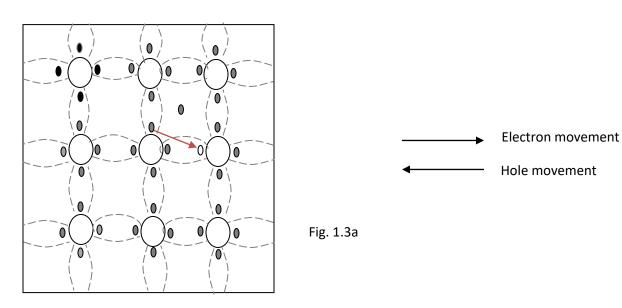

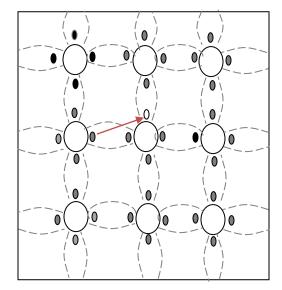

When a bond is in complete so that a hole exists, it is relatively easy for a valance electron in the neighboring atom to leave its covalent bond to fill this hole. An electron moving from a bond to fill a hole moves in a direction opposite to that of the electron. This hole, in its new position may now be filled by an electron from another covalent bond and the hole will correspondingly move one more step in the direction opposite to the motion of electron. Here we have a mechanism for conduction of electricity which does not involve free electrons. This phenomenon is illustrated in fig1.3

Fig. 1.3c

Fig 1.3a show that there is a hole at ion 6.Imagine that an electron from ion 5 moves into the hole at ion 6 so that the configuration of 1.3b results. If we compare both fig1.3a &fig 1.3b, it appears as if the hole has moved towards the left from ion6 to ion 5. Further if we compare fig 1.3b and fig 1.3c, the hole moves from ion5 to ion 4. This discussion indicates the motion of hole is in a direction opposite to that of motion of electron. Hence we consider holes as physical entities whose movement constitutes flow of current.

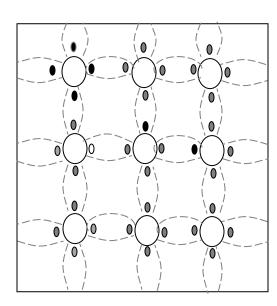

In a pure semiconductor, the number of holes is equal to the number of free electrons.

#### 1.0.2 EXTRINSIC SEMICONDUCTOR

Intrinsic semiconductor has very limited applications as they conduct very small amounts of current at room temperature. The current conduction capability of intrinsic semiconductor can be increased significantly by adding a small amounts impurity to the intrinsic semiconductor. By adding impurities it becomes impure or extrinsic semiconductor. This process of adding impurities is called as doping. The amount of impurity added is 1 part in 10<sup>6</sup> atoms.

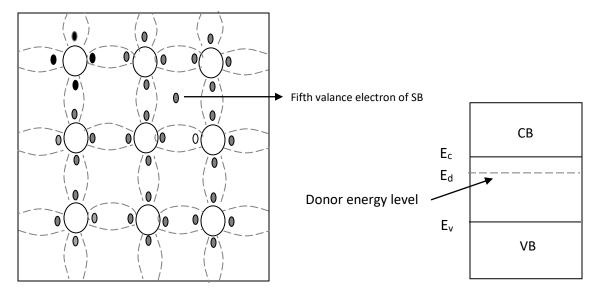

**N type semiconductor:** If the added impurity is a pentavalent atom then the resultant semiconductor is called N-type semiconductor. Examples of pentavalent impurities are Phosphorus, Arsenic, Bismuth, Antimony etc.

A pentavalent impurity has five valance electrons. Fig 1.4a shows the crystal structure of N-type semiconductor material where four out of five valance electrons of the impurity atom(antimony) forms covalent bond with the four intrinsic semiconductor atoms. The fifth electron is loosely bound to the impurity atom. This loosely bound electron can be easily

Fig. 1.4a crystal structure of N type SC

Fig. 1.4bEnergy band diagram of N type

Excited from the valance band to the conduction band by the application of electric field or increasing the thermal energy. The energy required to detach the fifth electron form the impurity atom is very small of the order of 0.01ev for Ge and 0.05 eV for Si.

The effect of doping creates a discrete energy level called donor energy level in the forbidden band gap with energy level  $E_d$  slightly less than the conduction band (fig 1.4b). The difference between the energy levels of the conducting band and the donor energy level is the energy required to free the fifth valance electron (0.01 eV for Ge and 0.05 eV for Si). At room temperature almost all the fifth electrons from the donor impurity atom are raised to conduction band and hence the number of electrons in the conduction band increases significantly. Thus every antimony atom contributes to one conduction electron without creating a hole.

In the N-type sc the no. of electrons increases and the no. of holes decreases compared to those available in an intrinsic sc. The reason for decrease in the no. of holes is that the larger no. of electrons present increases the recombination of electrons with holes. Thus current in N type sc is dominated by electrons which are referred to as majority carriers. Holes are the minority carriers in N type sc

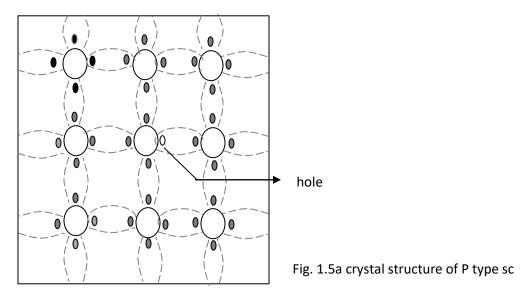

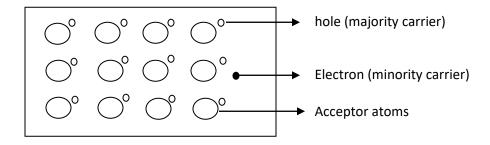

**P type semiconductor:** If the added impurity is a trivalent atom then the resultant semiconductor is called P-type semiconductor. Examples of trivalent impurities are Boron, Gallium, indium etc.

The crystal structure of p type sc is shown in the fig1.5a. The three valance electrons of the impurity (boon) forms three covalent bonds with the neighboring atoms and a vacancy exists in the fourth bond giving rise to the holes. The hole is ready to accept an electron from the neighboring atoms. Each trivalent atom contributes to one hole generation and thus introduces a large no. of holes in the valance band. At the same time the no. electrons are decreased compared to those available in intrinsic sc because of increased recombination due to creation of additional holes.

Thus in P type sc , holes are majority carriers and electrons are minority carriers. Since each trivalent impurity atoms are capable accepting an electron, these are called as acceptor atoms. The following fig 1.5b shows the pictorial representation of P type sc

Fig. 1.5b crystal structure of P type sc

- The conductivity of N type sc is greater than that of P type sc as the mobility of electron is greater than that of hole.

- For the same level of doping in N type sc and P type sc, the conductivity of an Ntype sc is around twice that of a P type sc

#### 1.0.3 CONDUCTIVITY OF SEMICONDUCTOR

In a pure sc, the no. of holes is equal to the no. of electrons. Thermal agitation continue to produce new electron-hole pairs and the electron hole pairs disappear because of recombination. with each electron hole pair created , two charge carrying particles are formed . One is negative which is a free electron with mobility  $\mu_n$ . The other is a positive i.e., hole with mobility  $\mu_p$ . The electrons and hole move in opposite direction in a an electric field E, but since they are of opposite sign, the current due to each is in the same direction. Hence the total current density J within the intrinsic sc is given by

```

J = J_n + J_p

= q n \mu_n E + q p \mu_p E

= (n \mu_n + p \mu_p) q E

= \sigma E

```

Where n=no. of electrons / unit volume i.e., concentration of free electrons

P= no. of holes / unit volume i.e., concentration of holes

E=applied electric field strength, V/m

q= charge of electron or hole I n Coulombs

Hence,  $\sigma$  is the conductivity of sc which is equal to  $(n \mu_n + p \mu_p)q$ . he resistivity of sc is reciprocal of conductivity.

$$P = 1/\sigma$$

It is evident from the above equation that current density with in a sc is directly proportional to applied electric field E.

For pure sc,  $n=p=n_i$  where  $n_i = intrinsic concentration. The value of <math>n_i$  is given by

$n_i^2 = AT^3 \exp(-E_{GO}/KT)$

therefore,  $J = n_i (\mu_n + \mu_p) q E$

Hence conductivity in intrinsic sc is  $\sigma i = n_i (\mu_n + \mu_p) q$

Intrinsic conductivity increases at the rate of 5% per ° C for Ge and 7% per ° C for Si.

## Conductivity in extrinsic sc (N Type and P Type):

The conductivity of intrinsic sc is given by  $\sigma i = n_i (\mu_n + \mu_p) q = (n \mu_n + p \mu_p) q$

For N type , n>>p

Therefore  $\sigma = q n \mu_n$

For P type ,p>>n

Therefore  $\sigma = q p \mu_p$

#### 1.0.4 CHARGE DENSITIES IN P TYPE AND N TYPE SEMICONDUCTOR:

#### Mass Action Law:

Under thermal equilibrium for any semiconductor, the product of the no. of holes and the concentration of electrons is constant and is independent of amount of donor and acceptor impurity doping.

$n.p=n_i^2$

where n= eleetron concentration

p = hole concentration

n<sub>i</sub><sup>2</sup>= intrinsic concentration

Hence in N type sc , as the no. of electrons increase the no. of holes decreases. Similarly in P type as the no. of holes increases the no. of electrons decreases. Thus the product is constant and is equal to  $n_i^2$  in case of intrinsic as well as extrinsic sc.

The law of mass action has given the relationship between free electrons concentration and hole concentration. These concentrations are further related by the law of electrical neutrality as explained below.

## Law of electrical neutrality:

Sc materials are electrically neutral. According to the law of electrical neutrality, in an electrically neutral material, the magnitude of positive charge concentration is equal to tat of negative charge concentration. Let us consider a sc that has  $N_D$  donor atoms per cubic centimeter and  $N_A$  acceptor atoms per cubic centimeter i.e., the concentration of donor and acceptor atoms are  $N_D$  and  $N_A$  respectively. Therefore  $N_D$  positively charged ions per cubic centimeter are contributed by donor atoms and  $N_A$  negatively charged ions per cubic centimeter are contributed by the acceptor atoms. Let n, p is concentration of free electrons and holes respectively. Then according to the law of neutrality

$$N_D + p = N_A + n$$

.....eq 1.1 For N type sc,  $N_A = 0$  and  $n >> p$ . Therefore  $N_D \approx n$  .....eq 1.2

Hence for N type sc the free electron concentration is approximately equal to the concentration of donor atoms. In later applications since some confusion may arise as to which type of sc is under consideration a the given moment, the subscript n or p is added for Ntype or P type respectively. Hence eq1.2 becomes  $N_D \approx n_n$

Therefore current density in N type sc is  $J = N_D \mu_n q E$

And conductivity  $\sigma = N_D \mu_n q$

For P type sc,  $N_D = 0$  and p>>n. Therefore  $N_A \approx p$

Or

$$N_A \approx p_p$$

Hence for P type sc the hole concentration is approximately equal to the concentration of acceptor atoms.

Therefore current density in N type sc is  $J = N_A \mu_D q E$

And conductivity  $\sigma = N_A \mu_p q$

Mass action law for N type,  $n_n p_n = n_i^2$

$$p_n = n_i^2 / N_D$$

since  $(n_n \approx N_D)$

Mass action law for P type,  $n_p p_p = n_i^2$

$$n_p = n_i^2 / N_A$$

since  $(p_p \approx N_A)$

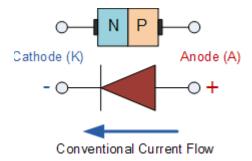

## 1.1 QUANTITATIVE THEORY OF PN JUNCTION DIODE

## 1.1.1 PN JUNCTION WITH NO APPLIED VOLTAGE OR OPEN CIRCUIT CONDITION:

In a piece of sc, if one half is doped by p type impurity and the other half is doped by n type impurity, a PN junction is formed. The plane dividing the two halves or zones is called PN junction. As

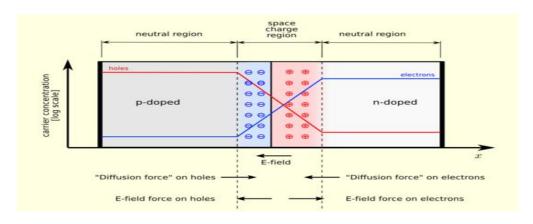

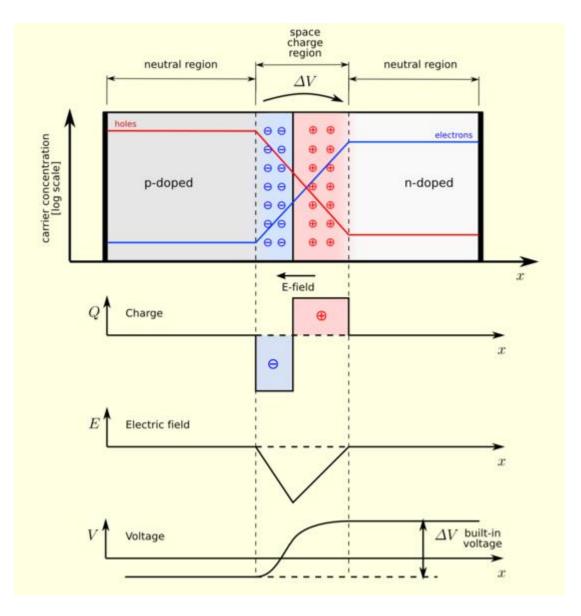

shown in the fig the n type material has high concentration of free electrons, while p type material has high concentration of holes. Therefore at the junction there is a tendency of free electrons to diffuse over to the P side and the holes to the N side. This process is called diffusion. As the free electrons move across the junction from N type to P type, the donor atoms become positively charged. Hence a positive charge is built on the N-side of the junction. The free electrons that cross the junction uncover the negative acceptor ions by filing the holes. Therefore a negative charge is developed on the p –side of the junction. This net negative charge on the p side prevents further diffusion of electrons into the p side. Similarly the net positive charge on the N side repels the hole crossing from p side to N side. Thus a barrier sis set up near the junction which prevents the further movement of charge carriers i.e. electrons and holes. As a consequence of induced electric field across the depletion layer, an electrostatic potential difference is established between P and N regions, which are called the potential barrier, junction barrier, diffusion potential or contact potential, Vo. The magnitude of the contact potential Vo varies with doping levels and temperature. Vo is 0.3V for Ge and 0.72 V for Si.

Fig 1.6: Symbol of PN Junction Diode

The electrostatic field across the junction caused by the positively charged N-Type region tends to drive the holes away from the junction and negatively charged p type regions tend to drive the electrons away from the junction. The majority holes diffusing out of the P region leave behind negatively charged acceptor atoms bound to the lattice, thus exposing a negatives pace charge in a previously neutral region. Similarly electrons diffusing from the N region expose positively ionized donor atoms and a double space charge builds up at the junction as shown in the fig. 1.7a

Fig 1.7a

It is noticed that the space charge layers are of opposite sign to the majority carriers diffusing into them, which tends to reduce the diffusion rate. Thus the double space of the layer causes an electric field to be set up across the junction directed from N to P regions, which is in such a direction to inhibit the diffusion of majority electrons and holes as illustrated in fig 1.7b. The shape of the charge density,  $\rho$ , depends upon how diode id doped. Thus the junction region is depleted of mobile charge carriers. Hence it is called depletion layer, space region, and transition region. The depletion region is of the order of 0.5 $\mu$ m thick. There are no mobile carriers in this narrow depletion region. Hence no current flows across the junction and the system is in equilibrium. To the left of this depletion layer, the carrier concentration is  $p = N_A$  and to its right it is  $n = N_D$ .

Fig 1.7b

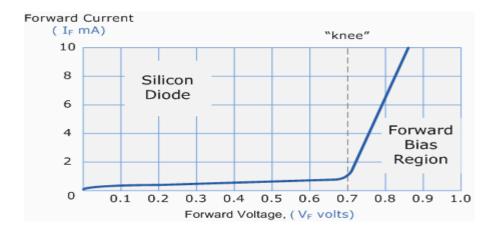

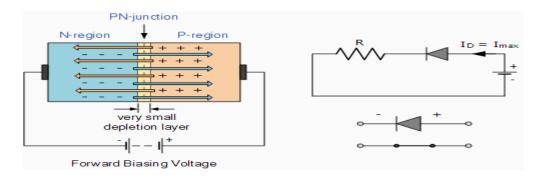

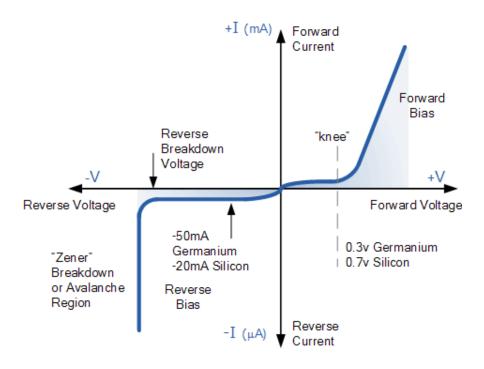

#### 1.1.2 FORWARD BIASED JUNCTION DIODE

When a diode is connected in a **Forward Bias** condition, a negative voltage is applied to the N-type material and a positive voltage is applied to the P-type material. If this external voltage becomes greater than the value of the potential barrier, approx. 0.7 volts for silicon and 0.3 volts for germanium, the potential barriers opposition will be overcome and current will start to flow. This is because the negative voltage pushes or repels electrons towards the junction giving them the energy to cross over and combine with the holes being pushed in the opposite direction towards the junction by the positive voltage. This results in a characteristics curve of zero current flowing up to this voltage point, called the "knee" on the static curves and then a high current flow through the diode with little increase in the external voltage as shown below.

## **Forward Characteristics Curve for a Junction Diode**

Fig 1.8a: Diode Forward Characteristics

The application of a forward biasing voltage on the junction diode results in the depletion layer becoming very thin and narrow which represents a low impedance path through the junction thereby allowing high currents to flow. The point at which this sudden increase in current takes place is represented on the static I-V characteristics curve above as the "knee" point.

#### Forward Biased Junction Diode showing a Reduction in the Depletion Layer

Fig 1.8b: Diode Forward Bias

This condition represents the low resistance path through the PN junction allowing very large currents to flow through the diode with only a small increase in bias voltage. The actual potential difference across the junction or diode is kept constant by the action of the depletion layer at approximately 0.3v for germanium and approximately 0.7v for silicon junction diodes. Since the diode can conduct "infinite" current above this knee point as it effectively becomes a short circuit, therefore resistors are used in series with the diode to limit its current flow. Exceeding its maximum forward current specification causes the device to dissipate more power in the form of heat than it was designed for resulting in a very quick failure of the device.

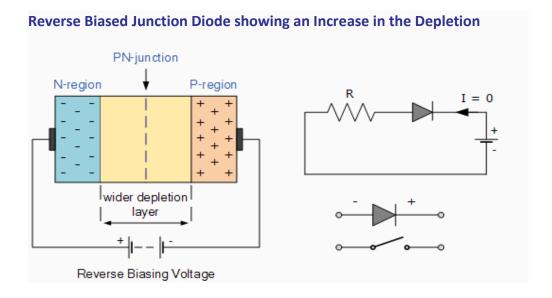

#### 1.1.2 PN JUNCTION UNDER REVERSE BIAS CONDITION:

## **Reverse Biased Junction Diode**

When a diode is connected in a **Reverse Bias** condition, a positive voltage is applied to the N-type material and a negative voltage is applied to the P-type material. The positive voltage applied to the N-type material attracts electrons towards the positive electrode and away from the junction, while the holes in the P-type end are also attracted away from the junction towards the negative electrode. The net result is that the depletion layer grows wider due to a lack of electrons and holes and presents a high impedance path, almost an insulator. The result is that a high potential barrier is created thus preventing current from flowing through the semiconductor material.

Fig 1.9a: Diode Reverse Bias

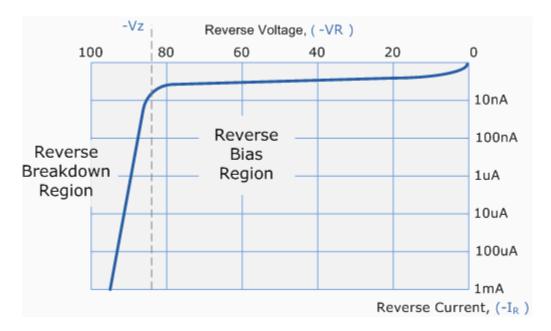

This condition represents a high resistance value to the PN junction and practically zero current flows through the junction diode with an increase in bias voltage. However, a very small **leakage current** does flow through the junction which can be measured in microamperes, ( $\mu$ A). One final point, if the reverse bias voltage Vr applied to the diode is increased to a sufficiently high enough value, it will cause the PN junction to overheat and fail due to the avalanche effect around the junction. This may

cause the diode to become shorted and will result in the flow of maximum circuit current, and this shown as a step downward slope in the reverse static characteristics curve below.

## **Reverse Characteristics Curve for a Junction Diode**

Fig 1.9b: Diode Reverse Characteristics

Sometimes this avalanche effect has practical applications in voltage stabilizing circuits where a series limiting resistor is used with the diode to limit this reverse breakdown current to a preset maximum value thereby producing a fixed voltage output across the diode. These types of diodes are commonly known as **Zener Diodes**

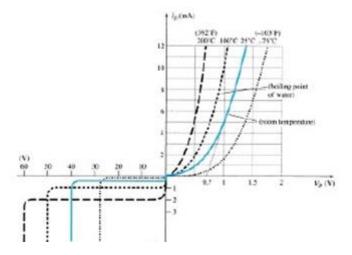

#### 1.2 VI CHARACTERISTICS AND THEIR TEMPERATURE DEPENDENCE

Diode terminal characteristics equation for diode junction current:

$$I_D = I_0 (e^{\frac{v}{\eta v_T}} - 1)$$

Where  $V_T = KT/q$ ;

$V_{\text{D}}$  diode terminal voltage, Volts

I<sub>o</sub> temperature-dependent saturation current, μA

T absolute temperature of p-n junction, K

K \_ Boltzmann's constant 1.38x 10 -23J/K)

q electron charge 1.6x10-19 C

$\eta$  = empirical constant, 1 for Ge and 2 for Si

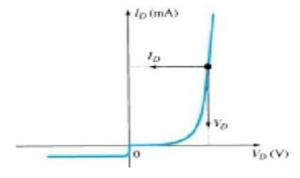

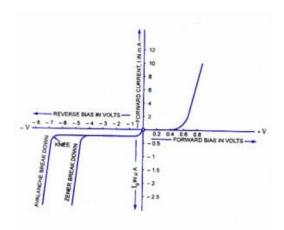

Fig 1.10: Diode Characteristics

## **Temperature Effects on Diode**

Temperature can have a marked effect on the characteristics of a silicon semiconductor diode as shown in Fig. 11 It has been found experimentally that the reverse saturation current Io will just about double in magnitude for every 10°C increase in temperature.

Fig 1.11 Variation in Diode Characteristics with temperature change

It is not uncommon for a germanium diode with an  $I_0$  in the order of 1 or 2 A at 25°C to have a leakage current of 100 A - 0.1 mA at a temperature of 100°C. Typical values of  $I_0$  for silicon are much lower than

that of germanium for similar power and current levels. The result is that even at high temperatures the levels of I<sub>o</sub> for silicon diodes do not reach the same high levels obtained. For germanium—a very important reason that silicon devices enjoy a significantly higher level of development and utilization in design. Fundamentally, the open-circuit equivalent in the reverse bias region is better realized at any temperature with silicon than with germanium. The increasing levels of I<sub>o</sub> with temperature account for the lower levels of threshold voltage, as shown in Fig. 1.11. Simply increase the level of I<sub>o</sub> in and not rise in diode current. Of course, the level of TK also will be increase, but the increasing level of I<sub>o</sub> will overpower the smaller percent change in TK. As the temperature increases the forward characteristics are actually becoming more "ideal,"

#### 1.3 IDEAL VERSUS PRACTICAL RESISTANCE LEVELS

#### DC or Static Resistance

The application of a dc voltage to a circuit containing a semiconductor diode will result in an operating point on the characteristic curve that will not change with time. The resistance of the diode at the operating point can be found simply by finding the corresponding levels of VD and ID as shown in Fig. 1.12 and applying the following Equation:

$$R_D = \frac{V_D}{I_D}$$

The dc resistance levels at the knee and below will be greater than the resistance levels obtained for the vertical rise section of the characteristics. The resistance levels in the reverse-bias region will naturally be quite high. Since ohmmeters typically employ a relatively constant-current source, the resistance determined will be at a preset current level (typically, a few mill amperes).

Fig 1.12 Determining the dc resistance of a diode at a particular operating point.

## **AC or Dynamic Resistance**

It is obvious from Eq. 1.3 that the dc resistance of a diode is independent of the shape of the characteristic in the region surrounding the point of interest. If a sinusoidal rather than dc input is applied, the situation will change completely. The varying input will move the instantaneous operating point up and down a region of the characteristics and thus defines a specific change in current and voltage as shown in Fig. 1.13. With no applied varying signal, the point of operation would be the Q-point appearing on Fig. 1.13 determined by the applied dc levels. The designation Q-point is derived from the word quiescent, which means "still or unvarying." A straight-line drawn tangent to the curve through the Q-point as shown in Fig. 1.13 will define a particular change in voltage and current that can be used to determine the ac or dynamic resistance for this region of the diode characteristics. In equation form,

$$r_d = \frac{\Delta V_d}{\Delta I_d}$$

Where  $\Delta$  Signifies a finite change in the quantity

Fig 1.13: Determining the ac resistance of a diode at a particular operating point.

#### 1.4 DIODE EQUIVALENT CIRCUITS

An equivalent circuit is a combination of elements properly chosen to best represent the actual terminal characteristics of a device, system, or such in a particular operating region. In other words, once the equivalent circuit is defined, the device symbol can be removed from a schematic and the equivalent circuit inserted in its place without severely affecting the actual behavior of the system. The result is often a network that can be solved using traditional circuit analysis techniques.

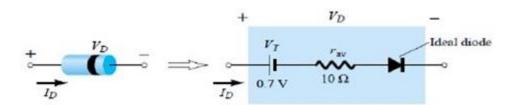

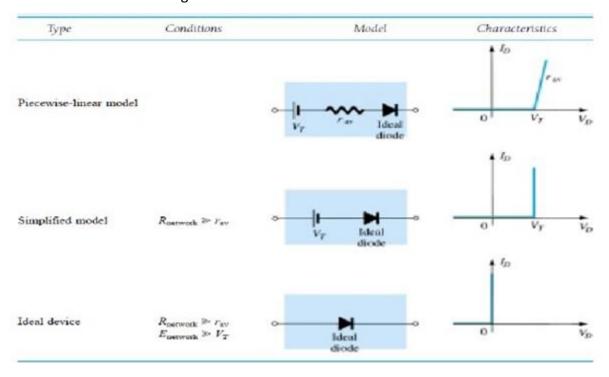

#### **Piecewise-Linear Equivalent Circuit**

One technique for obtaining an equivalent circuit for a diode is to approximate the characteristics of the device by straight-line segments, as shown in Fig. 1.31. The resulting equivalent

circuit is naturally called the piecewise-linear equivalent circuit. It should be obvious from Fig. 1.31 that the straight-line segments do not result in an exact duplication of the actual characteristics, especially in the knee region. However, the resulting segments are sufficiently close to the actual curve to establish an equivalent circuit that will provide an excellent first approximation to the actual behaviour of the device. The ideal diode is included to establish that there is only one direction of conduction through the device, and a reverse-bias condition will result in the open- circuit state for the device. Since a silicon semiconductor, diode does not reach the conduction state until VD reaches 0.7 V with a forward bias (as shown in Fig. 1.14a), a battery  $V_T$  opposing the conduction direction must appear in the equivalent circuit as shown in Fig. 1.14b. The battery simply specifies that the voltage across the device must be greater than the threshold battery voltage before conduction through the device in the direction dictated by the ideal diode can be established. When conduction is established, the resistance of the diode will be the specified value of  $r_{av}$ .

Fig: 1.14aDiode piecewise-linear model characteristics

Fig: 1.14b Diode piecewise-linear model equivalent circuit

The approximate level of  $r_{av}$  can usually be determined from a specified operating point on the specification sheet. For instance, for a silicon semiconductor diode, if IF  $_{-}$  10 mA (a forward conduction current for the diode) at VD  $_{-}$  0.8 V, we know for silicon that a shift of 0.7 V is required before the characteristics rise.

Fig 1.15 Ideal Diode and its characteristics

Fig 1.16: Diode equivalent circuits(models)

#### 1.5 TRANSITION AND DIFFUSION CAPACITANCE

Electronic devices are inherently sensitive to very high frequencies. Most shunt capacitive effects that can be ignored at lower frequencies because the reactance  $XC=1/2\pi fC$  is very large (open-circuit equivalent). This, however, cannot be ignored at very high frequencies. XC will become sufficiently small due to the high value of f to introduce a low-reactance "shorting" path. In the p-n semiconductor diode, there are two capacitive effects to be considered. In the reverse-bias region we have the transition- or depletion region capacitance (CT), while in the forward-bias region we have the diffusion (CD) or storage capacitance. Recall that the basic equation for the capacitance of a parallel-plate capacitor is defined by C=A/d, where E is the permittivity of the dielectric (insulator) between the plates of area A separated by a distance d. In the reverse-, bias region there is a depletion region (free of carriers) that behaves essentially like an insulator between the layers of opposite charge. Since

the depletion width (d) will increase with increased reverse-bias potential, the resulting transition capacitance will decrease. The fact that the capacitance is dependent on the applied reverse-bias potential has application in a number of electronic systems. Although the effect described above will also be present in the forward-bias region, it is over shadowed by a capacitance effect directly dependent on the rate at which charge is injected into the regions just outside the depletion region. The capacitive effects described above are represented by a capacitor in parallel with the ideal diode, as shown in Fig. 1.38. For low- or mid-frequency applications (except in the power area), however, the capacitor is normally not included in the diode symbol.

Fig 1.17: Including the effect of the transition or diffusion capacitance on the semiconductor diode

**Diode capacitances:** The diode exhibits two types of capacitances transition capacitance and diffusion capacitance.

- Transition capacitance: The capacitance which appears between positive ion layer in n-region and negative ion layer in p-region.

- ➤ Diffusion capacitance: This capacitance originates due to diffusion of charge carriers in the opposite regions.

The transition capacitance is very small as compared to the diffusion capacitance.

In reverse bias transition, the capacitance is the dominant and is given by:

$$C_T = \mathcal{C} A/W$$

where C<sub>T</sub> - transition capacitance

A - diode cross sectional area

W - depletion region width

In forward bias, the diffusion capacitance is the dominant and is given by:

$$C_D = dQ/dV = \tau^* dI/dV = \tau^* g = \tau/r \text{ (general)}$$

where C<sub>D</sub> - diffusion capacitance

dQ - change in charge stored in depletion region

V - change in applied voltage

τ- time interval for change in voltage

g - diode conductance

r - diode resistance

The diffusion capacitance at low frequencies is given by the formula:

$$C_D = \tau *g/2$$

(low frequency)

The diffusion capacitance at high frequencies is inversely proportional to the frequency and is given by the formula:

$$C_D = g(\tau/2\omega)^{\frac{4}{2}}$$

Note: The variation of diffusion capacitance with applied voltage is used in the design of varactor.

#### **1.6 BREAK DOWN MECHANISMS**

When an ordinary **P-N junction diode** is reverse biased, normally only very small reverse saturation current flows. This current is due to movement of minority carriers. It is almost independent of the voltage applied. However, if the reverse bias is increased, a point is reached when the junction breaks down and the reverse current increases abruptly. This current could be large enough to destroy the junction. If the reverse current is limited by means of a suitable series resistor, the power dissipation at the junction will not be excessive, and the device may be operated continuously in its breakdown region to its normal (reverse saturation) level. It is found that for a suitably designed diode, the breakdown voltage is very stable over a wide range of reverse currents. This quality gives the breakdown diode many useful applications as a voltage reference source.

The critical value of the voltage, at which the breakdown of a P-N junction diode occurs, is called the *breakdown voltage*. The breakdown voltage depends on the width of the depletion region, which, in turn, depends on the doping level. The junction offers almost zero resistance at the breakdown point.

There are two mechanisms by which breakdown can occur at a reverse biased P-N junction:

- 1. avalanche breakdown and

- 2. Zener breakdown.

## Avalanche breakdown

The minority carriers, under reverse biased conditions, flowing through the junction acquire a kinetic energy which increases with the increase in reverse voltage. At a sufficiently high reverse voltage (say 5 V or more), the kinetic energy of minority carriers becomes so large that they knock out electrons from the covalent bonds of the semiconductor material. As a result of collision, the liberated

electrons in turn liberate more electrons and the current becomes very large leading to the breakdown of the crystal structure itself. This phenomenon is called the avalanche breakdown. The breakdown region is the knee of the characteristic curve. Now the current is not controlled by the junction voltage but rather by the external circuit.

#### Zener breakdown

Under a very high reverse voltage, the depletion region expands and the potential barrier increases leading to a very high electric field across the junction. The electric field will break some of the covalent bonds of the semiconductor atoms leading to a large number of free minority carriers, which suddenly increase the reverse current. This is called the Zener effect. The breakdown occurs at a particular and constant value of reverse voltage called the breakdown voltage, it is found that Zener breakdown occurs at electric field intensity of about  $3 \times 10^7 \text{ V/m}$ .

Fig 1.18: Diode characteristics with breakdown

Either of the two (Zener breakdown or avalanche breakdown) may occur independently, or both of these may occur simultaneously. Diode junctions that breakdown below 5 V are caused by Zener effect. Junctions that experience breakdown above 5 V are caused by avalanche effect. Junctions that breakdown around 5 V are usually caused by combination of two effects. The Zener breakdown occurs in heavily doped junctions (P-type semiconductor moderately doped and N-type heavily doped), which produce narrow depletion layers. The avalanche breakdown occurs in lightly doped junctions, which produce wide depletion layers. With the increase in junction temperature Zener breakdown voltage is reduced while the avalanche breakdown voltage increases. The Zener diodes have a negative temperature coefficient while avalanche diodes have a positive temperature coefficient. Diodes that have breakdown voltages around 5 V have zero temperature coefficient. The breakdown phenomenon is reversible and harmless so long as the safe operating temperature is maintained.

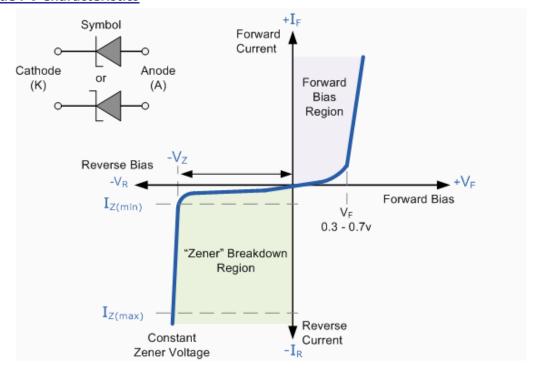

#### 1.7 ZENER DIODES

The **Zener diode** is like a general-purpose signal diode consisting of a silicon PN junction. When biased in the forward direction it behaves just like a normal signal diode passing the rated current, but as soon as a reverse voltage applied across the zener diode exceeds the rated voltage of the device, the diodes breakdown voltage V<sub>B</sub> is reached at which point a process called *Avalanche Breakdown* occurs in the semiconductor depletion layer and a current starts to flow through the diode to limit this increase in voltage.

The current now flowing through the zener diode increases dramatically to the maximum circuit value (which is usually limited by a series resistor) and once achieved this reverse saturation current remains fairly constant over a wide range of applied voltages. This breakdown voltage point,  $V_B$  is called the "zener voltage" for zener diodes and can range from less than one volt to hundreds of volts.

The point at which the zener voltage triggers the current to flow through the diode can be very accurately controlled (to less than 1% tolerance) in the doping stage of the diodes semiconductor construction giving the diode a specific *zener breakdown voltage*, (Vz) for example, 4.3V or 7.5V. This zener breakdown voltage on the I-V curve is almost a vertical straight line.

## **Zener Diode I-V Characteristics**

Fig 1.19: Zener diode characteristics

The **Zener Diode** is used in its "reverse bias" or reverse breakdown mode, i.e. the diodes anode connects to the negative supply. From the I-V characteristics curve above, we can see that the zener

diode has a region in its reverse bias characteristics of almost a constant negative voltage regardless of the value of the current flowing through the diode and remains nearly constant even with large changes in current as long as the zener diodes current remains between the breakdown current  $I_{Z(min)}$  and the maximum current rating  $I_{Z(max)}$ .

This ability to control itself can be used to great effect to regulate or stabilize a voltage source against supply or load variations. The fact that the voltage across the diode in the breakdown region is almost constant turns out to be an important application of the zener diode as a voltage regulator. The function of a regulator is to provide a constant output voltage to a load connected in parallel with it in spite of the ripples in the supply voltage or the variation in the load current and the zener diode will continue to regulate the voltage until the diodes current falls below the minimum  $I_{Z(min)}$  value in the reverse breakdown region.

## **UNIT II**

## **BIPOLAR JUNCTION TRANSISTOR**

#### 2.1 INTRODUCTION

A bipolar junction transistor (BJT) is a three terminal device in which operation depends on the interaction of both majority and minority carriers and hence the name bipolar. The BJT is analogues to vacuum triode and is comparatively smaller in size. It is used as amplifier and oscillator circuits, and as a switch in digital circuits. It has wide applications in computers, satellites and other modern communication systems.

A **Transistor** is a three terminal semiconductor device that regulates current or voltage flow and acts as a switch or gate for signals.

Why Do We Need Transistors?

Suppose that you have a FM receiver which grabs the signal you want. The received signal will obviously be weak due to the disturbances it would face during its journey. Now if this signal is read as it is, you cannot get a fair output. Hence we need to amplify the signal. **Amplification** means increasing the signal strength.

This is just an instance. Amplification is needed wherever the signal strength has to be increased. This is done by a transistor. A transistor also acts as a **switch** to choose between available options. It also **regulates** the incoming **current and voltage** of the signals.

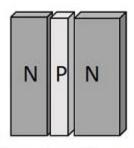

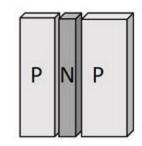

#### Constructional Details of a Transistor

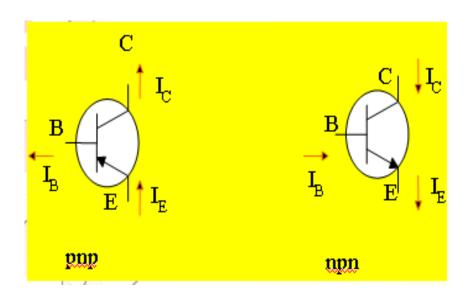

The Transistor is a three terminal solid state device which is formed by connecting two diodes back to back. Hence it has got **two PN junctions**. Three terminals are drawn out of the three semiconductor materials present in it. This type of connection offers two types of transistors. They are **PNP** and **NPN** which means an N-type material between two Ptypes and the other is a P-type material between two N-types respectively.

The construction of transistors is as shown in the following figure which explains the idea discussed above.

## Construction of PNP & NPN Transistors

The three terminals drawn from the transistor indicate Emitter, Base and Collector terminals. They have their functionality as discussed below.

#### **Emitter**

- The left hand side of the above shown structure can be understood as Emitter.

- This has a **moderate size** and is **heavily doped** as its main function is to **supply** a number of **majority carriers**, i.e. either electrons or holes.

- As this emits electrons, it is called as an Emitter.

- This is simply indicated with the letter E.

#### Base

- The middle material in the above figure is the Base.

- This is thin and lightly doped.

- Its main function is to **pass** the majority carriers from the emitter to the collector.

- This is indicated by the letter **B**.

## Collector

- The right side material in the above figure can be understood as a **Collector**.

- Its name implies its function of collecting the carriers.

- This is a bit larger in size than emitter and base. It is moderately doped.

- This is indicated by the letter **C**.

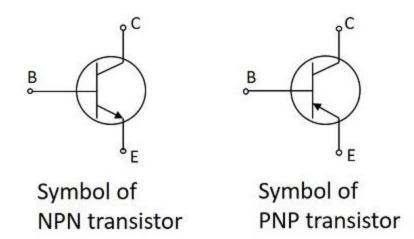

The symbols of PNP and NPN transistors are as shown below.

The **arrow-head** in the above figures indicated the **emitter** of a transistor. As the collector of a transistor has to dissipate much greater power, it is made large. Due to the specific functions of emitter and collector, they are **not interchangeable**. Hence the terminals are always to be kept in mind while using a transistor.

In a Practical transistor, there is a notch present near the emitter lead for identification. The PNP and NPN transistors can be differentiated using a Multimeter. The following figure shows how different practical transistors look like.

We have so far discussed the constructional details of a transistor, but to understand the operation of a transistor, first we need to know about the biasing.

## **Transistor Biasing**

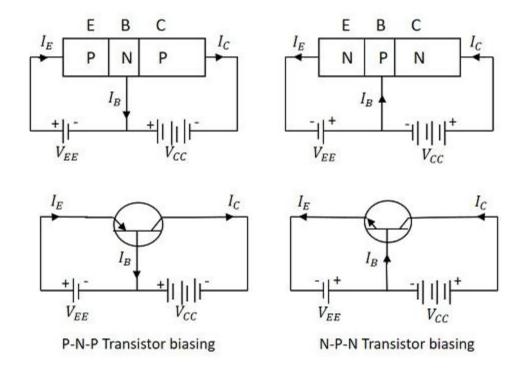

As we know that a transistor is a combination of two diodes, we have two junctions here. As one junction is between the emitter and base, that is called as **Emitter-Base junction** and likewise, the other is **Collector-Base junction**.

**Biasing** is controlling the operation of the circuit by providing power supply. The function of both the PN junctions is controlled by providing bias to the circuit through some dc supply. The figure below shows how a transistor is biased.

By having a look at the above figure, it is understood that

- The N-type material is provided negative supply and P-type material is given positive supply to make the circuit **Forward bias**.

- The N-type material is provided positive supply and P-type material is given negative supply to make the circuit **Reverse bias**.

By applying the power, the **emitter base junction** is always **forward biased** as the emitter resistance is very small. The **collector base junction** is **reverse biased** and its resistance is a bit higher. A small forward bias is sufficient at the emitter junction whereas a high reverse bias has to be applied at the collector junction.

The direction of current indicated in the circuits above, also called as the **Conventional Current**, is the movement of hole current which is **opposite to the electron current**.

## **Operation PNP Transistor**

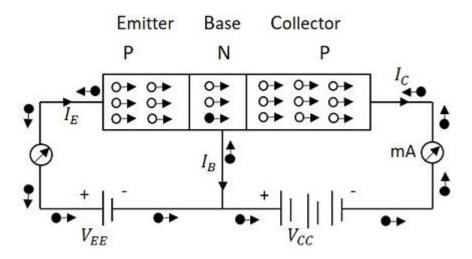

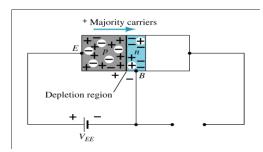

The operation of a PNP transistor can be explained by having a look at the following figure, in which emitter-base junction is forward biased and collector-base junction is reverse biased.

Operation of a PNP transistor

The voltage  $V_{EE}$  provides a positive potential at the emitter which repels the holes in the P-type material and these holes cross the emitter-base junction, to reach the base region. There a very low percent of holes recombine with free electrons of N-region. This provides very low current which constitutes the base current  $I_B$ . The remaining holes cross the collector-base junction, to constitute collector current  $I_C$ , which is the hole current.

As a hole reaches the collector terminal, an electron from the battery negative terminal fills the space in the collector. This flow slowly increases and the electron minority current flows through the emitter, where each electron entering the positive terminal of  $V_{EE}$ , is replaced by a hole by moving towards the emitter junction. This constitutes emitter current  $I_E$ .

Hence we can understand that -

- The conduction in a PNP transistor takes place through holes.

- The collector current is slightly less than the emitter current.

- The increase or decrease in the emitter current affects the collector current.

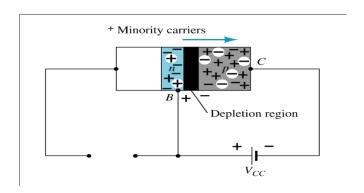

## Operation NPN Transistor

The operation of an NPN transistor can be explained by having a look at the following figure, in which emitter-base junction is forward biased and collector-base junction is reverse biased.

Operation of a NPN transistor

The voltage  $V_{EE}$  provides a negative potential at the emitter which repels the electrons in the N-type material and these electrons cross the emitter-base junction, to reach the base region. There a very low percent of electrons recombine with free holes of P-region. This provides very low current which constitutes the base current  $I_B$ . The remaining holes cross the collector-base junction, to constitute the collector current  $I_C$ .

As an electron reaches out of the collector terminal, and enters the positive terminal of the battery, an electron from the negative terminal of the battery  $\mathbf{V}_{EE}$  enters the emitter region. This flow slowly increases and the electron current flows through the transistor.

Hence we can understand that -

- The conduction in a NPN transistor takes place through electrons.

- The collector current is higher than the emitter current.

- The increase or decrease in the emitter current affects the collector current.

## Advantages

There are many advantages of a transistor such as -

- High voltage gain.

- Lower supply voltage is sufficient.

- Most suitable for low power applications.

- Smaller and lighter in weight.

- Mechanically stronger than vacuum tubes.

- No external heating required like vacuum tubes.

- Very suitable to integrate with resistors and diodes to produce ICs.

There are few disadvantages such as they cannot be used for high power applications due to lower power dissipation. They have lower input impedance and they are temperature dependent.

#### **2.3 TRANSISTOR CURRENT COMPONENTS:**

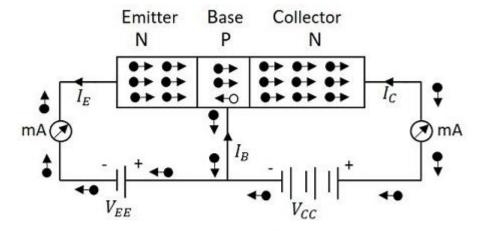

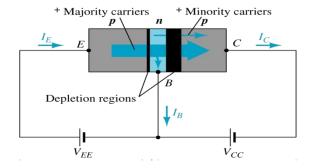

Fig 2.2 Bipolar Junction Transistor Current Components

The above fig 3.2 shows the various current components, which flow across the forward biased emitter junction and reverse- biased collector junction. The emitter current  $I_E$  consists of hole current  $I_{PE}$  (holes crossing from emitter into base) and electron current  $I_{nE}$  (electrons crossing from base into emitter). The ratio of hole to electron currents,  $I_{PE}$  /  $I_{nE}$  , crossing the emitter junction is proportional to the ratio of the conductivity of the p material to that of the n material. In a transistor, the doping of that of the emitter is made much larger than the doping of the base. This feature ensures (in p-n-p transistor) that the emitter current consists an almost entirely of holes. Such a situation is desired since the current which results from electrons crossing the emitter junction from base to emitter do not contribute carriers, which can reach the collector.

Not all the holes crossing the emitter junction  $J_E$  reach the the collector junction  $J_C$ Because some of them combine with the electrons in n-type base. If  $I_{pC}$  is hole current at junction  $J_C$  there must be a bulk recombination current ( $I_{PE}$ - $I_{pC}$ ) leaving the base. Actually, electrons enter the base region through the base lead to supply those charges, which have been lost by recombination with the holes injected in to the base across  $J_{E.}$  If the emitter were open circuited so that  $I_E=0$  then  $I_{pC}$  would be zero. Under these circumstances, the base and collector current  $I_C$  would equal the reverse saturation current  $I_{CO.}$  If  $I_E\neq 0$  then

Ic= Ico- Ipc

For a p-n-p transistor,  $I_{CO}$  consists of holes moving across  $J_{C}$  from left to right (base to collector) and electrons crossing  $J_{C}$  in opposite direction. Assumed referenced direction for  $I_{CO}$  i.e. from right to left, then for a p-n-p transistor,  $I_{CO}$  is negative. For an n-p-n transistor,  $I_{CO}$  is positive. The basic operation will be described using the pnp transistor. The operation of the pnp transistor is exactly the same if the roles played by the electron and hole are interchanged.

One p-n junction of a transistor is reverse-biased, whereas the other is forward-biased.

## 3.3a Forward-biased junction of a pnp transistor

2.3b Reverse-biased junction of a pnp transistor

2.3c Both biasing potentials have been applied to a pnp transistor and resulting majority and minority carrier flows indicated.

Majority carriers (+) will diffuse across the forward-biased p-n junction into the n-type material.

A very small number of carriers (+) will through n-type material to the base terminal. Resulting IB is typically in order of microamperes.

The large number of majority carriers will diffuse across the reverse-biased junction into the p-type material connected to the collector terminal

Applying KCL to the transistor:

$$I_E = I_C + I_B$$

The comprises of two components – the majority and minority carriers

$$I_C = I_{Cmajority} + I_{COminority}$$

$I_{CO} - I_C$  current with emitter terminal open and is called leakage current

Various parameters which relate the current components is given below

# **Emitter efficiency:**

$$\gamma = \frac{current of injected carriers at \pmb{J}_{\scriptscriptstyle E}}{total emitter current}$$

$$\gamma = \frac{I_{pE}}{I_{pE} + I_{nE}} = \frac{I_{pE}}{I_{nE}}$$

### **Transport Factor:**

$$\beta^* = \frac{injected carrier current reaching J_C}{injected carrier n current at J_E}$$

$$\beta^* = \frac{I_{pC}}{I_{pC}}$$

## Large signal current gain:

The ratio of the negative of collector current increment to the emitter current change from zero (cutoff) to  $I_E$  the large signal current gain of a common base transistor.

$$\alpha = \frac{-(I_C - I_{CO})}{I_F}$$

Since  $I_{C \text{ and }} I_E$  have opposite signs, then  $\alpha$ , as defined, is always positive. Typically numerical values of  $\alpha$  lies in the range of 0.90 to 0.995

$$\alpha = \frac{I_{pC}}{I_E} = \frac{I_{pC}}{I_{nE}} * \frac{I_{pE}}{I_E}$$

$$\alpha = \beta * \gamma$$

The transistor alpha is the product of the transport factor and the emitter efficiency. This statement assumes that the collector multiplication ratio  $\alpha^*$  is unity.  $\alpha^*$  is the ratio of total current crossing  $J_C$  to hole arriving at the junction.

#### 2.4 Bipolar Transistor Configurations

A Transistor has 3 terminals, the emitter, the base and the collector. Using these 3 terminals the transistor can be connected in a circuit with one terminal common to both input and output in a 3 different possible configurations.

The three types of configurations are **Common Base, Common Emitter** and **Common Collector** configurations. In every configuration, the emitter junction is forward biased and the collector junction is reverse biased.

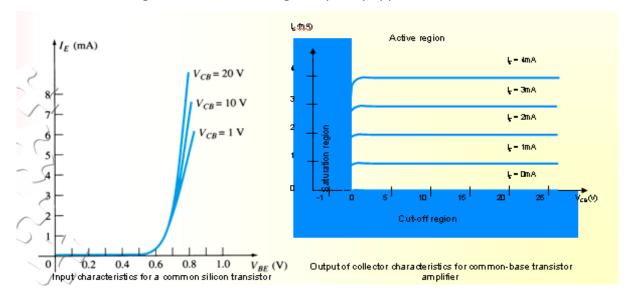

### Common Base (CB) Configuration

The name itself implies that the Base terminal is taken as common terminal for both input and output of the transistor. The common base connection for both NPN and PNP transistors is as shown in the following figure.

#### Common Base Connection

For the sake of understanding, let us consider NPN transistor in CB configuration. When the emitter voltage is applied, as it is forward biased, the electrons from the negative terminal repel the emitter electrons and current flows through the emitter and base to the collector to contribute collector current. The collector voltage **V**<sub>CB</sub> is kept constant throughout this.

In the CB configuration, the input current is the emitter current  $I_E$  and the output current is the collector current  $I_C$ .

### **Current Amplification Factor (α)**

The ratio of change in collector current ( $\Delta IC\Delta IC$ ) to the change in emitter current ( $\Delta IE\Delta IE$ ) when collector voltage  $\mathbf{V}_{CB}$  is kept constant, is called as **Current amplification factor**. It is denoted by  $\alpha$ .

$$lpha \, = \, rac{\Delta I_C}{\Delta I_E} \, \, at \, constant \, V_{CB}$$

#### **Expression for Collector current**

With the idea above, let us try to draw some expression for collector current. Along with the emitter current flowing, there is some amount of base current IB which flows through the base terminal due to electron hole recombination. As collector-base junction is reverse biased, there is another current which is flown due to minority charge carriers. This is the leakage current which can be understood as I<sub>leakage</sub>. This is due to minority charge carriers and hence very small.

The emitter current that reaches the collector terminal is

$$\alpha I_E$$

Total collector current

$$I_C = \alpha I_E + I_{leakage}$$

If the emitter-base voltage  $V_{EB} = 0$ , even then, there flows a small leakage current, which can be termed as  $I_{CBO}$  (collector-base current with output open).

The collector current therefore can be expressed as

$$I_C = \alpha I_E + I_{CBO}$$

$I_E = I_C + I_B$

$I_C = \alpha (I_C + I_B) + I_{CBO}$

$I_C(1 - \alpha) = \alpha I_B + I_{CBO}$

$I_C = (\frac{\alpha}{1 - \alpha}) I_B + (\frac{I_{CBO}}{1 - \alpha})$

$I_C = (\frac{\alpha}{1 - \alpha}) I_B + (\frac{1}{1 - \alpha}) I_{CBO}$

Hence the above derived is the expression for collector current. The value of collector current depends on base current and leakage current along with the current amplification factor of that transistor in use.

# Characteristics of CB configuration

- This configuration provides voltage gain but no current gain.

- Being V<sub>CB</sub> constant, with a small increase in the Emitter-base voltage V<sub>EB</sub>, Emitter current I<sub>E</sub> gets increased.

- Emitter Current IE is independent of Collector voltage VCB.

- Collector Voltage V<sub>CB</sub> can affect the collector current I<sub>C</sub>only at low voltages, when V<sub>EB</sub> is kept constant.

- The input resistance ri is the ratio of change in emitter-base voltage ( $\Delta VEB$ ) to the change in emitter current ( $\Delta IE$ ) at constant collector base voltage  $\mathbf{V}_{CB}$ .

$$=rac{\Delta V_{EB}}{\Delta I_{E}} \; at \, constant \, V_{CB}$$

• As the input resistance is of very low value, a small value of V<sub>EB</sub> is enough to produce a large current flow of emitter current I<sub>E</sub>.

• The output resistance  $r_0$  is the ratio of change in the collector base voltage ( $\Delta VCB$ ) to the change in collector current ( $\Delta IC$ ) at constant emitter current  $I_E$ .

$$r_o = rac{\Delta V_{CB}}{\Delta I_C} \, at \, constant \, l_E$$

- As the output resistance is of very high value, a large change in **V**<sub>CB</sub> produces a very little change in collector current **I**<sub>C</sub>.

- This Configuration provides good stability against increase in temperature.

- The CB configuration is used for high frequency applications.

Fig 2.5 CB Input-Output Characteristics

| Active                                                                                                                                                                                             | Saturation                                                                                                                                         | Cut-off                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| region                                                                                                                                                                                             | region                                                                                                                                             | region                                                                                                         |

| •IE increased, Ic increased  •BE junction forward bias and CB junction reverse bias  •Refer to the graf, Ic ≈ IE  •Ic not depends on VcB  •Suitable region for the transistor working as amplifier | BE and CB junction is forward bias Small changes in VcB will cause big different to Ic The allocation for this region is to the left of VcB = 0 V. | Region below the line of IE=0 A  BE and CB is reverse bias  no current flow at collector, only leakage current |

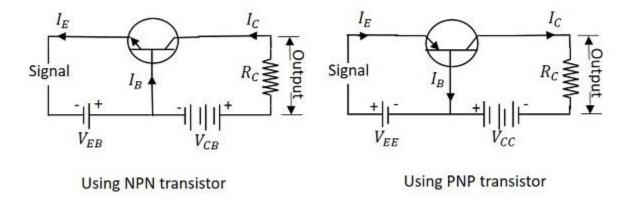

# Common Emitter (CE) Configuration

The name itself implies that the Emitter terminal is taken as common terminal for both input and output of the transistor. The common emitter connection for both NPN and PNP transistors is as shown in the following figure.

# Common Emitter Connection Signal Signal $V_{BE}$ $V_{BE}$ $V_{CE}$ $V_{CE}$ Using PNP transistor

Just as in CB configuration, the emitter junction is forward biased and the collector junction is reverse biased. The flow of electrons is controlled in the same manner. The input current is the base current IB and the output current is the collector current Ic here.

# **Base Current Amplification factor (β)**

Using NPN transistor

The ratio of change in collector current ( $\Delta IC\Delta IC$ ) to the change in base current ( $\Delta IB\Delta IB$ ) is known as Base Current Amplification Factor. It is denoted by  $\beta$

$$\beta = \frac{\Delta I_C}{\Delta I_B}$$

### Relation between $\beta$ and $\alpha$

Let us try to derive the relation between base current amplification factor and emitter current amplification factor.

$$eta = rac{\Delta I_C}{\Delta I_B}$$

$lpha = rac{\Delta I_C}{\Delta I_E}$

$I_E = I_B + I_C$

$\Delta I_E = \Delta I_B + \Delta I_C$

$\Delta I_B = \Delta I_E - \Delta I_C$

We can write

$$eta = rac{\Delta I_C}{\Delta I_E - \Delta I_C}$$

$$eta = rac{rac{\Delta I_C}{\Delta I_E}}{rac{\Delta I_E}{\Delta I_E} - rac{\Delta I_C}{\Delta I_E}}$$

$lpha = rac{\Delta I_C}{\Delta I_E}$

We have

$$\alpha = \frac{\Delta I_C}{\Delta I_E}$$

Therefore,

$$\beta = \frac{\alpha}{1-\alpha}$$

From the above equation, it is evident that, as  $\alpha$  approaches 1,  $\beta$  reaches infinity.

Hence, the current gain in Common Emitter connection is very high. This is the reason this circuit connection is mostly used in all transistor applications.

**Expression for Collector Current**

In the Common Emitter configuration, IB is the input current and Ic is the output current.

We know

And

$$I_C = lpha I_E + I_{CBO}$$

$= lpha (I_B + I_C) + I_{CBO}$   $I_C (1 - lpha) = lpha I_B + I_{CBO}$   $I_C = rac{lpha}{1 - lpha} I_B + rac{1}{1 - lpha} I_{CBO}$

If base circuit is open, i.e. if  $I_B = 0$ ,

The collector emitter current with base open is ICEO

$$I_{CEO} = rac{1}{1-lpha} \, I_{CBO}$$

Substituting the value of this in the previous equation, we get

$$I_C = \frac{\alpha}{1-\alpha}I_B + I_{CEO}$$

$$I_C = \beta I_B + I_{CEO}$$

Hence the equation for collector current is obtained.

#### **Knee Voltage**

In CE configuration, by keeping the base current  $I_B$  constant, if  $V_{CE}$  is varied,  $I_C$  increases nearly to 1v of  $V_{CE}$  and stays constant thereafter. This value of  $V_{CE}$  up to which collector current  $I_C$  changes with  $V_{CE}$  is called the **Knee Voltage**. The transistors while operating in CE configuration, they are operated above this knee voltage.

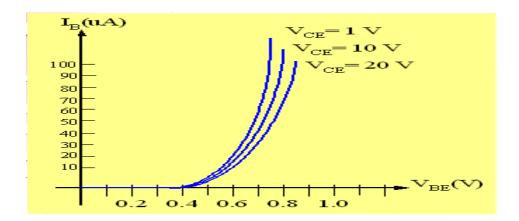

Characteristics of CE Configuration

- This configuration provides good current gain and voltage gain.

- Keeping V<sub>CE</sub> constant, with a small increase in V<sub>BE</sub> the base current I<sub>B</sub> increases rapidly than in CB configurations.

- For any value of V<sub>CE</sub> above knee voltage, I<sub>C</sub> is approximately equal to βI<sub>B</sub>.

- The input resistance  $\mathbf{r}_i$  is the ratio of change in base emitter voltage ( $\Delta VBE$ ) to the change in base current ( $\Delta IB$ ) at constant collector emitter voltage  $\mathbf{V}_{CE}$ .

$$r_i = rac{\Delta V_{BE}}{\Delta I_B} \, at \, constant \, V_{CE}$$

- As the input resistance is of very low value, a small value of V<sub>BE</sub> is enough to produce a large current flow of base current I<sub>B</sub>.

- The output resistance  $\mathbf{r_o}$  is the ratio of change in collector emitter voltage ( $\Delta VCE\Delta VCE$ ) to the change in collector current ( $\Delta IC\Delta IC$ ) at constant  $\mathbf{I_B}$ .

$$r_o = rac{\Delta V_{CE}}{\Delta I_C} \, at \, constant \, I_B$$

As the output resistance of CE circuit is less than that of CB circuit.

This configuration is usually used for bias stabilization methods and audio frequency applications.

Fig 3.9a Input characteristics for common-emitter npn transistor

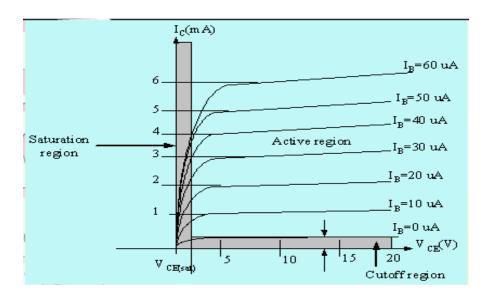

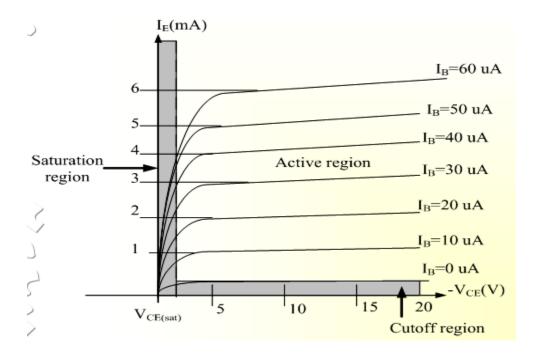

Fig 2.9b Output characteristics for common-emitter npn transistor

| Active region                                                                                                                                                | Saturation region                                                                                                                                                                                                                                                                                                  | Cut-off<br>region                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>B-E junction is forward bias</li> <li>C-B junction is reverse bias</li> <li>can be employed for voltage, current and power amplification</li> </ul> | <ul> <li>B-E and C-B junction is forward bias, thus the values of I<sub>B</sub> and I<sub>C</sub> is too big.</li> <li>The value of V<sub>CE</sub> is so small.</li> <li>Suitable region when the transistor as a logic switch.</li> <li>NOT and avoid this region when the transistor as an amplifier.</li> </ul> | <ul> <li>region below I<sub>B</sub>=0μA is to be avoided if an undistorted o/p signal is required</li> <li>B-E junction and C-B junction is reverse bias</li> <li>I<sub>B</sub>=0, I<sub>C</sub> not zero, during this condition I<sub>C</sub>=I<sub>CEO</sub> where is this current flow when B-E is reverse bias.</li> </ul> |

#### 2.7 COMMON - COLLECTOR CONFIGURATION

# Common Collector (CC) Configuration

The name itself implies that the **Collector** terminal is taken as common terminal for both input and output of the transistor. The common collector connection for both NPN and PNP transistors is as shown in the following figure.

# Common Collector Connection $R_{C} = V_{EC}$ Signal $V_{BC}$ Signal $V_{BC}$ Signal $V_{BC}$

Using NPN transistor

Using PNP transistor

Just as in CB and CE configurations, the emitter junction is forward biased and the collector junction is reverse biased. The flow of electrons is controlled in the same manner. The input current is the base current  $I_B$  and the output current is the emitter current  $I_E$  here.

# **Current Amplification Factor (γ)**

The ratio of change in emitter current ( $\Delta IE\Delta IE$ ) to the change in base current ( $\Delta IB\Delta IB$ ) is known as **Current Amplification factor**in common collector (CC) configuration. It is denoted by  $\gamma$ .

$$\gamma = \frac{\Delta I_E}{\Delta I_R}$$

- The current gain in CC configuration is same as in CE configuration.

- The voltage gain in CC configuration is always less than 1.

Relation between  $\gamma$  and  $\alpha$

Let us try to draw some relation between  $\gamma$  and  $\alpha$

$$egin{aligned} \gamma &= rac{\Delta I_E}{\Delta I_B} \ & lpha &= rac{\Delta I_C}{\Delta I_E} \ & I_E &= I_B \, + \, I_C \ & \Delta I_E &= \Delta I_B \, + \, \Delta I_C \ & \Delta I_B &= \Delta I_E \, - \, \Delta I_C \end{aligned}$$

Substituting the value of IB, we get

$$\gamma = rac{\Delta I_E}{\Delta I_E - \Delta I_C}$$

Dividing by ΔIE

$$\gamma = rac{rac{\Delta I_E}{\Delta I_E}}{rac{\Delta I_E}{\Delta I_E} - rac{\Delta I_C}{\Delta I_E}} \ rac{1}{1-lpha} \ \gamma = rac{1}{1-lpha}$$

# Expression for collector current

We know

$$I_C = lpha I_E + I_{CBO}$$

$I_E = I_B + I_C = I_B + (lpha I_E + I_{CBO})$

$I_E (1-lpha) = I_B + I_{CBO}$

$I_E = rac{I_B}{1-lpha} + rac{I_{CBO}}{1-lpha}$

$I_C \cong I_E = (eta+1)I_B + (eta+1)I_{CBO}$

The above is the expression for collector current.

#### Characteristics of CC Configuration

- This configuration provides current gain but no voltage gain.

- In CC configuration, the input resistance is high and the output resistance is low.

- The voltage gain provided by this circuit is less than 1.

- The sum of collector current and base current equals emitter current.

- The input and output signals are in phase.

- This configuration works as non-inverting amplifier output.

- This circuit is mostly used for impedance matching. That means, to drive a low impedance load from a high impedance source.

Fig 2.11 Output Characteristics of CC Configuration for npn Transistor

### **UNIT III**

### FIELD EFFECT TRANSISTOR

#### **INTRODUCTION**

- 1. The Field effect transistor is abbreviated as FET, it is an another semiconductor device like a BJT which can be used as an amplifier or switch.

- 2. The Field effect transistor is a voltage operated device. Whereas Bipolar junction transistor is a current controlled device. Unlike BJT a FET requires virtually no input current.

- 3. This gives it an extremely high input resistance, which is its most important advantage over a bipolar transistor.

- 4. FET is also a three terminal device, labeled as source, drain and gate.

- 5. The source can be viewed as BJT's emitter, the drain as collector, and the gate as the counter part of the base.

- The material that connects the source to drain is referred to as the channel.

- 7. FET operation depends only on the flow of majority carriers ,therefore they are called uni polar devices. BJT operation depends on both minority and majority carriers.

- 8. As FET has conduction through only majority carriers it is less noisy than BJT.

- 9. FETs are much easier to fabricate and are particularly suitable for ICs because they occupy less space than BJTs.

- 10. FET amplifiers have low gain bandwidth product due to the junction capacitive effects and produce more signal distortion except for small signal operation.

- 11. The performance of FET is relatively unaffected by ambient temperature changes. As it has a negative temperature coefficient at high current levels, it prevents the FET from thermal breakdown. The BJT has a positive temperature coefficient at high current levels which leads to thermal breakdown.

### **CLASSIFICATION OF FET:**

There are two major categories of field effect transistors:

- 1. Junction Field Effect Transistors

- 2. MOSFETs

These are further sub divided in to P- channel and N-channel devices.

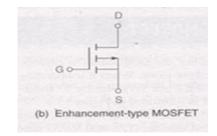

MOSFETs are further classified in to two types Depletion MOSFETs and Enhancement.

### **MOSFETs**

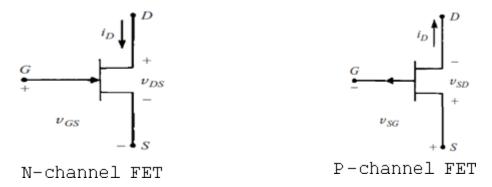

The schematic symbols for the P-channel and N-channel JFETs are shown in the figure.

Fig 4.1 schematic symbols for the P-channel and N-channel JFET

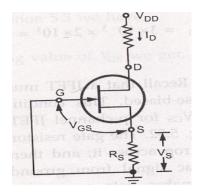

### CONSTRUCTION AND OPERATION OF N- CHANNEL FET

If the gate is an N-type material, the channel must be a P-type material.

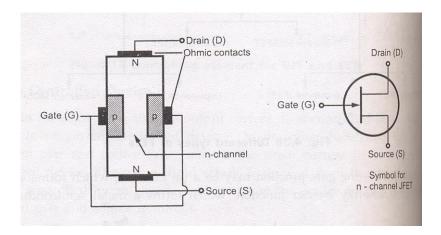

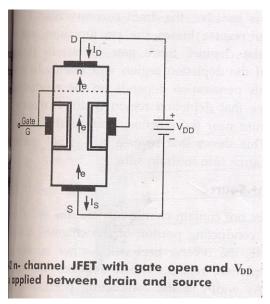

### **CONSTRUCTION OF N-CHANNEL JFET**

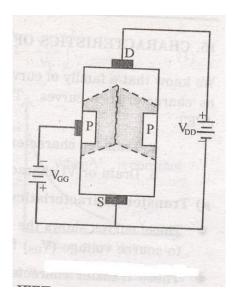

Fig 4.2 Construction of N-Channel JFET

A piece of N- type material, referred to as channel has two smaller pieces of P-type material attached to its sides, forming PN junctions. The channel ends are designated as the drain and source. And the two pieces of P-type material are connected together and their terminal is called the gate. Since this channel is in the N-type bar, the FET is known as N-channel JFET.

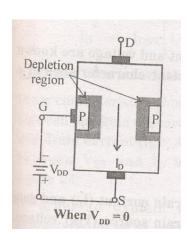

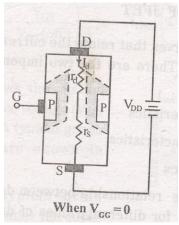

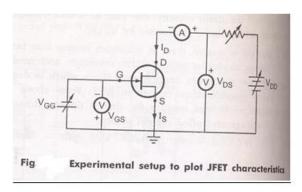

#### **OPERATION OF N-CHANNEL JFET:-**

The overall operation of the JFET is based on varying the width of the channel to control the drain current.